|      |   |   |

|------|---|---|

| 2003 | - | 5 |

| 2004 | - | 6 |

| 2005 | - | 6 |

| 2006 | - | 5 |

| 2007 | - | 6 |

| 2008 | - | 6 |

| 2009 | - | 6 |

| 2010 | - | 2 |

| 2011 | - | 6 |

| 2012 | - | 5 |

| 2013 | - | 3 |

| 2014 | - | 5 |

| 2015 | - | 1 |

| 2016 | - |   |

| 2017 | - |   |

| 2018 | - |   |

| 2019 | - |   |

62

# Vorlesungsprüfung aus Digitales Design

11. März 2003

---

Die Arbeitszeit beträgt 2 Stunden. Als Hilfsmittel sind ausnahmslos Schreibzeug, Lineal und (nicht programmierbarer) Taschenrechner erlaubt. Schreiben Sie Ihre Antworten und Lösungen (incl. Lösungsweg!) mit dokumentechten Stiften (Füllfeder, Kugelschreiber, KEIN Bleistift!) und streichen Sie alles durch, was nicht zur Beurteilung herangezogen werden soll. Ein Abbruch der Prüfung nach Erhalt der Angaben führt in jedem Fall zu einer Beurteilung.

Tragen Sie Namen, Kennzahl und Matrikelnummer **zu Beginn** der Prüfung in die Tabelle ein und beschriften Sie jedes Blatt, das Sie abgeben möchten rechts oben mit Namen und Matrikelnummer.

|               |                 |

|---------------|-----------------|

| Familienname: | Vorname:        |

| Kennzahl:     | Matrikelnummer: |

Viel Erfolg!

**Die nachfolgende Tabelle nicht beschriften!**

| Beispiel       | Mögliche Punkte | Erhaltene Punkte |

|----------------|-----------------|------------------|

| Theoriefragen  | 50              |                  |

| Rechenbeispiel | 1               | 10               |

|                | 2               | 15               |

|                | 3               | 15               |

|                | 4               | 10               |

| Gesamt         | 100             |                  |

## Theoriefragen

**Frage 1:**

Was ist eine Sign-off Simulation?

**Frage 2:**

Welche Strecke legt eine elektromagnetische Welle auf einer Leitung innerhalb von 1ns zurück?

**Frage 3:**

Handelt es sich bei einem ROM um rein kombinatorische oder sequentielle Logik? Begründen Sie!

**Frage 4:**

Wodurch unterscheidet sich im Aufbau ein Tri-State-Ausgang von einem open-Drain-Ausgang?

**Frage 5:**

Was besagt das Moore'sche Gesetz

**Frage 6:**

Was ist ein IP-Core?

**Frage 7:**

Warum verursacht ein Scan-Test einen Overhead in der Chipfläche?

**Frage 8:**

Altert ein Chip auch wenn er nicht in Betrieb ist? Begründen Sie!

**Frage 9:**

Nennen Sie zwei Maßnahmen um die Wahrscheinlichkeit für Upsets infolge von Metastabilität zu vermeiden!

**Frage 10:**

Warum werden bei CMOS-Logik die Funktionen NAND und NOR bevorzugt verwendet und nur selten AND und OR?

## Rechenbeispiele

### Beispiel 1

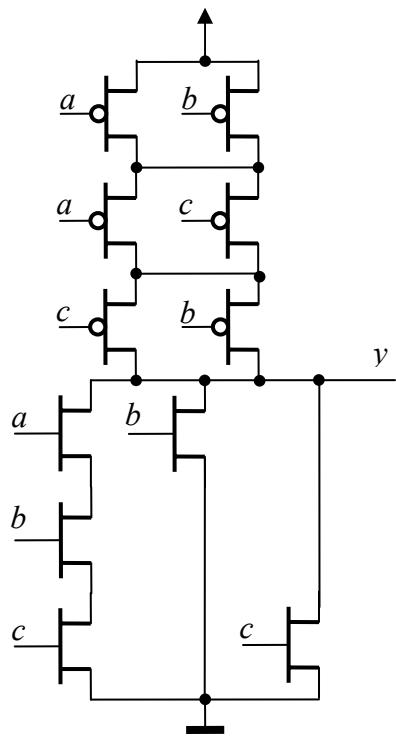

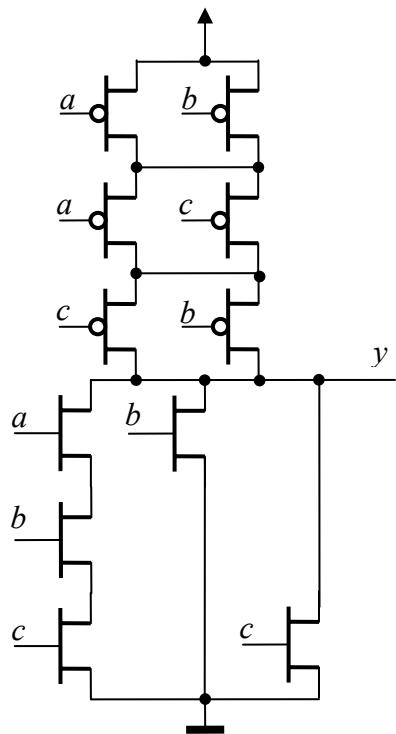

Die folgende Funktion ist in Hardware zu realisieren:

$$Y = (\neg A \vee \neg B) \wedge \neg C$$

- (a) Geben Sie die Wahrheitstabelle und das KV-Diagramm für diese Funktion an!

- (b) Wenn Sie die Wahl zwischen einer Realisierung als AOI oder als OAI haben, was würden Sie bevorzugen? Begründen Sie!

- (c) Entwerfen Sie zunächst den n-Stack für Ihre bevorzugte Lösung!

- (d) Entwerfen Sie weiters den dazugehörigen p-Stack!

- (e) Stellen Sie die Realisierung der Gesamtlösung mittels FETs dar (Schaltbild)!

### Beispiel 2

Gegeben sind zwei Variable A und B mit 2 Bit Wortbreite, d.h.  $A = (a_1, a_0)$ ,  $B = (b_1, b_0)$ . Gesucht ist die Realisierung einer Funktion, die genau dann „1“ ausgibt, wenn  $A > B$ . A und B sind binär codierte positive Integer-Werte, es gilt also  $(0,0) < (0,1) < (1,0) < (1,1)$ .

- (a) Skizzieren Sie, wie Sie diese Funktion mittels eines ROM implementieren würden:

- Wie viele Adressleitungen benötigen Sie?

- Welche Signale schließen sie daran an?

- Welche Speichergröße benötigen Sie?

- Geben Sie zu jeder ROM-Adresse den zugehörigen Speicherinhalt an!

- (b) Skizzieren Sie, wie Sie diese Funktion mittels einer PAL-Struktur implementieren würden:

- Wie viele p-Terms benötigen Sie?

- Kennzeichnen Sie in Ihrer Skizze alle Verbindungen die programmiert werden müssen mit „O“

### Beispiel 3

An einem Chip messen Sie bei einer Versorgungsspannung von  $V_{DD}=3,3V$  einen mittleren Strom von 3A. Im Datenblatt finden Sie für das Gehäuse folgende Angabe:

$$\theta_{JC} = 2\text{K/W}$$

$\theta_{JA} = 5\text{K/W}$  für Betrieb ohne Kühlkörper.

- (a) Welche Temperatur  $T_J$  erreicht der Die im Betrieb bei  $T_{AMB}=25^\circ\text{C}$ ?

- (b) Angenommen Sie erhöhen für einen Burn-in dieses Chips die Versorgungsspannung auf  $V_{DD} = 4,0\text{V}$ . Welche Temperatur  $T_J$  erreicht der Die nun?

(Nehmen Sie an, die Verlustleistung sei durch Ladeströme dominiert)

- (c) Bestimmen Sie Temperature Acceleration Factor  $AF_T$  und Voltage Acceleration Factor  $AF_V$  für den Betrieb bei  $V_{DD} = 4,0\text{V}$  und  $T_{AMB} = 25^\circ\text{C}$  gegenüber einem Normalbetrieb bei  $V_{DD} = 3,3\text{V}$  und  $T_{AMB} = 25^\circ\text{C}$ !

$k = 8,6 \cdot 10^{-5} \text{eV/K}$  ;  $E_{act} = 0,7 \text{eV}$  ;  $\gamma = 3,2 \text{V}^{-1}$

- (d) Angenommen, Sie wollen erreichen, dass der Chip beim Burn-in innerhalb von 24 Stunden um 1 Jahr altert (als Normalbetrieb gilt wieder  $T_{AMB} = 25^\circ\text{C}$ ;  $V_{DD} = 3,3\text{V}$ ). Welchen Acceleration Factor  $AF$  benötigen Sie insgesamt?

Welcher Temperature Acceleration Factor  $AF_T$  ist nun erforderlich ( $V_{DD}$  ist weiterhin 4,0V)?

Bei welcher Die-Temperatur  $T_J$  und welcher Umgebungstemperatur  $T_{AMB}$  muss man den Chip dafür betreiben? Ist das technisch machbar?

## Beispiel 4

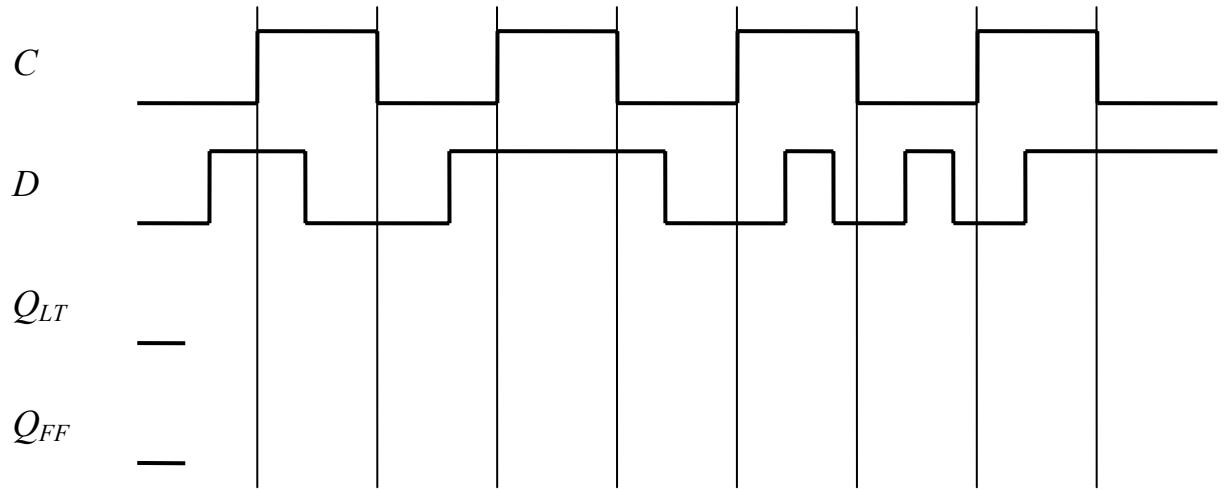

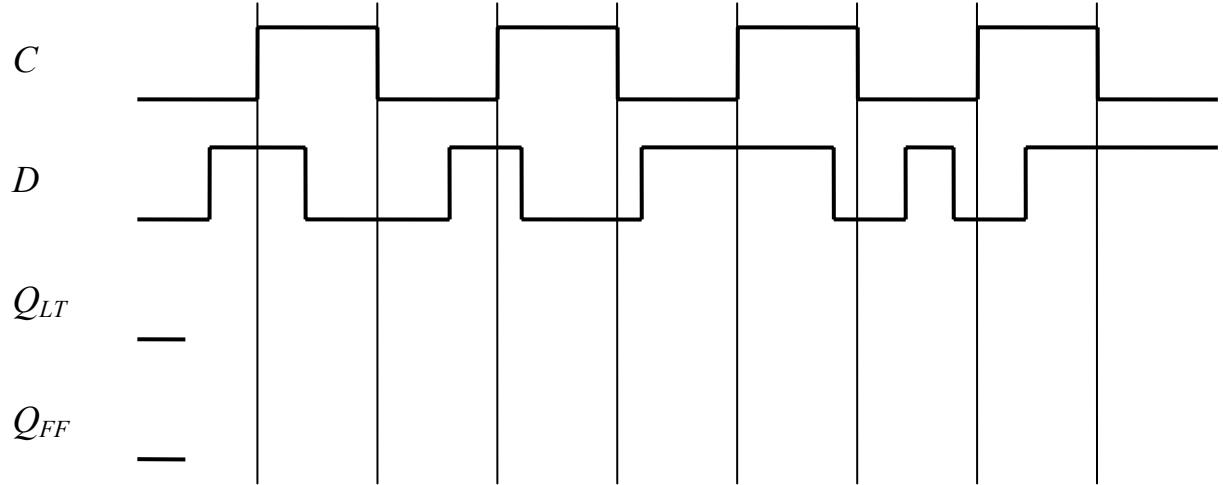

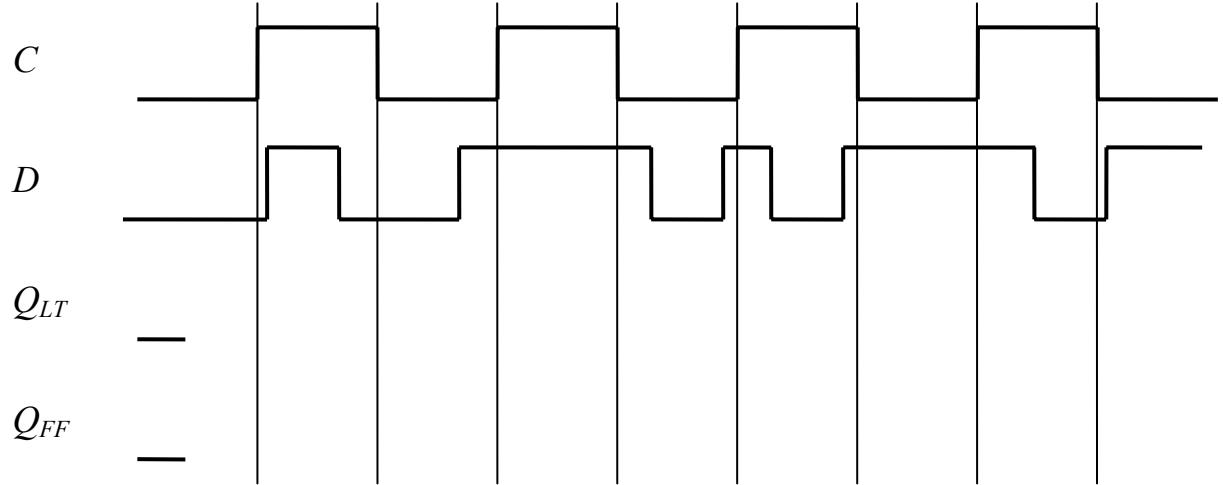

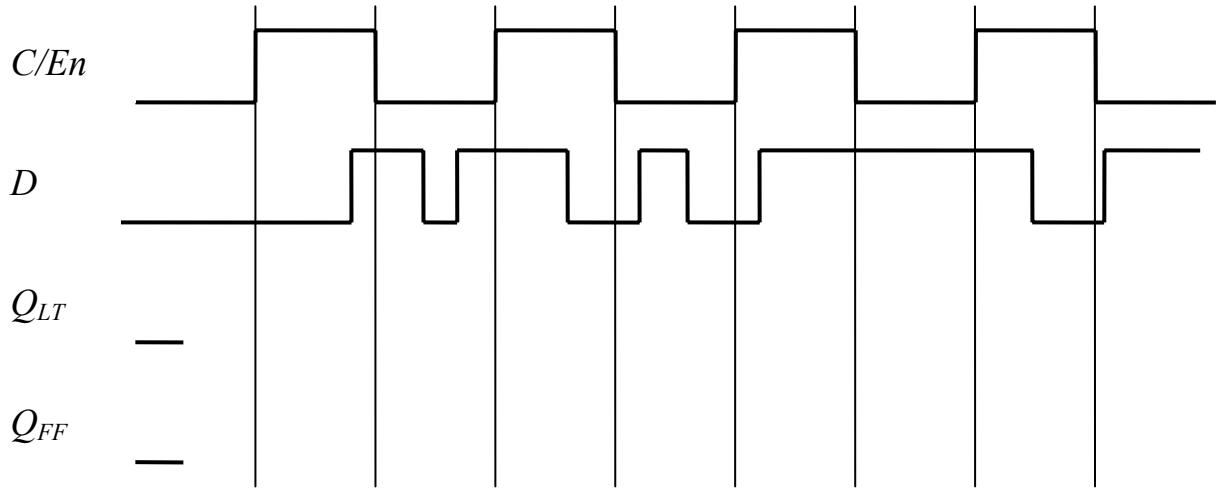

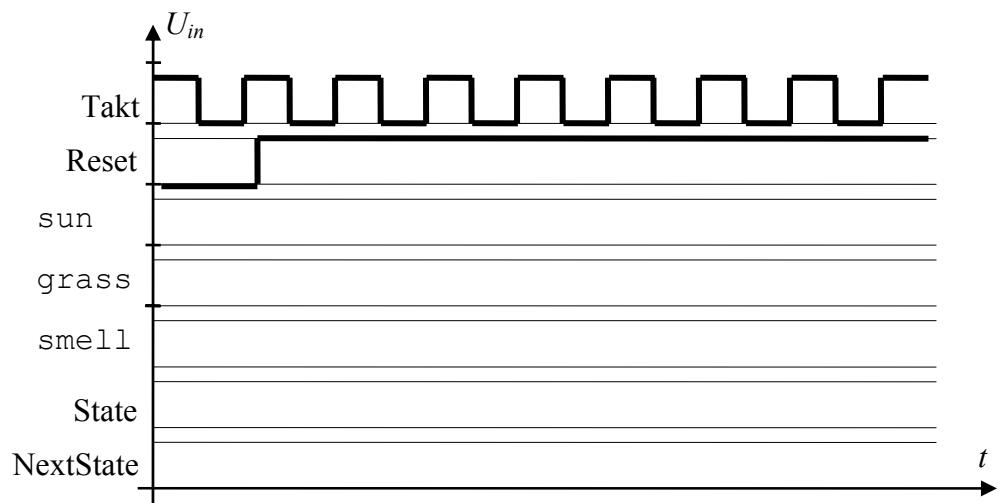

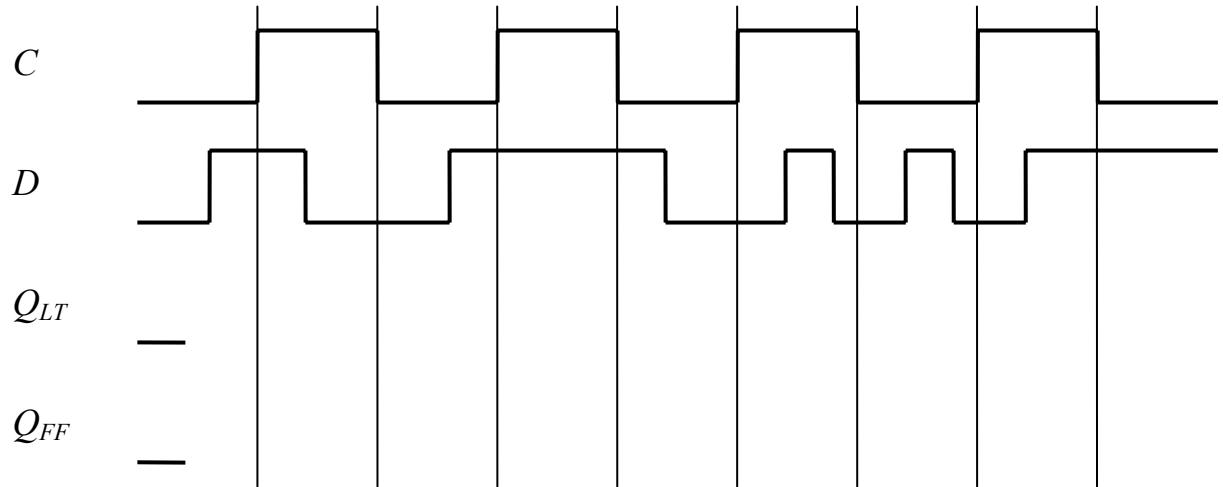

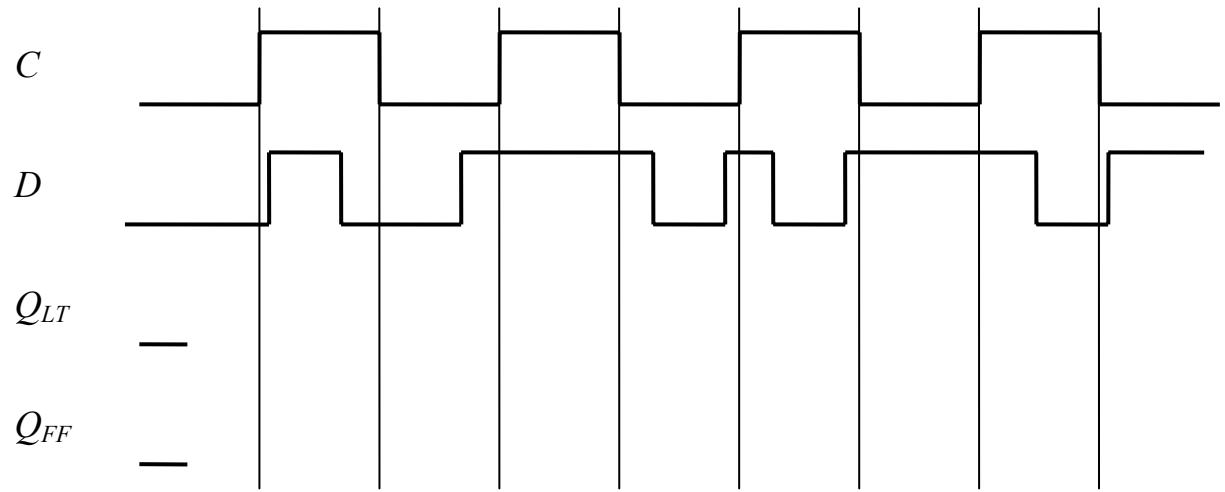

Gegeben sind die in Abbildung 1 dargestellten Signalverläufe für ein Datensignal  $D$  und ein Clock-Signal bzw. Enable-Signal  $C$ .

- (a) Tragen Sie in die Zeile  $Q_{LT}$  das zugehörige Ausgangssignal Q eines D-Latch ein! („0“ = „Hold“)

- (b) Tragen Sie in die Zeile  $Q_{FF}$  das zugehörige Ausgangssignal Q eines D-Flip-Flop ein! (steigende Flanke ist aktiv)

- (c) Beschreibt der folgende VHDL-Code ein D-Flip-Flop, ein D-Latch oder keines von beiden? Begründen Sie!

```

Architecture BEISPIEL_3 of PRÜFUNG is

begin

signal CLK, DATA, NEXT, OUT : std_logic;

CAPTURE: process (CLK)

begin

if CLK'event and CLK = '1' then

OUT <= NEXT;

else

NEXT <= OUT;      ←

end if;

end process CAPTURE;

NEXT <= DATA;

end BEISPIEL_3;

```

- (d) Wenn Sie den „else“-Zweig (mit Pfeilen markiert) weglassen – was beschreibt der Code dann?

# Vorlesungsprüfung aus Digitales Design

17. November 2003

---

Die Arbeitszeit beträgt 2 Stunden. Als Hilfsmittel sind ausnahmslos Schreibzeug, Lineal und (nicht programmierbarer) Taschenrechner erlaubt. Schreiben Sie Ihre Antworten und Lösungen (incl. Lösungsweg!) mit dokumentechten Stiften (Füllfeder, Kugelschreiber, KEIN Bleistift!) und streichen Sie alles durch, was nicht zur Beurteilung herangezogen werden soll. Ein Abbruch der Prüfung nach Erhalt der Angaben führt in jedem Fall zu einer Beurteilung.

Tragen Sie Namen, Kennzahl und Matrikelnummer **zu Beginn** der Prüfung in die Tabelle ein und beschriften Sie jedes Blatt, das Sie abgeben möchten rechts oben mit Namen und Matrikelnummer.

|               |                 |

|---------------|-----------------|

| Familienname: | Vorname:        |

| Kennzahl:     | Matrikelnummer: |

Viel Erfolg!

**Die nachfolgende Tabelle nicht beschriften!**

| Beispiel       | Mögliche Punkte | Erhaltene Punkte |

|----------------|-----------------|------------------|

| Theoriefragen  | 50              |                  |

| Rechenbeispiel | 1               | 15               |

|                | 2               | 10               |

|                | 3               | 10               |

|                | 4               | 15               |

| Gesamt         | 100             |                  |

## Theoriefragen

**Frage 1:**

Was versteht man unter einem Minterm?

**Frage 2:**

Warum sind Wafer rund?

**Frage 3:**

Wie ist ein Transmission-Gate aufgebaut und wozu wird es verwendet?

**Frage 4:**

Was versteht man im Zusammenhang mit der Simulation unter einem „Delta-Cycle“?

**Frage 5:**

Was ist ein EEPROM?

**Frage 6:**

Wozu verwendet man eine Antifuse?

**Frage 7:**

Was versteht man unter Metastabilität?

**Frage 8:**

Was versteht man unter infant mortality?

**Frage 9:**

Was besagt die „Rule of Ten“?

**Frage 10:**

Welche Werte kann ein Signal bei der Null Convention Logik (NCL) annehmen ?

## Rechenbeispiele

### Beispiel 1

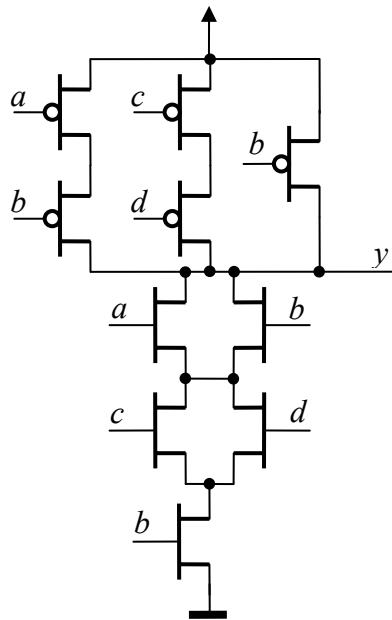

Gegeben ist die folgende Funktion:

$$Y = (\neg A \wedge B) \vee (C \wedge D) \vee (A \wedge \neg B \wedge \neg C)$$

(a) Zeichnen Sie das KV-Diagramm dieser Funktion Y !

(b) Zeigen Sie, wie Sie diese Funktion Y mit einer PAL-Struktur realisieren können:

- Wie viele P-Terme benötigen Sie ?

- Wie viele Programmierelemente weist die Verbindungsmaatrix insgesamt auf ? Wie viele davon werden programmiert (d.h. eine Verbindung wird erstellt) ?

- Zeichnen Sie das Schaltbild !

- Skizzieren Sie, wie man am Ausgang einen programmierbaren Inverter realisieren könnte!

- Wie viele P-Terme würde man bei Verwendung des Inverters benötigen ?

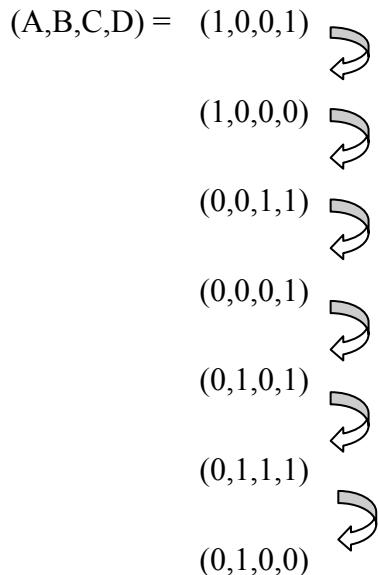

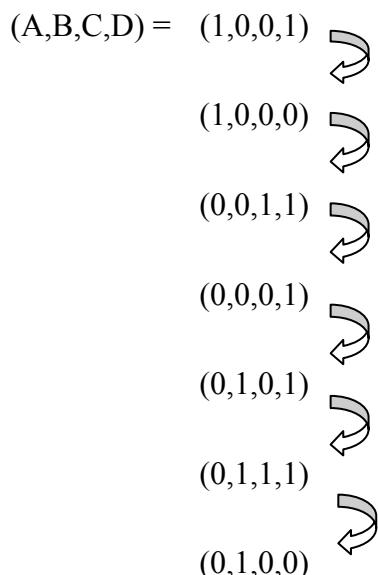

(c) Sie wollen diese Schaltung nun im Fundamental Mode betreiben.

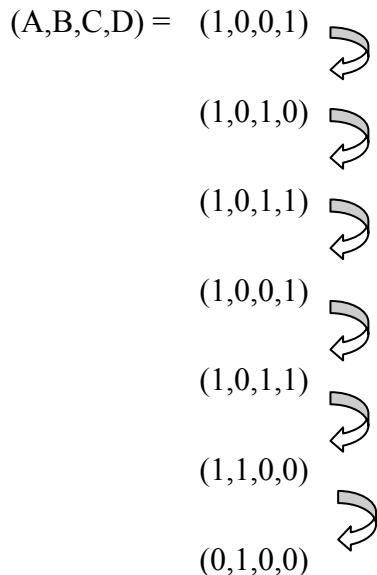

- Kennzeichnen Sie in der folgenden Sequenz jene Übergänge mit „X“, die dabei nicht zulässig sind:

- Kennzeichnen Sie weiters jenen Übergang mit „O“, der zwar im Fundamental Mode zulässig ist, bei dem aber dennoch ein Glitch auftreten könnte! Begründen Sie!

- Welchen P-Term müssten Sie hinzufügen, damit dieser Glitch sicher vermieden werden kann (Huffman Circuit) ?

## Beispiel 2

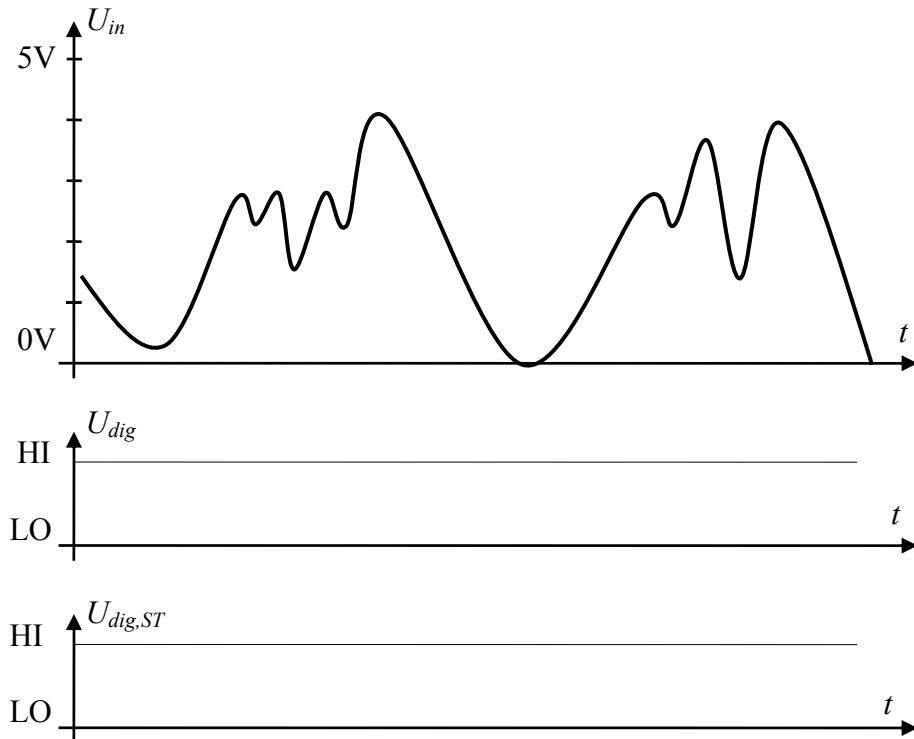

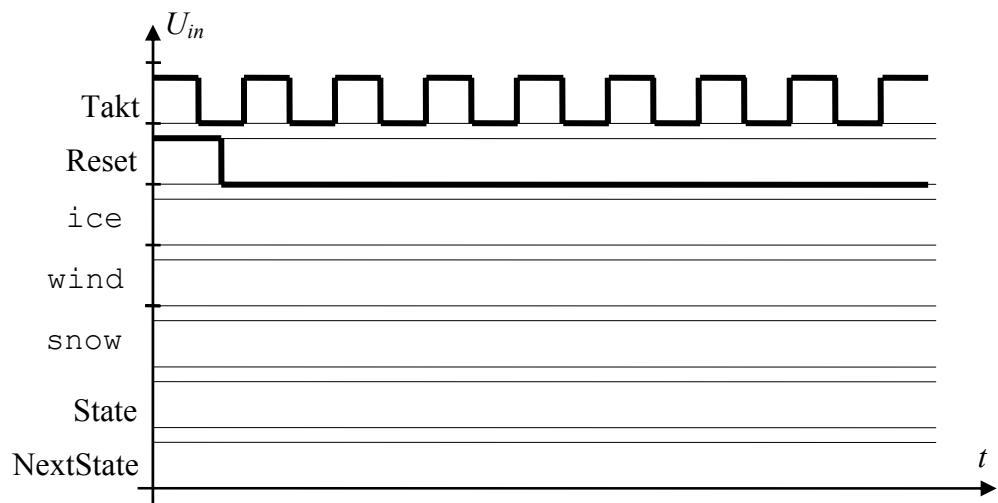

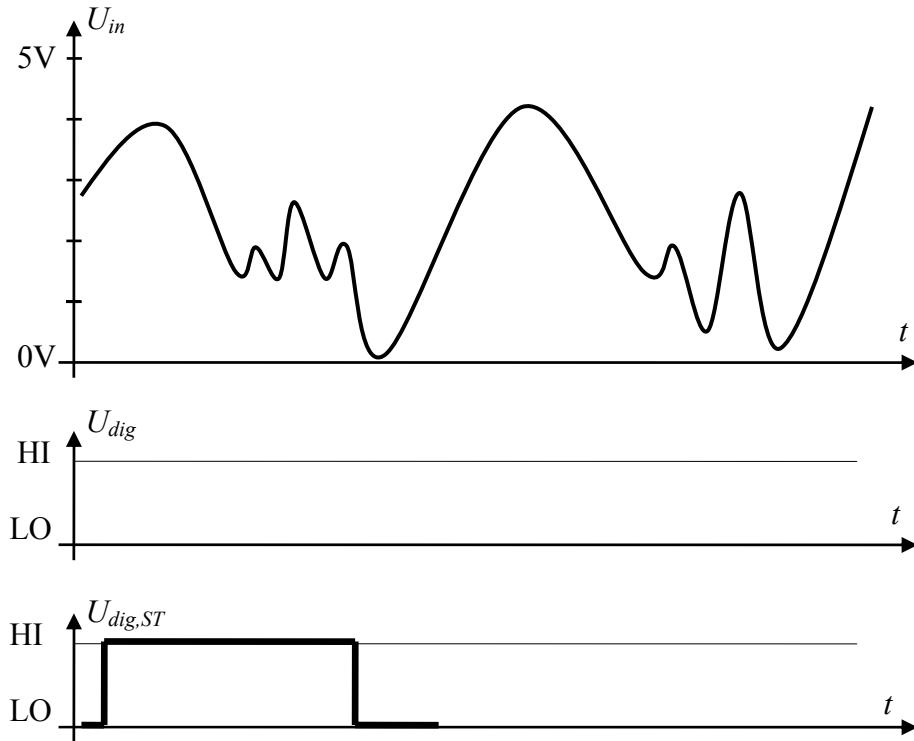

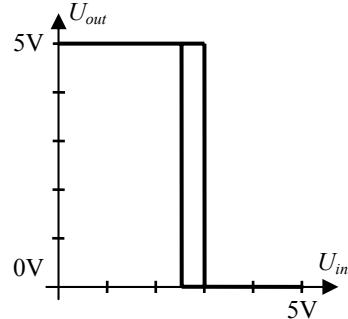

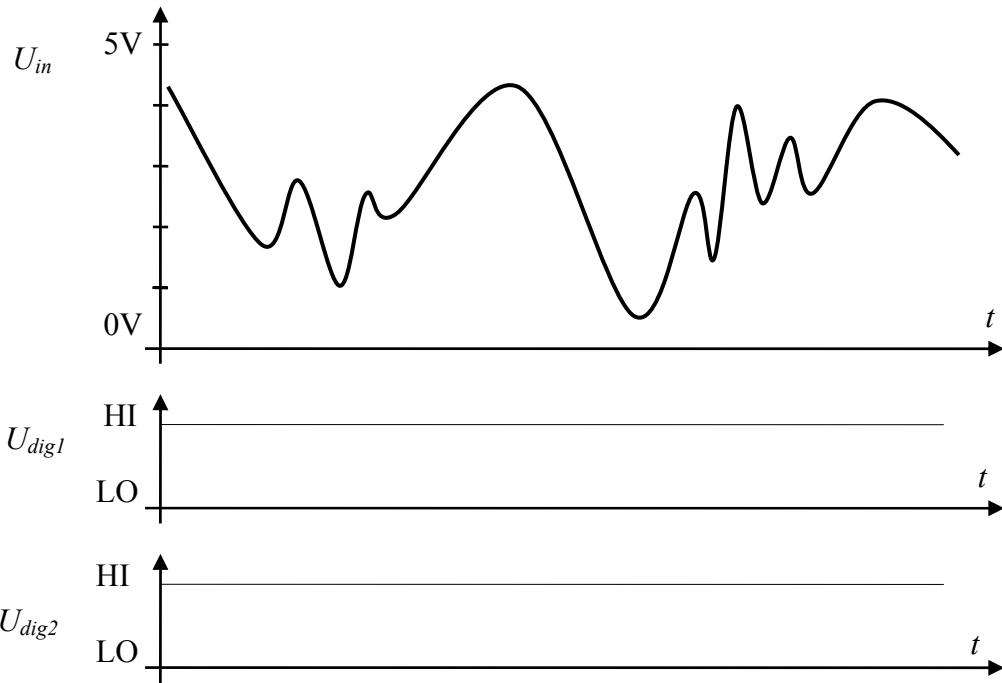

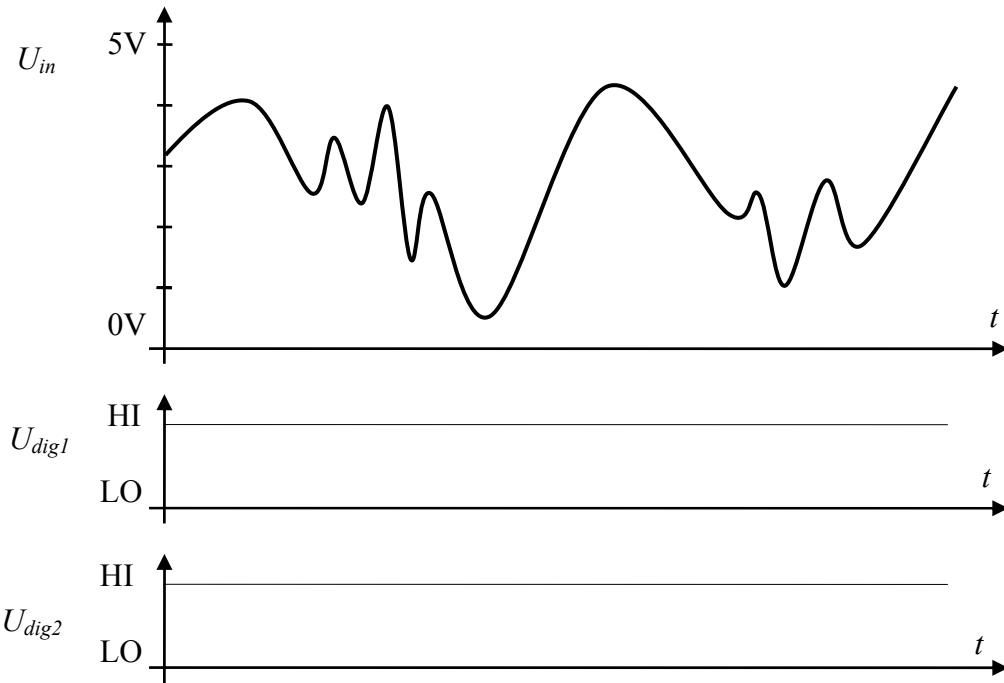

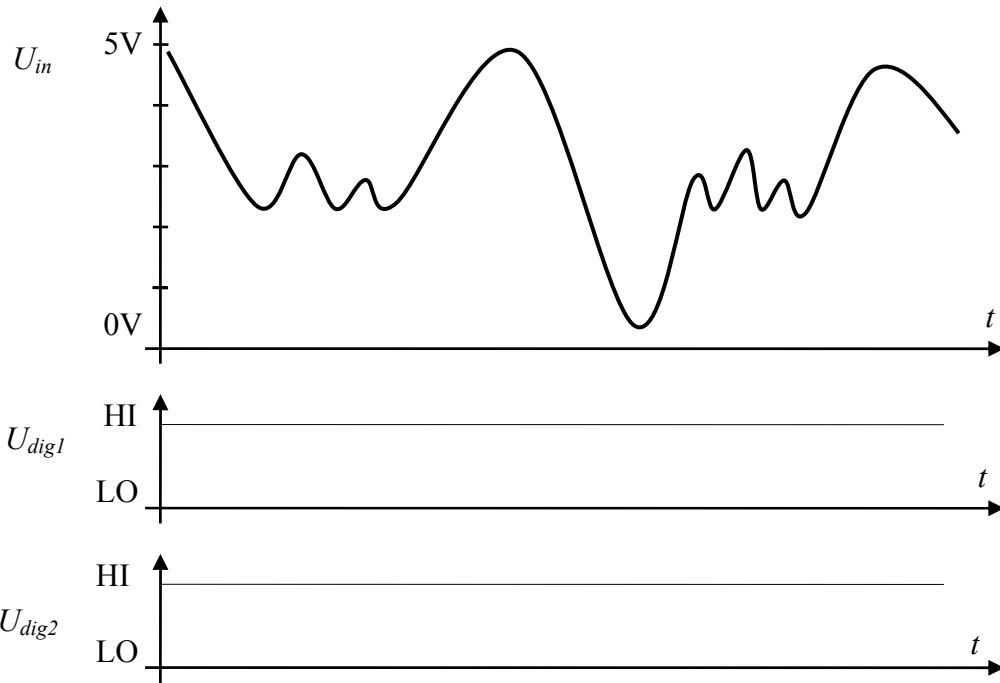

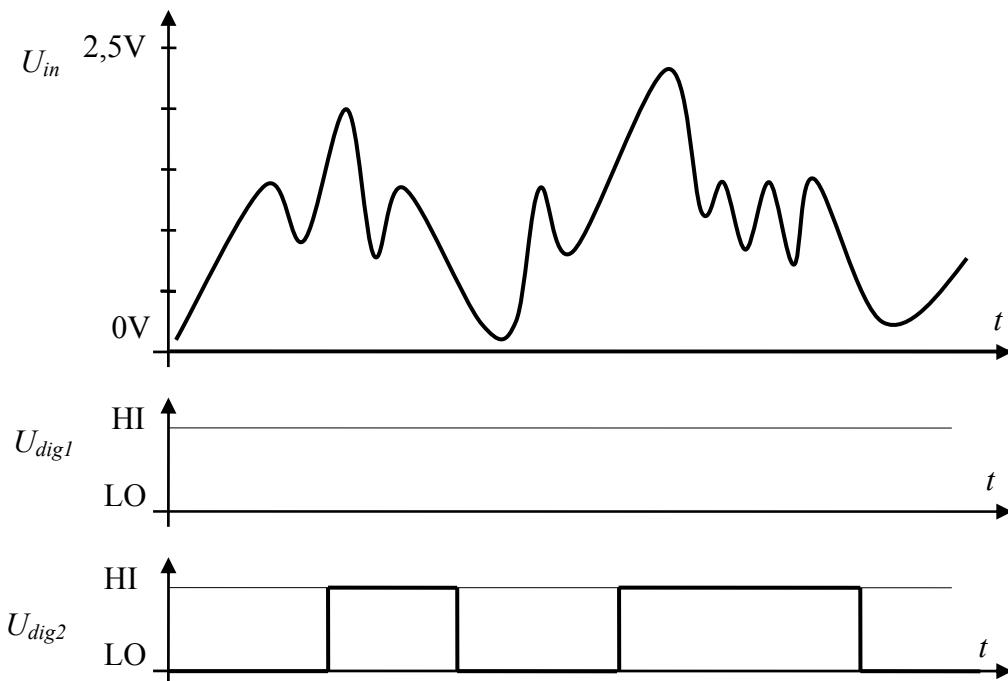

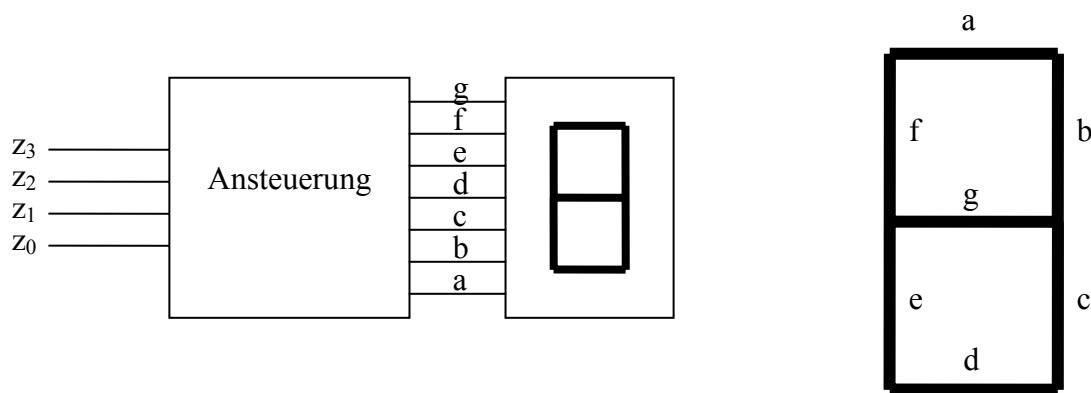

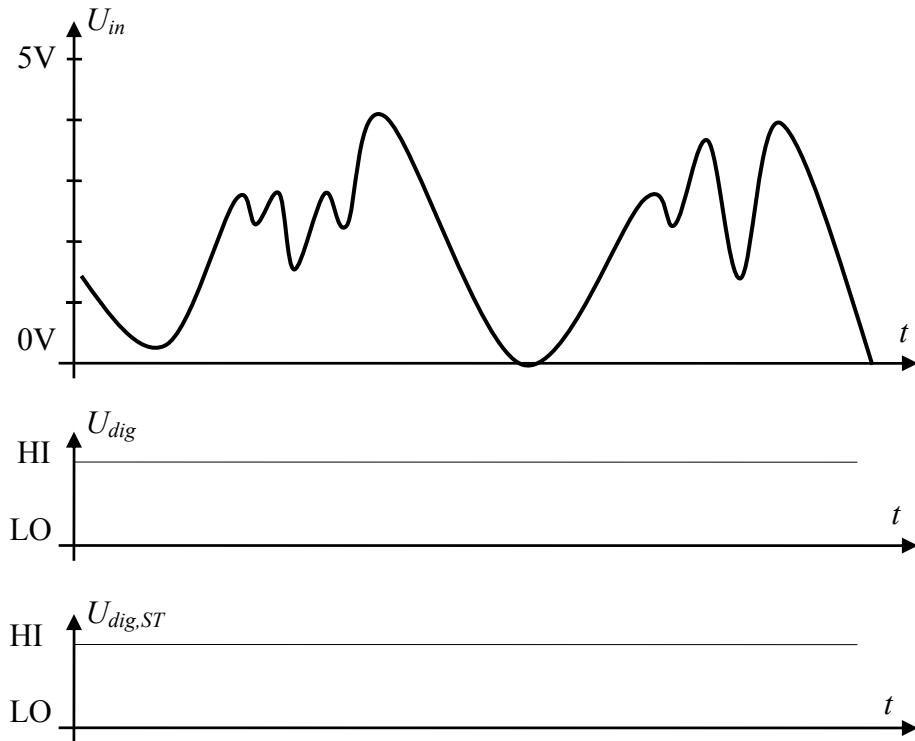

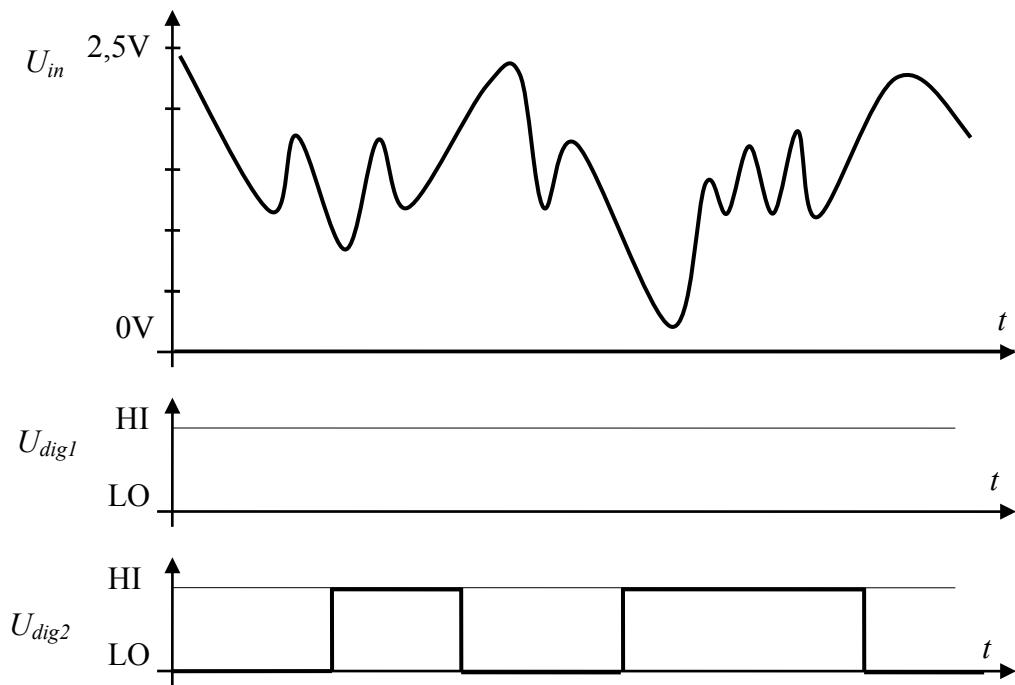

Gegeben ist der Spannungsverlauf  $U_{in}$  in Abbildung 1:

Abbildung 1

- (a) Tragen Sie in die Abbildung den Spannungsverlauf  $U_{dig}$  nach der Digitalisierung dieser Eingangsspannung ein, wenn der Schwellwert fix bei 2,5V liegt.

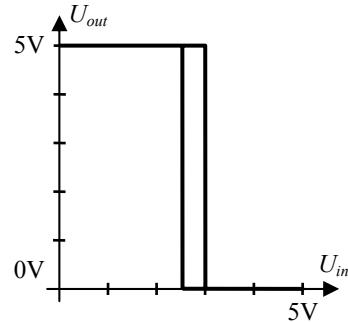

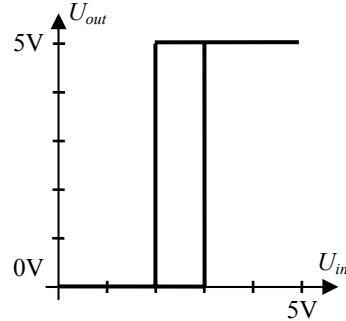

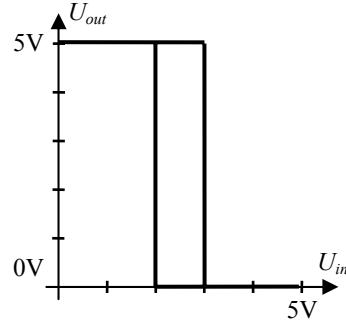

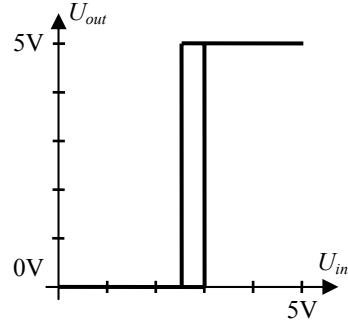

In Abbildung 2 ist die Kennlinie eines Schmitt-Trigger gegeben.

Abbildung 2

- (b) Kennzeichnen Sie durch Pfeile in den vertikalen Abschnitten der Kennlinie die Richtung, in der die Kennlinie durchlaufen wird.

- (c) Wie groß ist die Hysteresis dieses Schmitt-Trigger (incl. Einheit!) ?

- (d) Handelt es sich um einen invertierenden Schmitt-Trigger oder einen nicht-invertierenden? Begründen Sie!

- (e) Wie sieht die Ausgangsspannung  $U_{dig,ST}$  am Ausgang des Schmitt-Trigger aus, wenn Sie die Eingangsspannung nach Abbildung 1 anlegen? Tragen Sie den Verlauf in Abbildung 1 ein!

### Beispiel 3

Ein Chip hat bei einer Versorgungsspannung von  $V_{DD} = 5V$  einen Stromverbrauch von 2A. Bei einer Umgebungstemperatur von  $T_{amb} = 20^\circ C$  erreicht der Die im Betrieb eine Temperatur von  $T_J = 100^\circ C$ . Laut Datenblatt beträgt die MTBF des Chips unter diesen Bedingungen 10 Jahre.  $E_{act} = 0,7\text{eV}$ ;  $k = 8,6 \cdot 10^{-5} \text{ eV/K}$

(a) Wie groß ist die Verlustleistung des Chips unter diesen Bedingungen ?

(b) Wie groß ist der Thermische Widerstand  $T_{JA}$  des Chips (incl. Einheit)?

Aufgrund eines Fehlers in der Dimensionierung der Spannungsversorgung wird der Chip nun mit  $V_{DD} = 6V$  betrieben.

(c) Wie groß ist nun die Verlustleistung?

(Nehmen Sie an, daß die dynamischen Ladeströme dominieren)

(d) Welche Temperatur erreicht der Die nun ?

(e) Welche MTBF ist zu erwarten ?

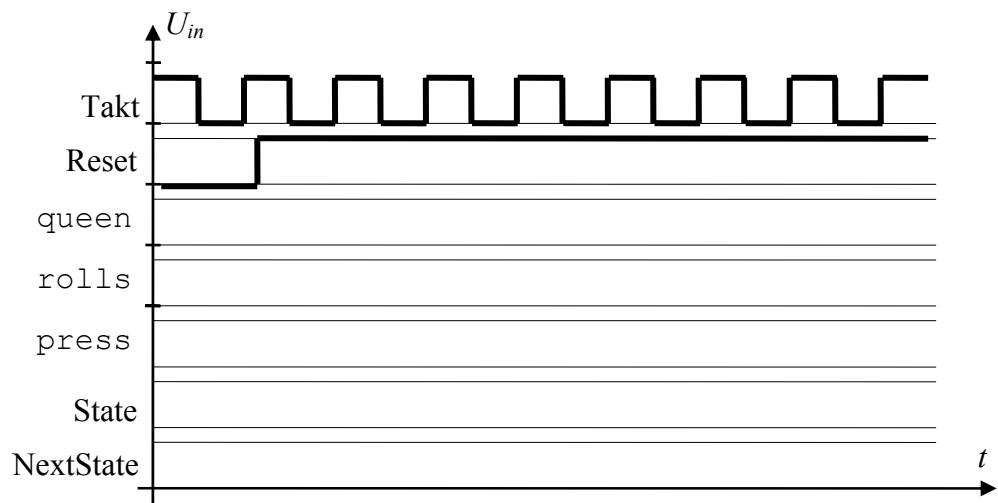

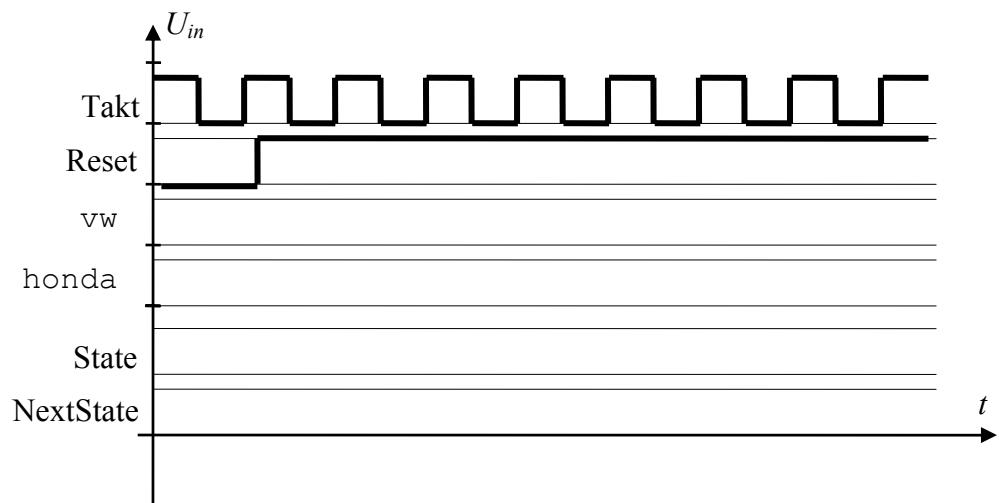

## Beispiel 4

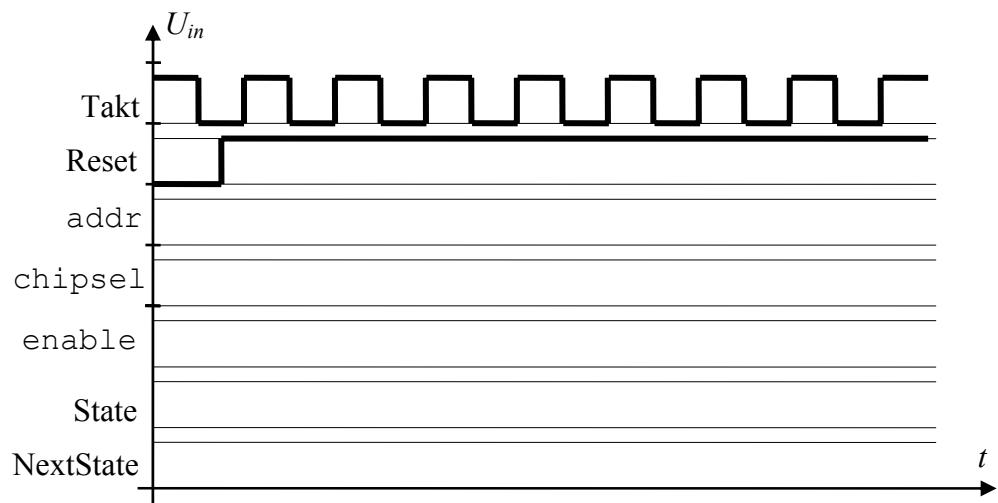

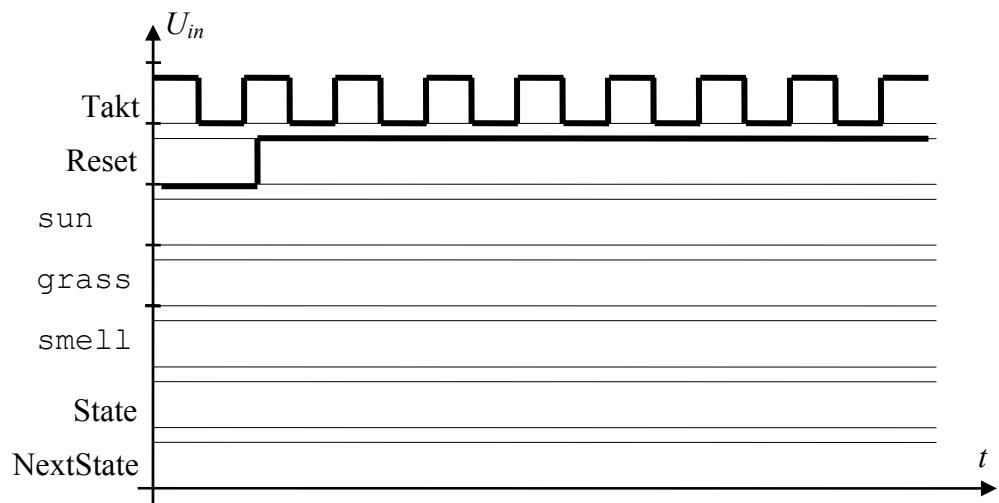

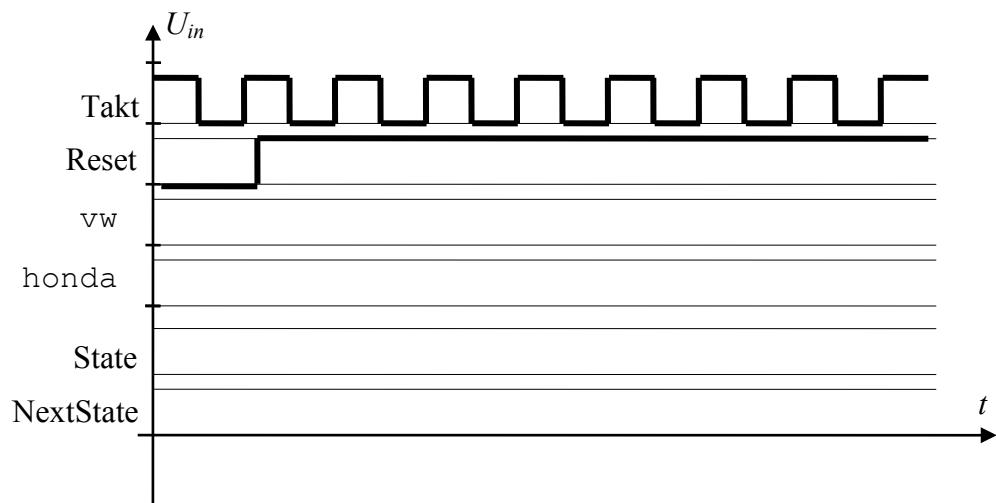

Gegeben ist folgender VHDL-Code einer State-Machine, die die Steuersignale `select`, `enable` und `addr` für einen Zugriff auf ein ROM generiert:

```

library IEEE;

use      IEEE.std_logic_1164.all;

use      IEEE.std_logic_UNSIGNED.all;

entity RAMaccess is

port(

mega  : in std_logic;

energy : in std_logic;

chipsel: out std_logic;

enable : out std_logic;

addr: out std_logic_vector(0 to 3)

);

end RAMaccess;

```

```

architecture making of RAMaccess is

signal cat, dog:

std_logic_vector(0 to 1);

begin

kirk: process(cat)

begin

case cat is

when "00"  => dog <= "01";

when "01"  => dog <= "10";

when "10"  => dog <= "11";

when others => dog <= "00";

end case;

end process kirk;

spock: process(mega, energy)

begin

if energy = '0' then

cat <= "00";

else

if mega'event and mega = '0' then

cat <= dog;

end if;

end if;

end process spock;

scotty: process(cat)

variable bee: std_logic_vector(0 to 3);

begin

if energy = '0' then

bee := "0000";

end if;

case cat is

when "00"  => chipsel <= '1';

enable <= '1';

when "01"  => chipsel <= '0';

bee := bee + '1';

enable <= '1';

when others => chipsel <= '0';

enable <= '0';

end case;

addr <= bee;

end process scotty;

end making;

```

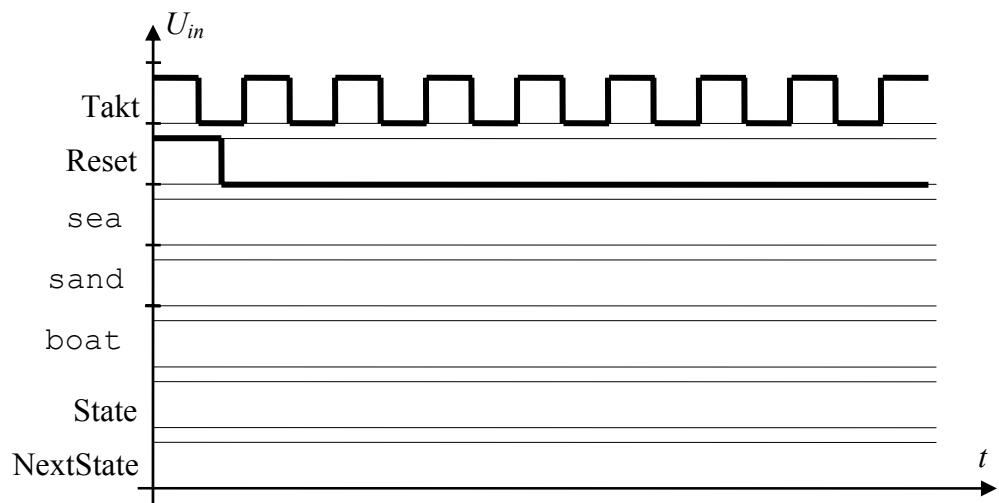

(a) Identifizieren Sie Taktsignal und Reset!

(b) Handelt es sich um einen synchronen oder einen asynchronen Reset? Begründen Sie!

(c) Welches ist die aktive Taktflanke (steigend oder fallend)? Begründen Sie!

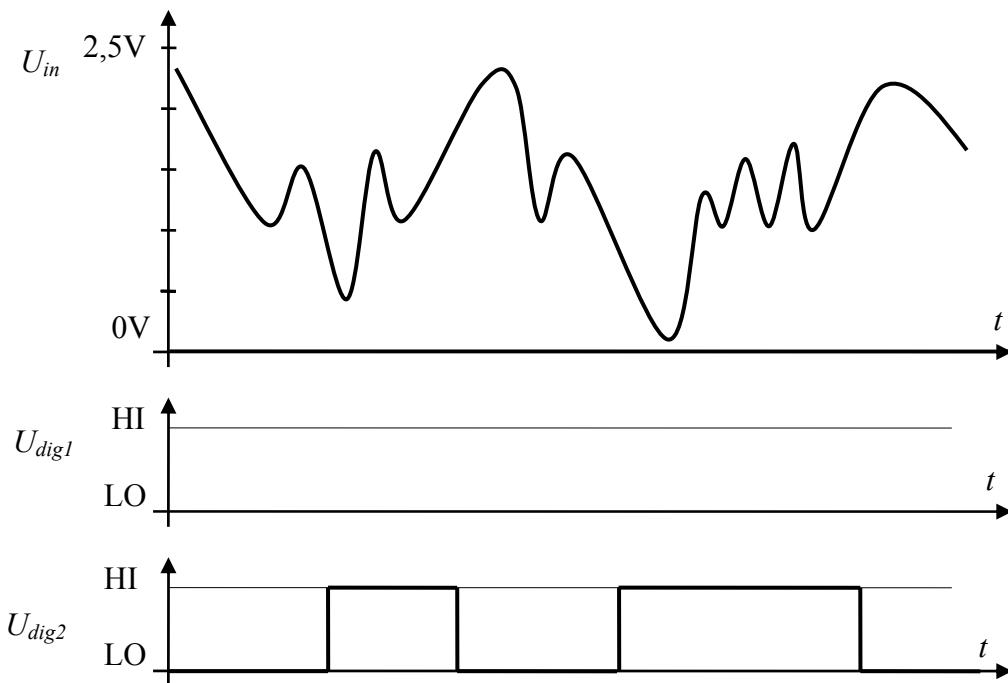

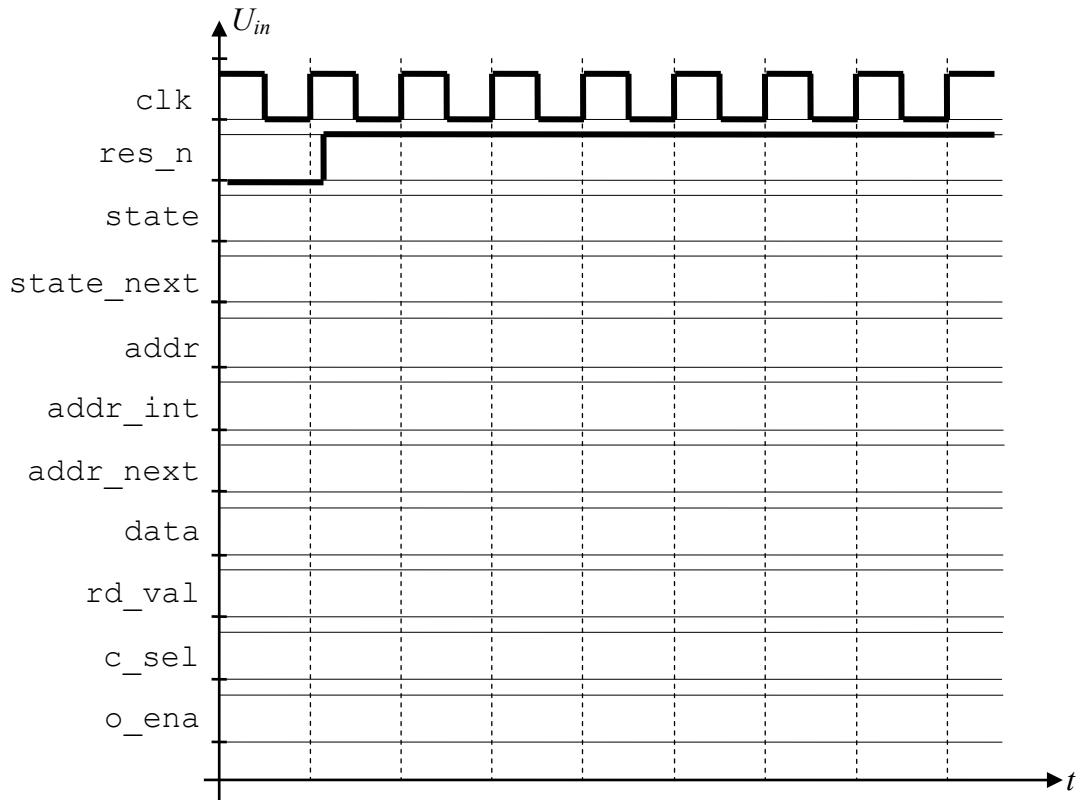

(d) Tragen Sie den Zeitverlauf von `chipsel`, `enable` und `addr` in Abbildung 3 ein!

Abbildung 3

# Vorlesungsprüfung aus Digitales Design

22. Oktober 2003

---

Die Arbeitszeit beträgt 2 Stunden. Als Hilfsmittel sind ausnahmslos Schreibzeug, Lineal und (nicht programmierbarer) Taschenrechner erlaubt. Schreiben Sie Ihre Antworten und Lösungen (incl. Lösungsweg!) mit dokumentechten Stiften (Füllfeder, Kugelschreiber, KEIN Bleistift!) und streichen Sie alles durch, was nicht zur Beurteilung herangezogen werden soll. Ein Abbruch der Prüfung nach Erhalt der Angaben führt in jedem Fall zu einer Beurteilung.

Tragen Sie Namen, Kennzahl und Matrikelnummer **zu Beginn** der Prüfung in die Tabelle ein und beschriften Sie jedes Blatt, das Sie abgeben möchten rechts oben mit Namen und Matrikelnummer.

|               |                 |

|---------------|-----------------|

| Familienname: | Vorname:        |

| Kennzahl:     | Matrikelnummer: |

Viel Erfolg!

**Die nachfolgende Tabelle nicht beschriften!**

| Beispiel       | Mögliche Punkte | Erhaltene Punkte |

|----------------|-----------------|------------------|

| Theoriefragen  | 50              |                  |

| Rechenbeispiel | 1               | 15               |

|                | 2               | 10               |

|                | 3               | 10               |

|                | 4               | 15               |

| Gesamt         | 100             |                  |

## Theoriefragen

**Frage 1:**

Skizzieren Sie die Prinzipschaltung eines Latch!

**Frage 2:**

Warum eignet sich Silizium besonders gut für die Herstellung integrierter Schaltungen?

**Frage 3:**

Was ist der Vorteil von BiCMOS-Logik?

**Frage 4:**

Was ist der Unterschied zwischen Floorplanning und Partitionierung?

**Frage 5:**

Was ist ein OTP-ROM?

**Frage 6:**

Wie werden beim Gate-Array mittels lauter gleicher Zellen unterschiedliche Funktionen realisiert?

**Frage 7:**

Nennen Sie drei Faktoren, von denen der thermische Widerstand eines Gehäuses abhängt!

**Frage 8:**

Wovon hängt das Ausmaß der Electromigration ab?

**Frage 9:**

Warum wendet man beim BIST das Prinzip des nondeterministic Testing an?

**Frage 10:**

Was versteht man unter einem „Hazard“?

## Rechenbeispiele

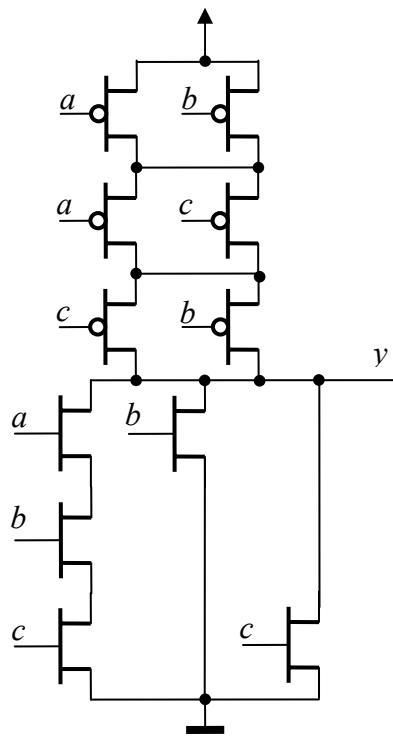

### Beispiel 1

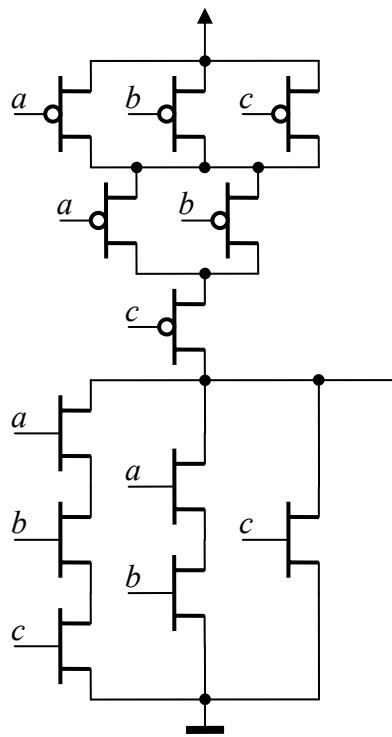

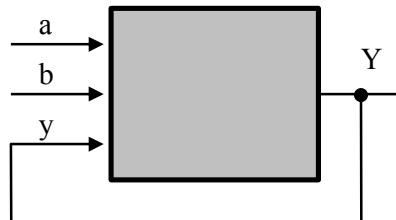

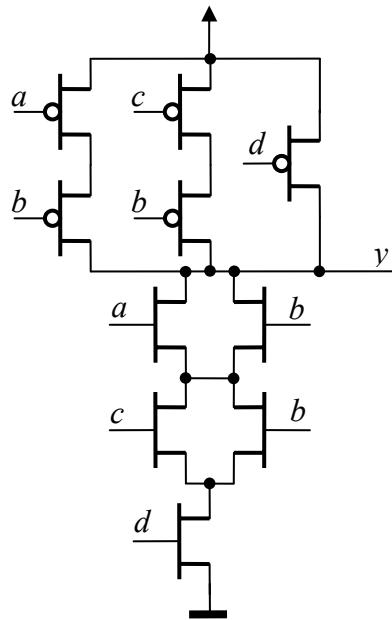

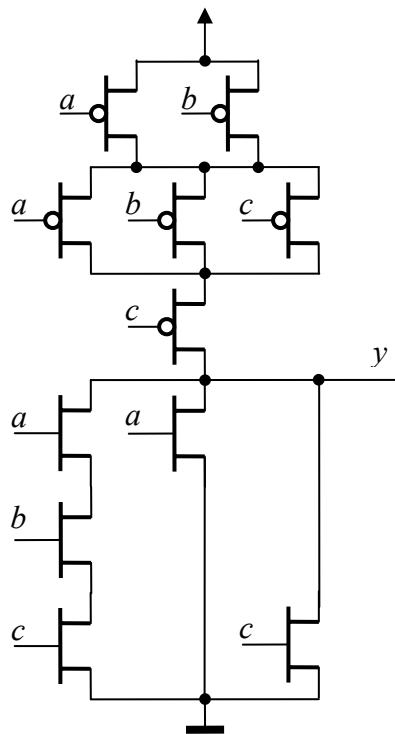

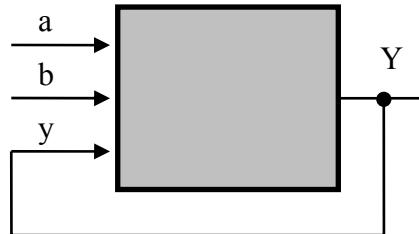

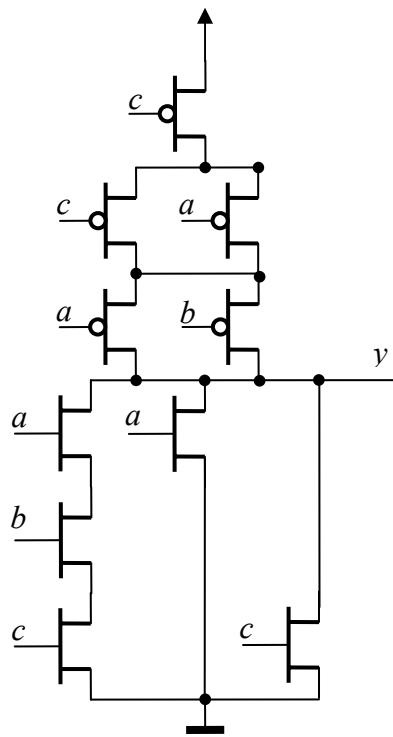

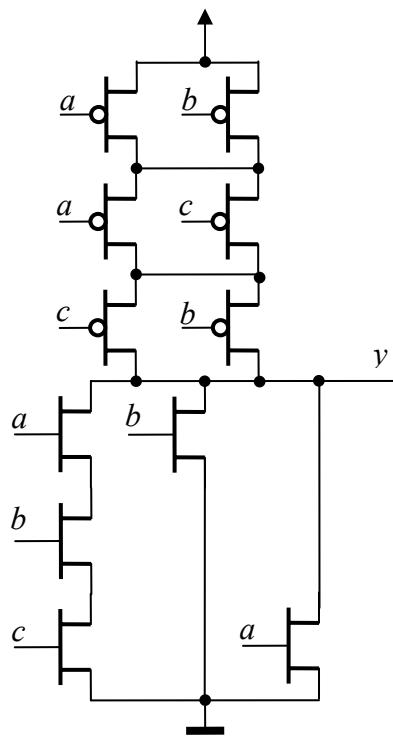

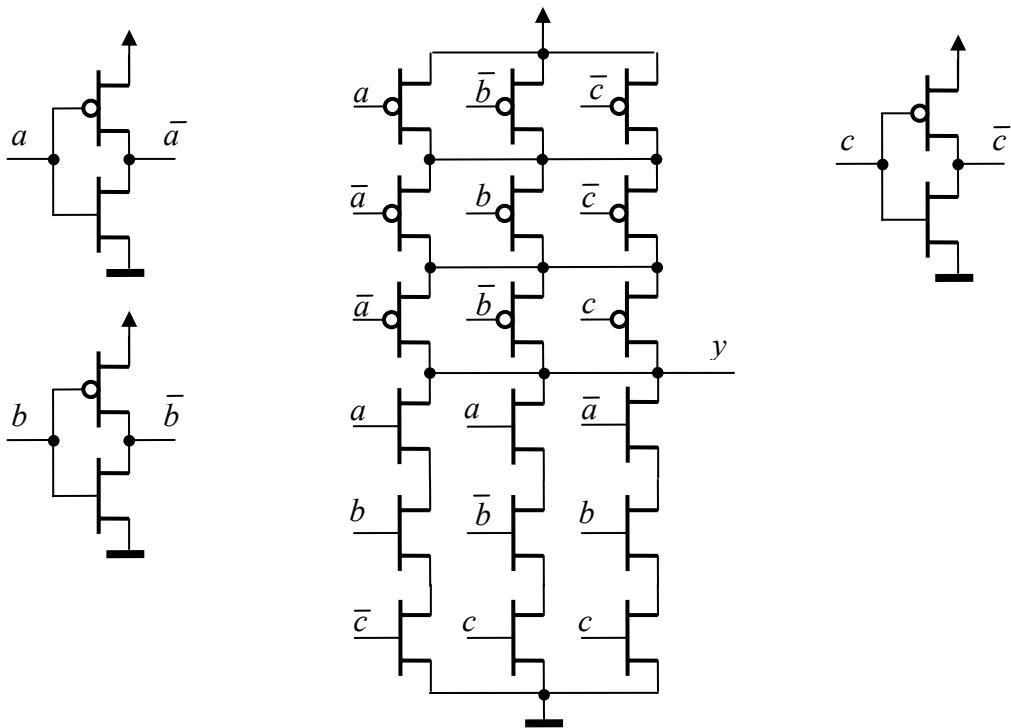

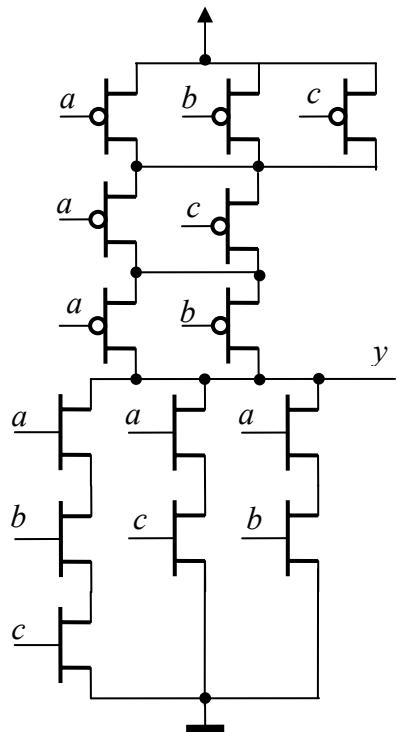

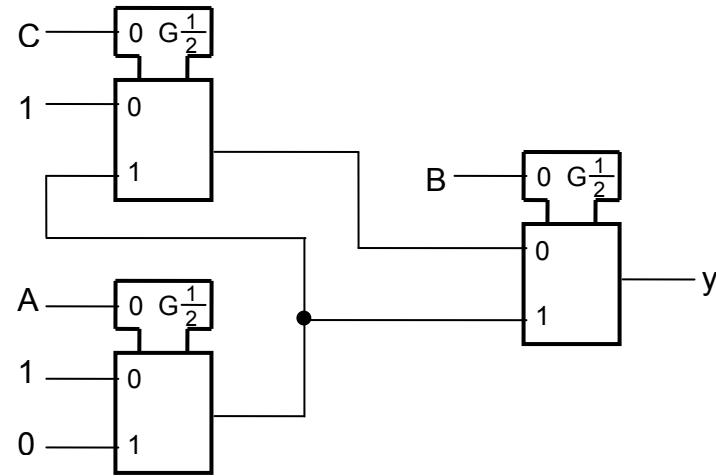

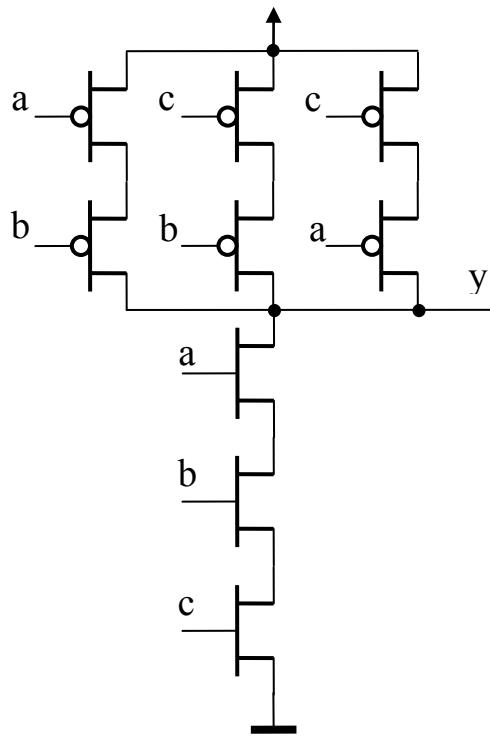

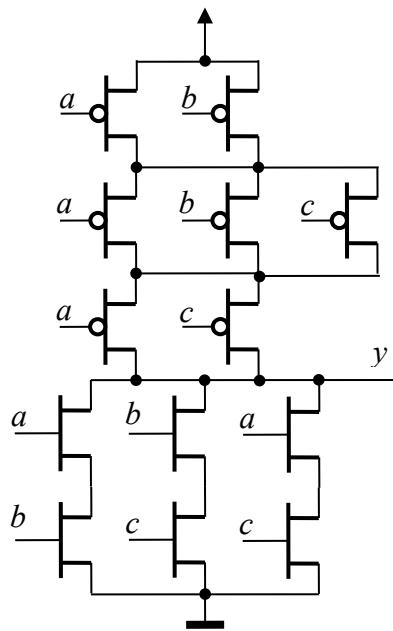

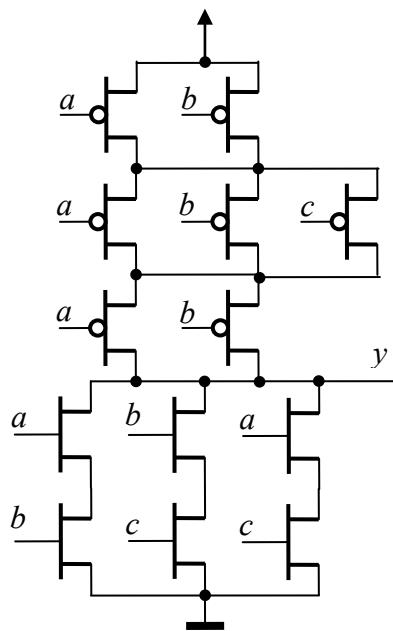

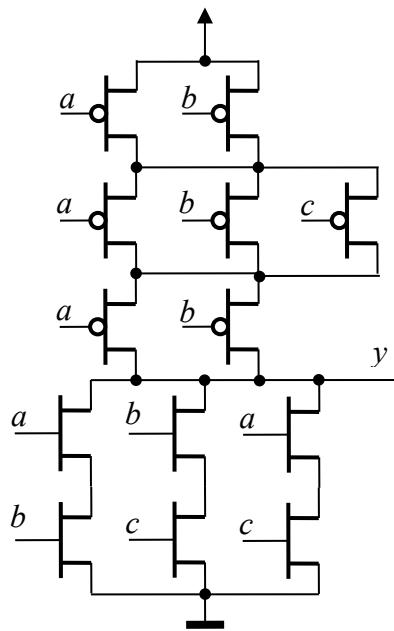

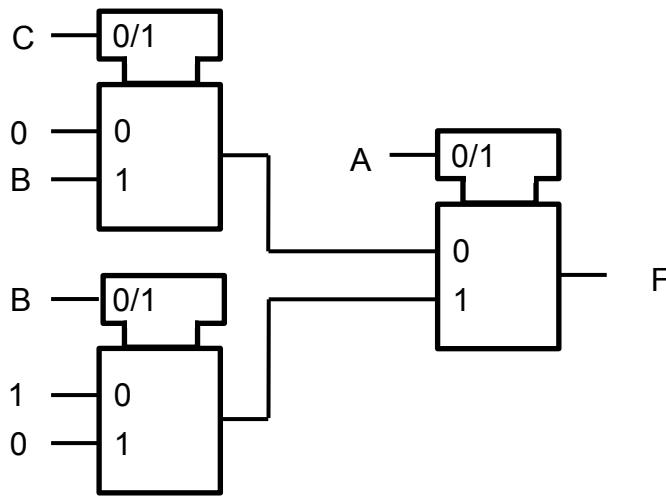

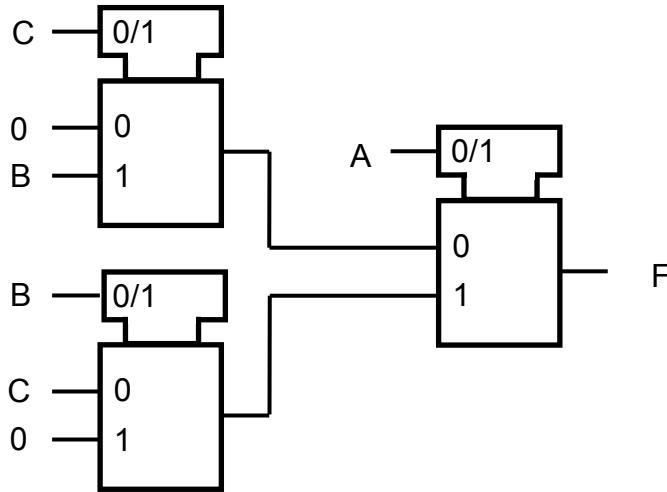

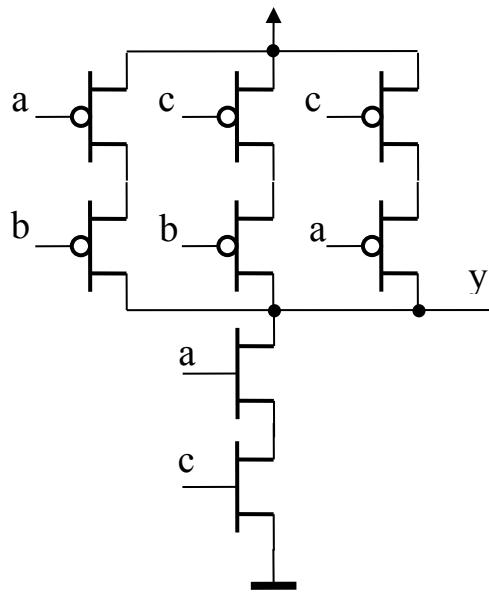

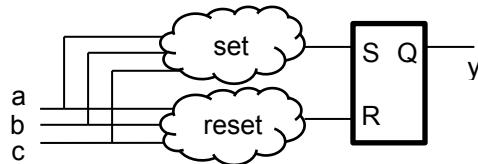

Abbildung 1 zeigt die FET-Realisierung einer logischen Funktion  $y(a,b,c)$ .

Abbildung 1

- Leiten Sie anhand dieses Schaltbildes her, welchen Wert der Ausgang  $y$  für folgendes Bitmuster am Eingang annimmt:  $(a,b,c) = (1,0,1)$  !

- Geben Sie die Funktion  $y$  in Form einer Booleschen Gleichung an!

- Zeichnen Sie das KV-Diagramm dieser Funktion  $y$  !

- Leiten Sie aus dem KV Diagramm eine vereinfachte Darstellung der Funktion  $y$  her

- Zeichnen Sie die FET-Realisierung dieser vereinfachten Form. Was hat sich geändert? Warum?

## Beispiel 2

Zu realisieren ist eine Schaltung, die von einer Zahl  $b$  das Quadrat  $y$  berechnet. Der Eingangswert  $b$  ist als positive Binärzahl  $(b_2, b_1, b_0)$  dargestellt, ebenso das Ergebnis  $y$   $(y_5, y_4, y_3, y_2, y_1, y_0)$ .

- Beschreiben Sie eine Realisierung als ROM: Welches ROM benötigen Sie (Speicherzellen, Wortbreite), wie beschalten Sie die Adressen, wie die Daten? Geben Sie eine Liste der Speicherinhalte an!

- Gehen Sie von der Liste der Speicherinhalte aus (a) aus und beschreiben Sie die logischen Verknüpfungen, die Sie für  $y_0, y_1, y_3$  und  $y_5$  realisieren müssten, wenn Sie die Funktion mittels logischer Grundfunktionen realisieren wollten.

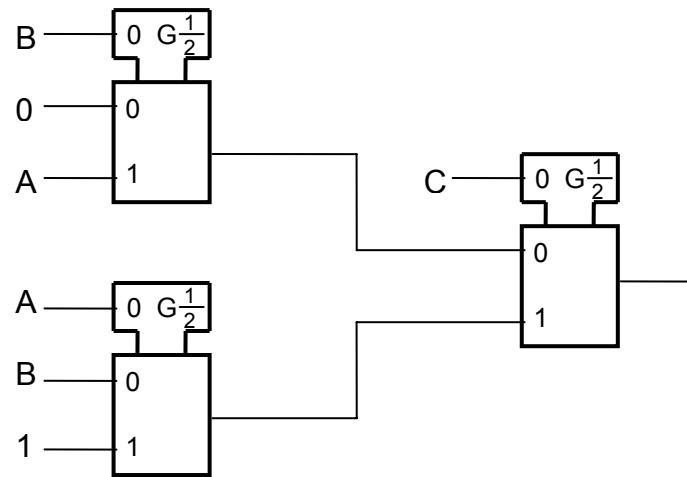

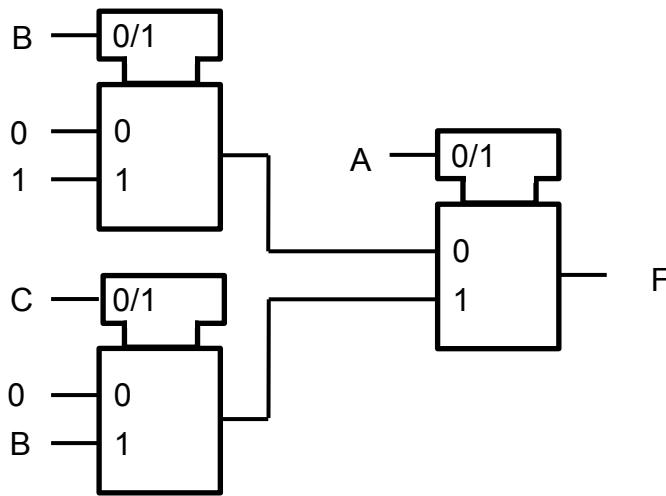

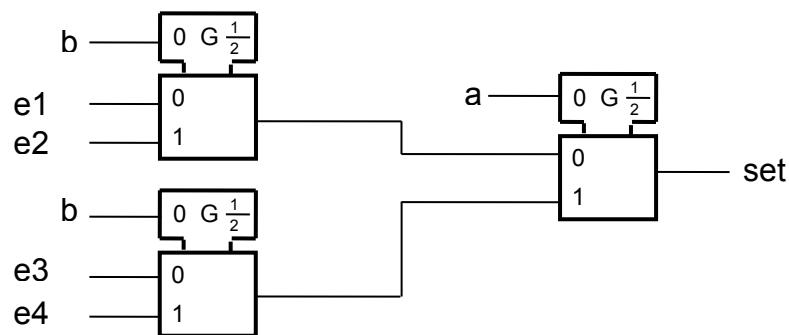

- Leiten Sie eine Realisierung für die Funktion  $y_3(b_2, b_1, b_0)$  mittels Multiplexer-basierter Logik (wie im ACTEL-FPGA) her! Zeichnen Sie das Schaltbild Ihrer Lösung!

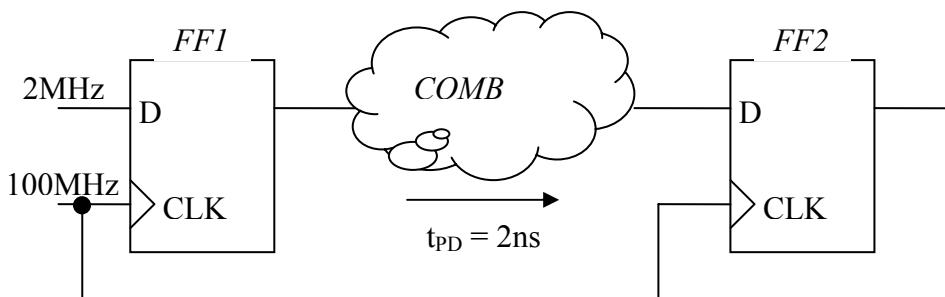

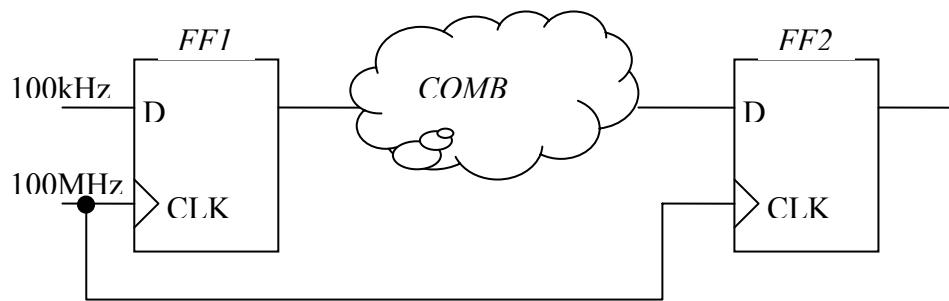

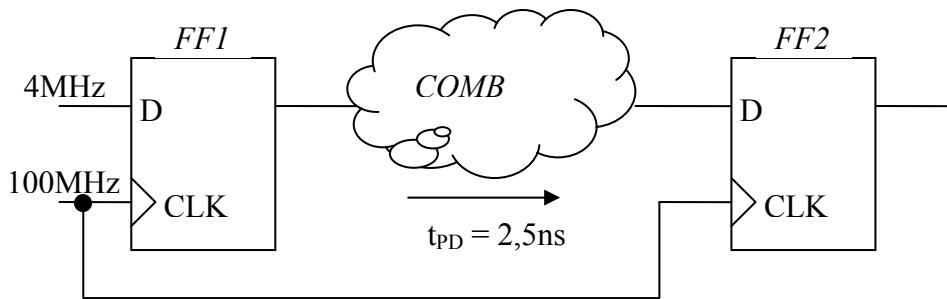

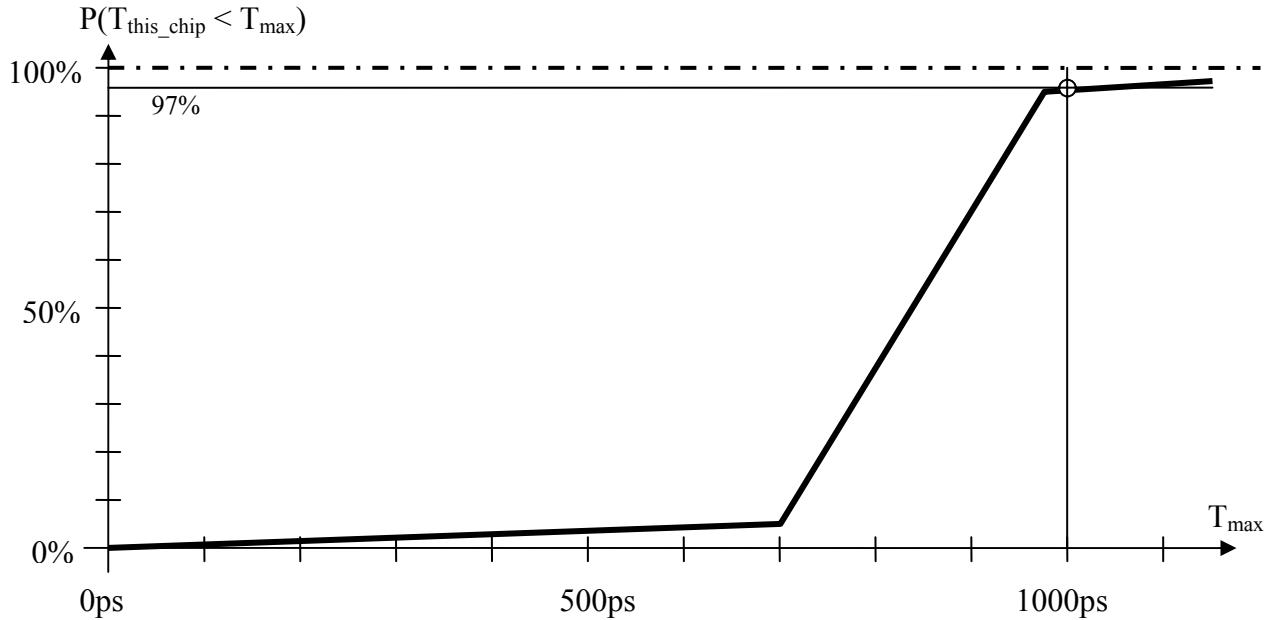

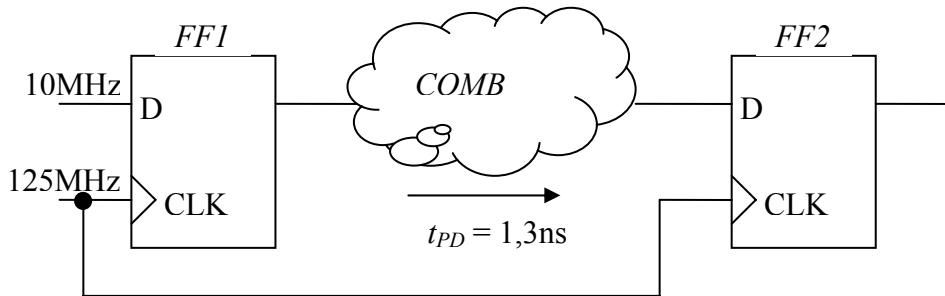

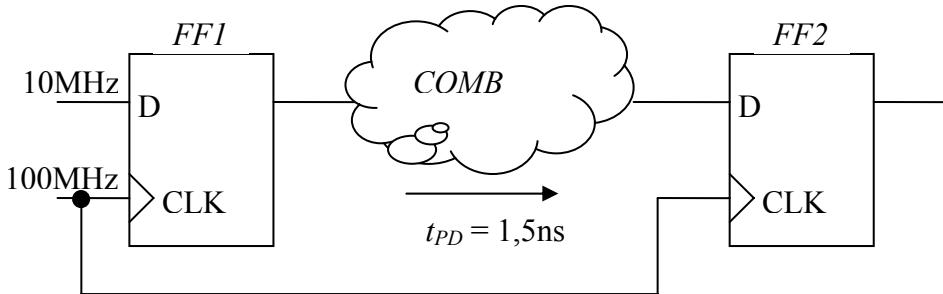

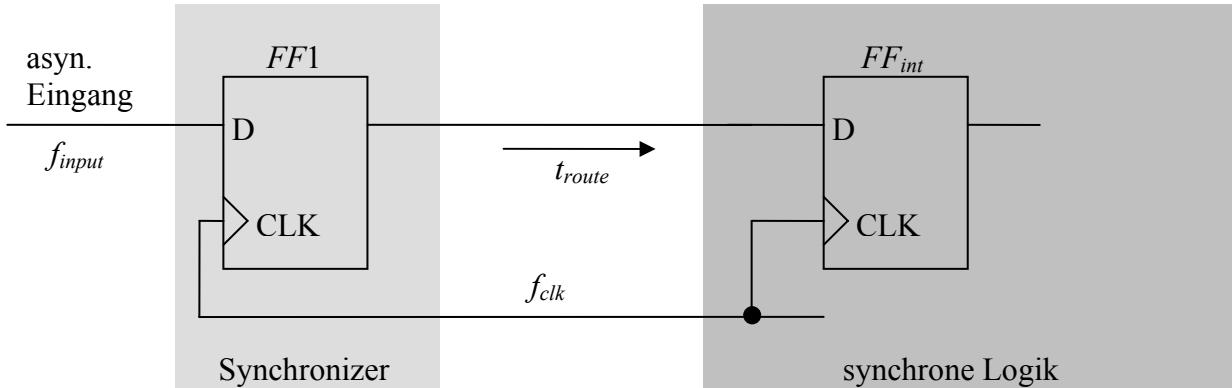

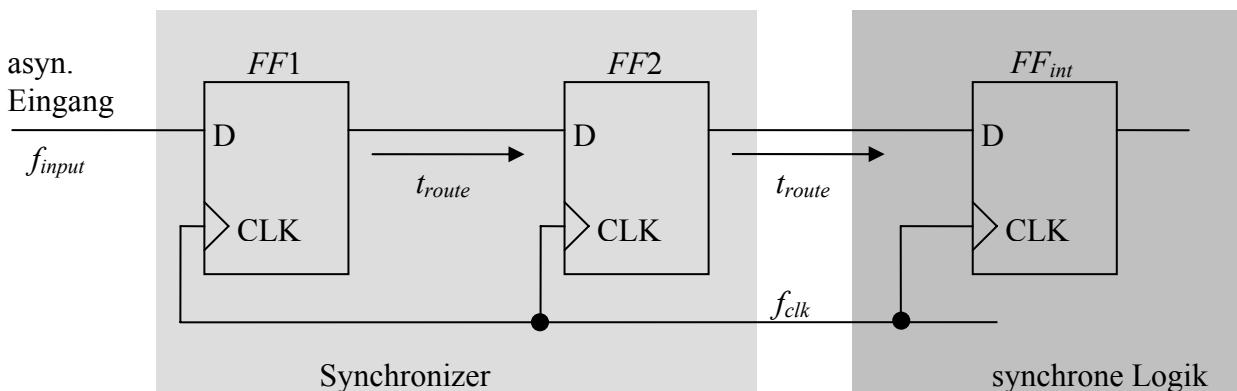

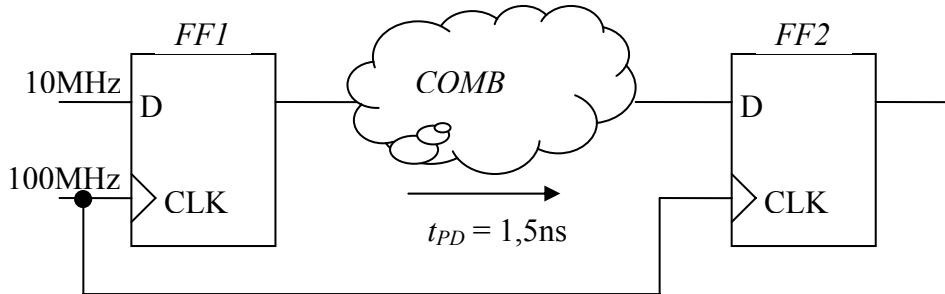

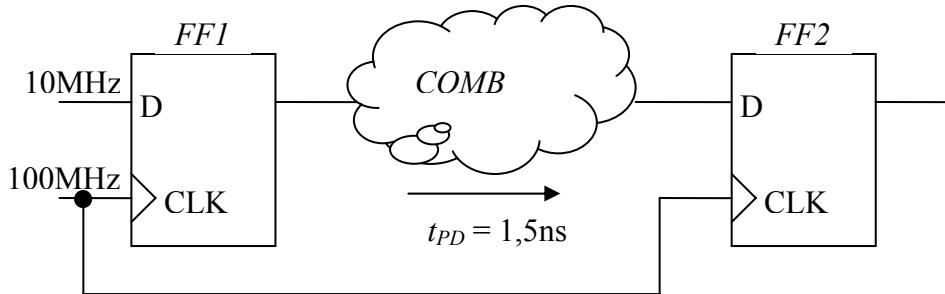

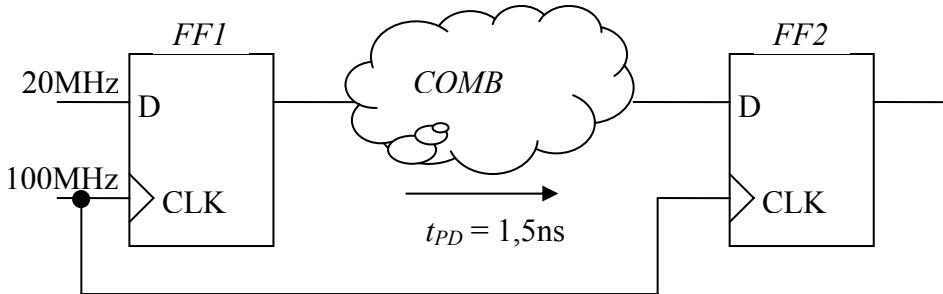

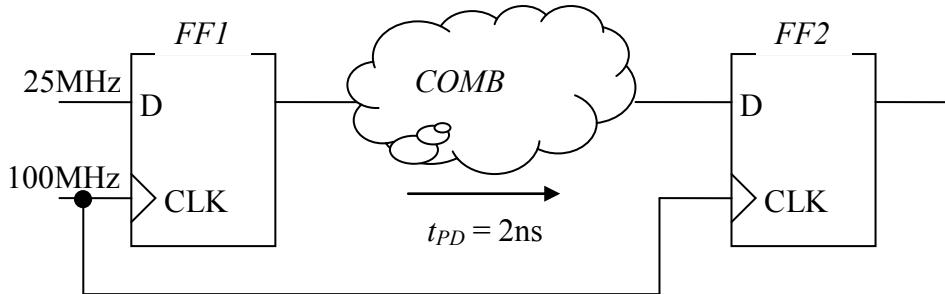

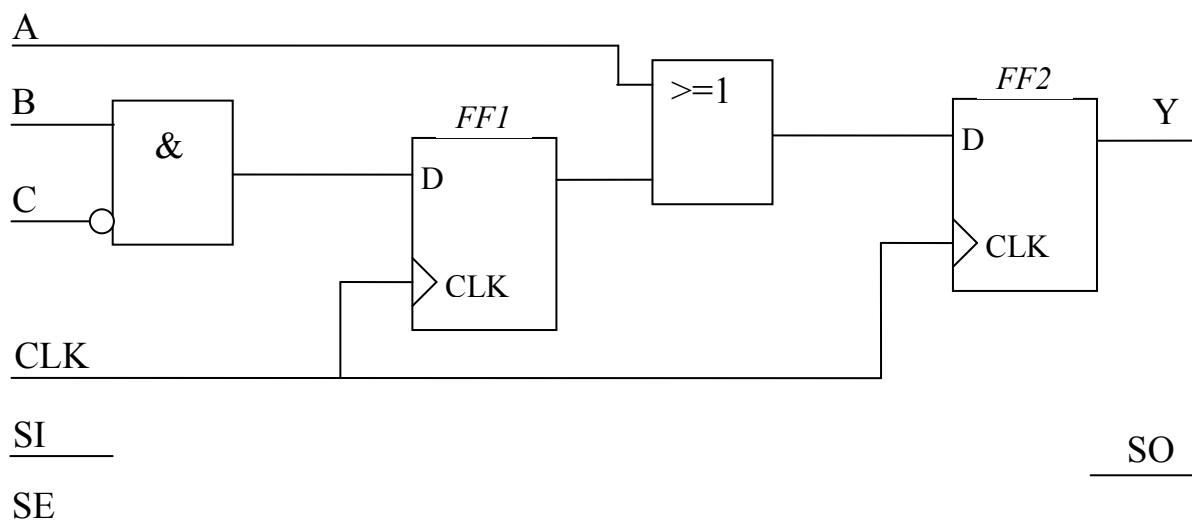

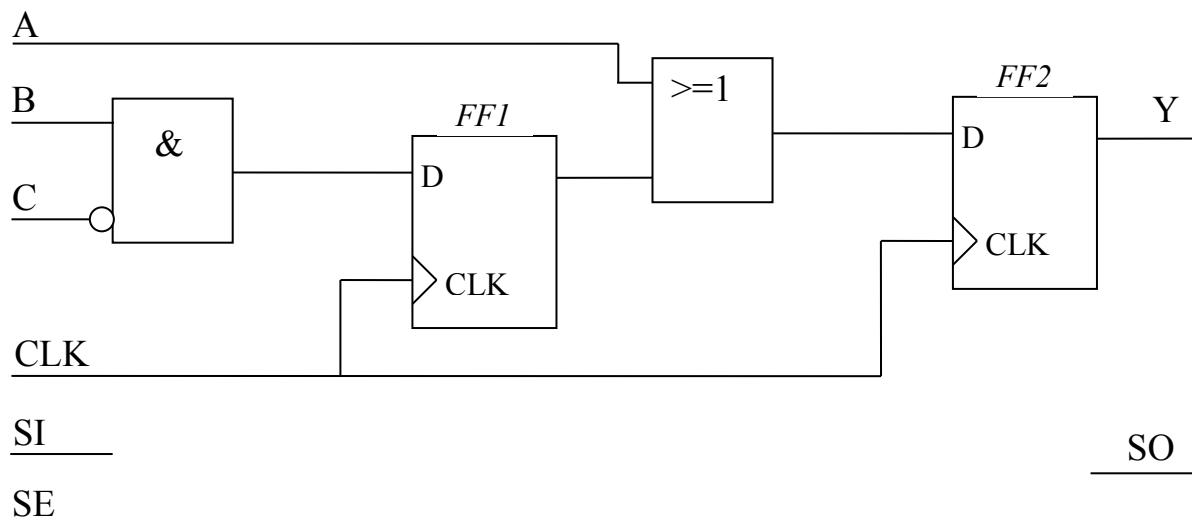

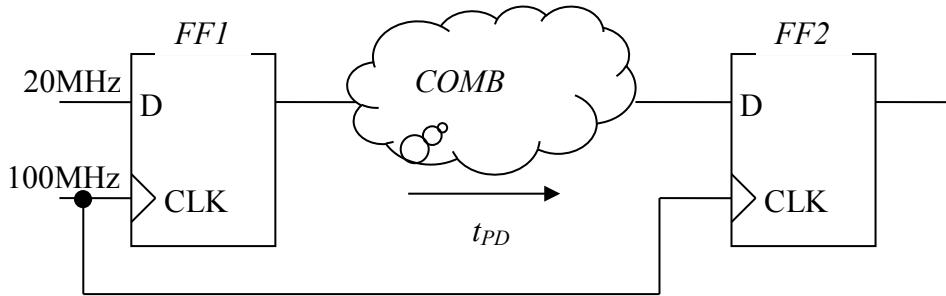

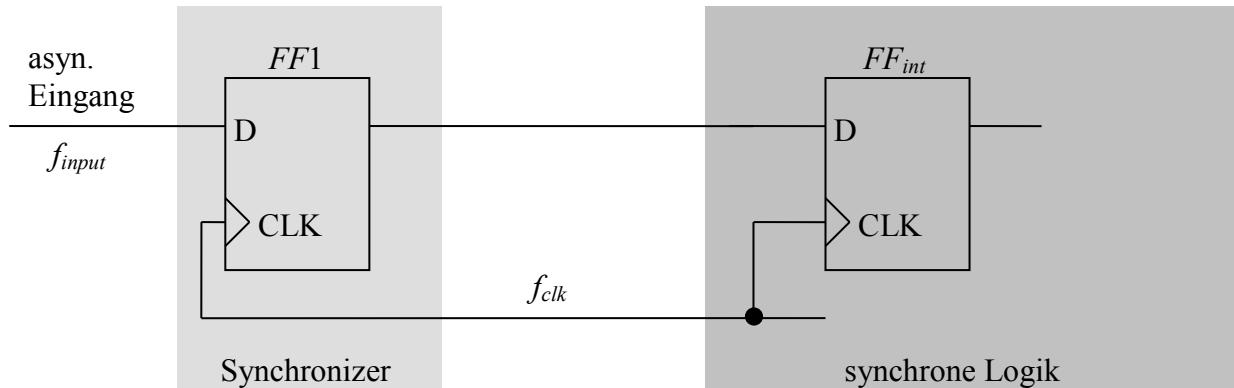

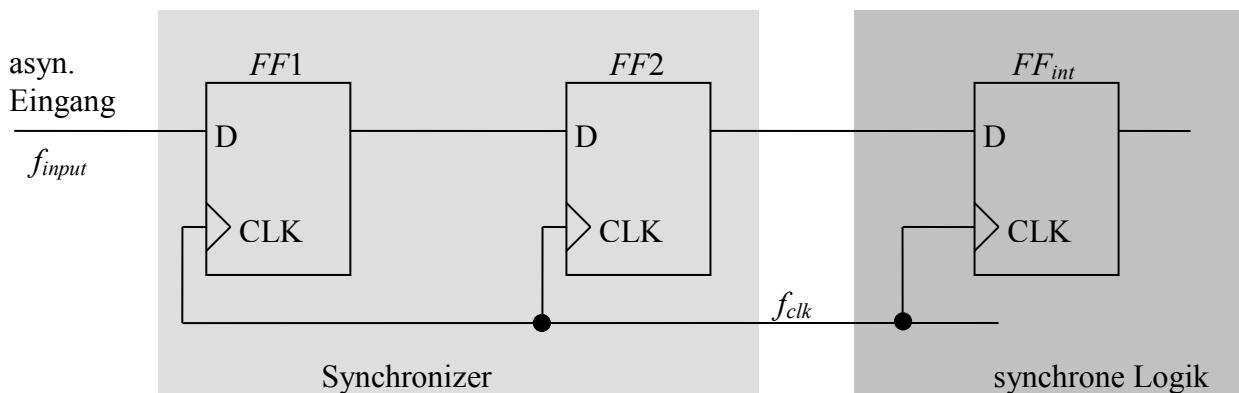

## Beispiel 3

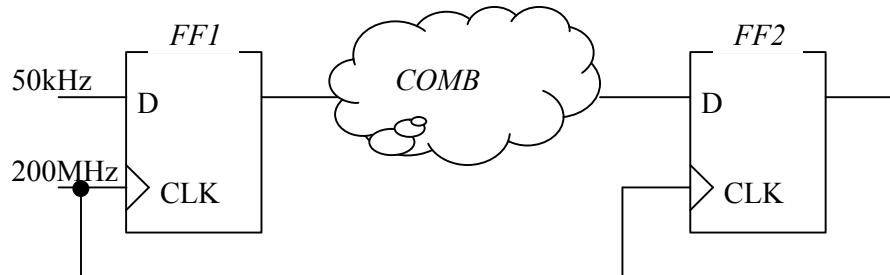

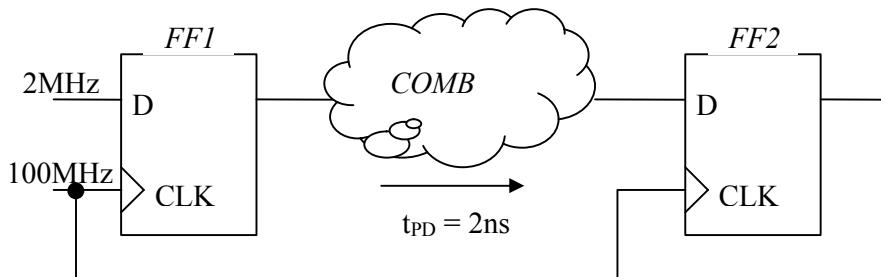

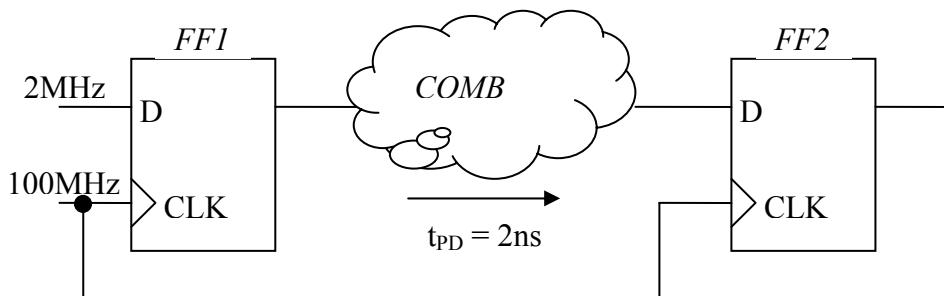

Gegeben ist die in Abbildung 2 dargestellte Schaltung mit 100MHz Takt. Ein asynchrones Eingangssignal mit 2MHz liegt am Eingang von Flip-Flop  $FF1$ . Der Ausgang von  $FF1$  geht über kombinatorische Logik  $COMB$  an den Eingang von Flip-Flop  $FF2$ . Die Verzögerungszeit der kombinatorischen Logik beträgt 2ns. Laut Datenblatt haben die beiden Flip-Flops folgende Parameter:

$$t_{SU} = 1\text{ns} ; \quad \tau_C = 0,25\text{ns} ; \quad T_0 = 0,1\text{ns} .$$

Abbildung 2

- Welche MTBU ist zu erwarten ?

- Die Testabteilung schreibt nun vor, dass vor die D-Eingänge der beiden Flipflops jeweils ein Multiplexer geschaltet werden muss. Welchen Grund wird die Testabteilung dafür haben?

- Die Multiplexer verursachen im Datenpfad ein Delay von 2ns. Welche MTBU ergibt sich nun?

- Auf welchen Wert müssten Sie die Frequenz des asynchronen Eingangssignals verringern, um wieder die ursprüngliche MTBU zu erreichen?

## Beispiel 4

Gegeben ist folgender VHDL-Code einer State-Machine:

```

library IEEE;

use      IEEE.std_logic_1164.all;

entity silence is

port(

yes  : in std_logic;

no   : in std_logic;

upset: in std_logic;

alpha: out std_logic_vector(0 to 1);

);

end silence;

```

```

architecture sound of silence is

signal one, two:

std_logic_vector(0 to 1);

begin

tick: process(one)

begin

case one is

when "00"  => two <= "01";

when "01"  => two <= "10";

when "10"  => two <= "11";

when others => two <= "00";

end case;

end process tick;

trick: process(yes, no)

begin

if no = '0' then

one <= "00";

else

if yes'event and yes = '1' then

one <= two;

end if;

end if;

end process trick;

track: process(one)

begin

if upset = "1" then

alpha <= "111";

else

case one is

when "00"  => alpha <= "101";

when "01"  => alpha <= "001";

when "10"  => alpha <= "110";

when others => alpha <= "010";

end case;

end if;

end process track;

end sound;

```

- Identifizieren Sie Taktsignal und Reset!

- Nennen Sie die 3 Funktionsblöcke, die eine State-Machine stets umfassen muß? Welcher Process im obigen Code entspricht welchem Funktionsblock?

- Um welchen Typ von State-Machine (Moore oder Mealy) handelt es sich? Begründen Sie!

- Verändern Sie den Code so, dass der Reset nun synchron anstelle von asynchron wird (Schreiben Sie den Code für den entsprechend veränderten Process vollständig an)!

# Vorlesungsprüfung aus Digitales Design

28. April 2003

---

Die Arbeitszeit beträgt 2 Stunden. Als Hilfsmittel sind ausnahmslos Schreibzeug, Lineal und (nicht programmierbarer) Taschenrechner erlaubt. Schreiben Sie Ihre Antworten und Lösungen (incl. Lösungsweg!) mit dokumentechten Stiften (Füllfeder, Kugelschreiber, KEIN Bleistift!) und streichen Sie alles durch, was nicht zur Beurteilung herangezogen werden soll. Ein Abbruch der Prüfung nach Erhalt der Angaben führt in jedem Fall zu einer Beurteilung.

Tragen Sie Namen, Kennzahl und Matrikelnummer **zu Beginn** der Prüfung in die Tabelle ein und beschriften Sie jedes Blatt, das Sie abgeben möchten rechts oben mit Namen und Matrikelnummer.

|               |                 |

|---------------|-----------------|

| Familienname: | Vorname:        |

| Kennzahl:     | Matrikelnummer: |

Viel Erfolg!

**Die nachfolgende Tabelle nicht beschriften!**

| Beispiel       | Mögliche Punkte | Erhaltene Punkte |

|----------------|-----------------|------------------|

| Theoriefragen  | 50              |                  |

| Rechenbeispiel | 1               | 15               |

|                | 2               | 10               |

|                | 3               | 10               |

|                | 4               | 15               |

| Gesamt         | 100             |                  |

## Theoriefragen

**Frage 1:**

Was passiert wenn man bei einem SR-Latch ohne Enable sowohl S als auch R aktiviert?

**Frage 2:**

Welche elektrische Funktion hat das Siliziumdioxid im Chip?

**Frage 3:**

Was ist ein Transmission Gate und wie ist es aufgebaut?

**Frage 4:**

Geben Sie die Signal-Resolution-Table für die Funktion OR und die Zustände {0,1,X} an!

**Frage 5:**

Warum haben EPROMs ein Fenster im Gehäuse?

**Frage 6:**

Was versteht man unter dem Elmore-Delay?

**Frage 7:**

Angenommen die Versorgungsspannung eines Chip liegt am unteren Ende des Toleranzbereiches. Wird der Chip dadurch schneller oder langsamer als beim Nominalwert?

**Frage 8:**

Was ist Latch-up?

**Frage 9:**

Welche Probleme treten beim „exhaustive Test“ in der praktischen Anwendung auf?

**Frage 10:**

Was versteht man unter Metastabilität?

## Rechenbeispiele

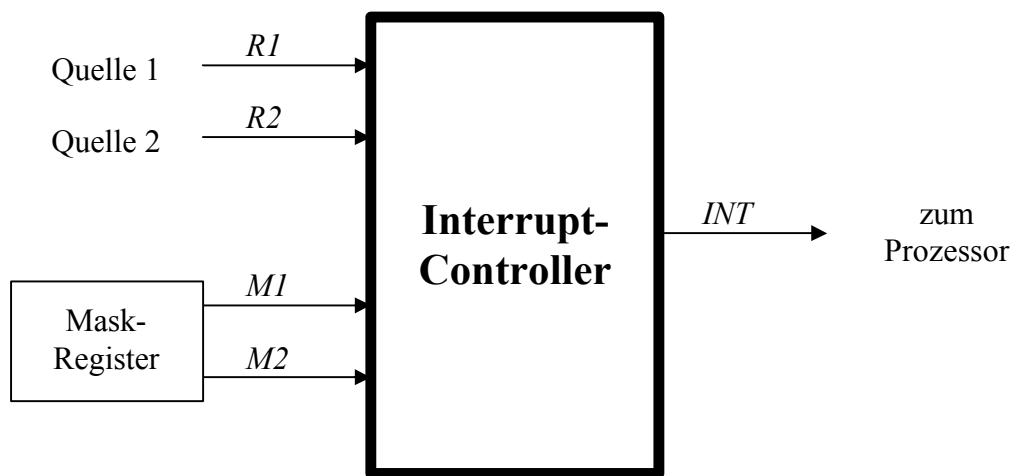

### Beispiel 1

Die Abbildung zeigt einen einfachen Interrupt-Controller: Die von 2 Quellen kommenden Request-Signale  $R1$  und  $R2$  werden zu einem gemeinsamen Interrupt-Request  $INT$  zusammengefasst, das schließlich an den Prozessor geleitet wird. Für jede Quelle kann mittels eines Mask-Bits ( $M1, M2$ ) der zugehörige Request maskiert oder freigegeben werden. Alle Request-Signale sind LO aktiv, d.h.  $INT$  ist dann LO wenn zumindest einer der freigegebenen Requests LO ist. Ein Request ist freigegeben, wenn das zugehörige Mask-Bit HI ist.

- Geben Sie Wahrheitstabelle und KV-Diagramm für die Funktion dieses Interrupt-Controllers an!

- Entwerfen Sie eine Realisierung mittels LUT (Welche LUT benötigen Sie, wie ist die LUT zu programmieren, wie ist sie anzuschliessen?)

- Entwerfen Sie eine Realisierung mittels Standard-PLD (3 p-Terms, programmierbarer Ausgangsinverter)

Markieren Sie im gezeichneten Schaltbild die programmierten Verbindungen mit 'O'.

## Beispiel 2

Von einer Versorgungsleitung in einem Chip seien folgende Kennwerte bekannt:

Querschnitt =  $10\mu\text{m}^2$ ; Material: Aluminium ( $E_{\text{act}} = 0.7\text{eV}$ );  $k = 8,6 \cdot 10^{-5}\text{eV/K}$

Bei Betrieb mit einem Strom von 2A und einer Junction-Temperatur  $T_J = 80^\circ\text{C}$  beträgt die MTTF dieser Leitung 10 Jahre.

Aufgrund eines Maskenfehlers bei der Fertigung beträgt der Querschnitt dieser Leitung jedoch nur  $4\mu\text{m}^2$ .

- (a) Welche MTTF ist zu erwarten?

- (b) Beim Burn-in wird der Chip 100 Stunden lang (bei unveränderter Versorgungsspannung) mit  $T_J = 140^\circ\text{C}$  betrieben. Welcher Betriebsdauer entspricht dies bei Normalbetrieb?

- (c) Ist der Test geeignet, den Defekt zu erkennen? Begründen Sie!

## Beispiel 3

Von einem bestimmten Server werden 1 Million Stück gefertigt. Jeder dieser Server ist mit einem DMA-Controller-Chip ausgerüstet. Ein solcher Controller Chip kostet 3€ und weist bei der Fertigung einen Defect Level von 5% auf. Die Kosten für die Reparatur des Servers aufgrund eines defekten DMA-Controllers betragen im Mittel 1000€.

- (a) Welchen finanziellen Schaden verursachen die Reparaturkosten für die nicht entdeckten Controller-Chips?

- (b) Durch einen Funktionstest aller mit dem Controller bestückten Platinen vor dem Einbau in den Server könnte man 70% der verbliebenen Defekte erkennen, für die sich die Reparaturkosten dann auf 200€ reduzieren. Ist die Anwendung eines solchen Tests wirtschaftlich sinnvoll, wenn dadurch Testkosten von 40€ je Platine anfallen?

- (c) Durch einen Built-in Self-Test kann die Defektrate des Chips von 5% auf 1% vermindert werden. Ist die Anwendung des BIST wirtschaftlich sinnvoll, wenn die zusätzlich benötigte Testlogik den Preis des Controllers auf 4€ erhöht?

## Beispiel 4

Als erste Aufgabe in einer neuen Firma bekommen Sie von Ihrem Chef ein Stück VHDL-Code. Es beschreibt angeblich eine State-Machine, die ein Spiel implementiert. Ihr Vorgänger hat den Code kurz vor seiner Entlassung geschrieben und Ihre Aufgabe besteht nun darin, die Funktion des Codes nachzuvollziehen.

```

architecture cryptic of game is

signal a, b, k, p, x, y: std_logic;

begin

ONE: process(k, p)

if k = '1' then

x <= '0';

else

if p'event and p = '1' then

x <= y;

end if;

end if;

end process ONE;

TWO: process(a, x)

if a = '0' then

y <= x;

else

y <= NOT(x);

end if;

end process TWO;

THREE: process(a, x)

if a = '1' then

b <= '0';

else

b <= x;

end if;

end process THREE;

end cryptic;

```

- (a) Welches Signal entspricht dem Takt? Begründen Sie!

Ist die steigende oder die fallende Taktflanke die aktive?

- (b) Welches Signal entspricht dem Reset?

Handelt es sich um einen synchronen oder einen asynchronen Reset?

Ist der Reset HI-aktiv oder LO-aktiv? Begründen Sie!

- (c) Handelt es sich um eine State-Machine vom Moore-Type oder vom Mealy-Type?

Begründen Sie!

Beschreiben Sie die Teilaufgaben der einzelnen Prozesse!

- (d) Beschreiben Sie die Funktion des Spiels:

Welches Signal entspricht dem Eingang, welches dem Ausgang?

Was passiert mit dem Zustand und dem Ausgang wenn der Eingang auf '1' geht?

Was passiert beim Reset?

# Vorlesungsprüfung aus Digitales Design

## 29. Jänner 2003

---

Die Arbeitszeit beträgt 2 Stunden. Als Hilfsmittel sind ausnahmslos Schreibzeug, Lineal und (nicht programmierbarer) Taschenrechner erlaubt. Schreiben Sie Ihre Antworten und Lösungen (incl. Lösungsweg!) mit dokumentechten Stiften (Füllfeder, Kugelschreiber, KEIN Bleistift!) und streichen Sie alles durch, was nicht zur Beurteilung herangezogen werden soll. Ein Abbruch der Prüfung nach Erhalt der Angaben führt in jedem Fall zu einer Beurteilung.

Tragen Sie Namen, Kennzahl und Matrikelnummer **zu Beginn** der Prüfung in die Tabelle ein und beschriften Sie jedes Blatt, das Sie abgeben möchten rechts oben mit Namen und Matrikelnummer.

|               |                 |

|---------------|-----------------|

| Familienname: | Vorname:        |

| Kennzahl:     | Matrikelnummer: |

Viel Erfolg!

**Die nachfolgende Tabelle nicht beschriften!**

| Beispiel       | Mögliche Punkte | Erhaltene Punkte |

|----------------|-----------------|------------------|

| Theoriefragen  | 50              |                  |

| Rechenbeispiel | 1               | 10               |

|                | 2               | 15               |

|                | 3               | 15               |

|                | 4               | 10               |

| Gesamt         | 100             |                  |

## Theoriefragen

**Frage 1:**

Was signalisiert das Busy-Flag beim Dual-Port RAM?

**Frage 2:**

Skizzieren Sie die Badewannenkurve (Achsen beschriften) und bezeichnen Sie die Bereiche kurz!

**Frage 3:**

Nennen Sie zwei Effekte, die die Geschwindigkeit von VLSI-Chips maßgeblich begrenzen!

**Frage 4:**

Über welchen Faktor hängen die Komplexitätsmaße „Gate-Count“ und „Anzahl der Transistoren“ zusammen? Erklären Sie diesen Faktor!

**Frage 5:**

Was ist der Unterschied zwischen Floorplanning und Partitionierung?

**Frage 6:**

Erläutern Sie das Prinzip des Boundary-Scan!

**Frage 7:**

Was versteht man im Zusammenhang mit einem PLD unter einem Product Term?

**Frage 8:**

Wozu benötigt man bei der Fertigung eines ICs die Masken?

**Frage 9:**

Was ist ein Schmitt-Trigger-Eingang? Wozu wird er verwendet?

**Frage 10:**

Was versteht man unter einem Glitch? Wie kommt es zu seinem Auftreten?

## Rechenbeispiele

### Beispiel 1

Zu realisieren ist die folgende Funktion:

$$Y = (A \wedge B) \vee (B \wedge C) \vee (A \wedge C)$$

- (a) Geben Sie die Wahrheitstabelle und das KV-Diagramm für diese Funktion an!

- (b) Skizzieren Sie, wie man die Funktion mittels einer LUT-basierten Logik realisieren kann!

Wie viele Eingänge braucht die LUT, und wie viele Bit benötigt sie?

- (c) Entwerfen Sie eine Realisierung mittels Multiplexer-basierter Logik!

Skizzieren Sie Ihre Lösung!

Wie viele Multiplexer mit 2 Eingängen benötigen Sie?

### Beispiel 2

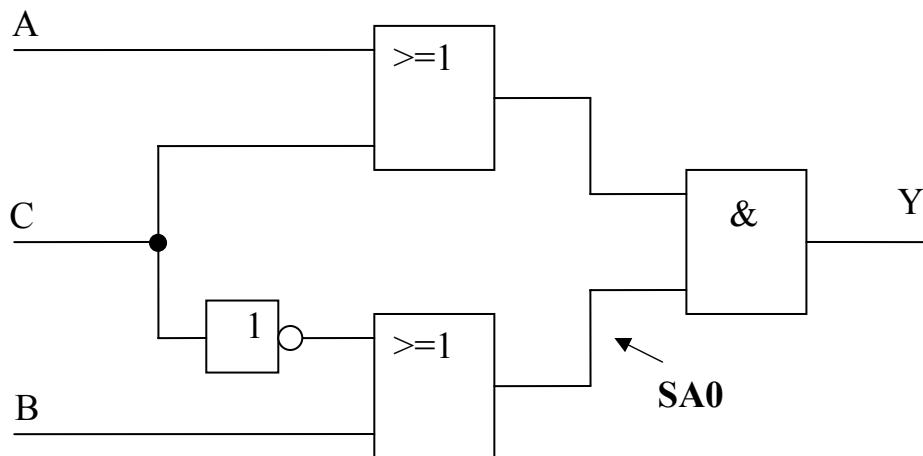

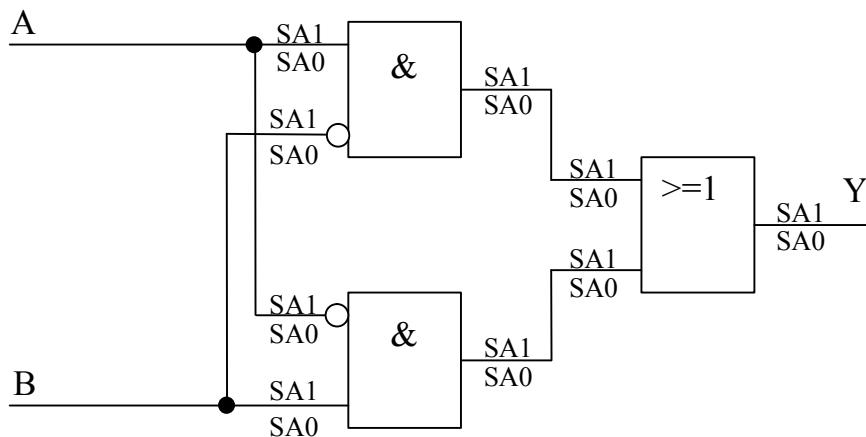

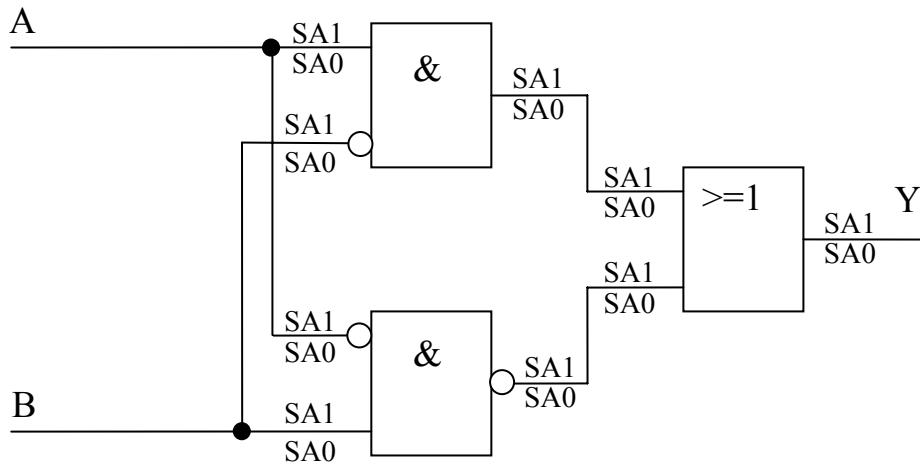

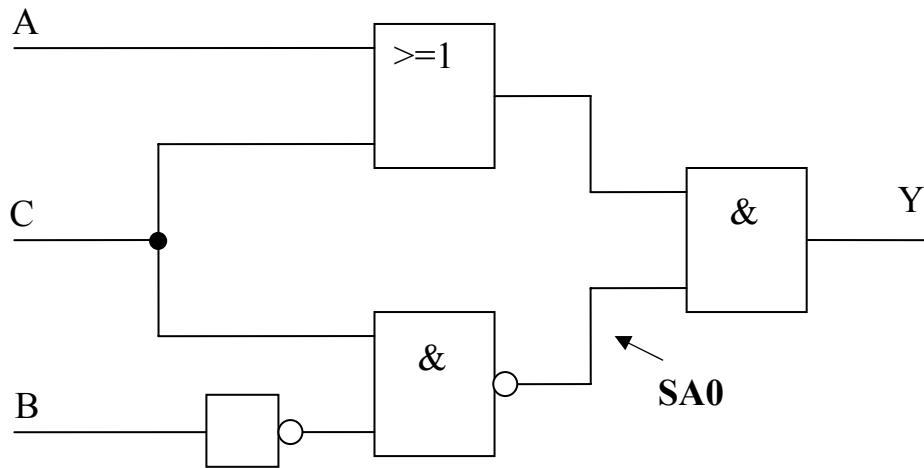

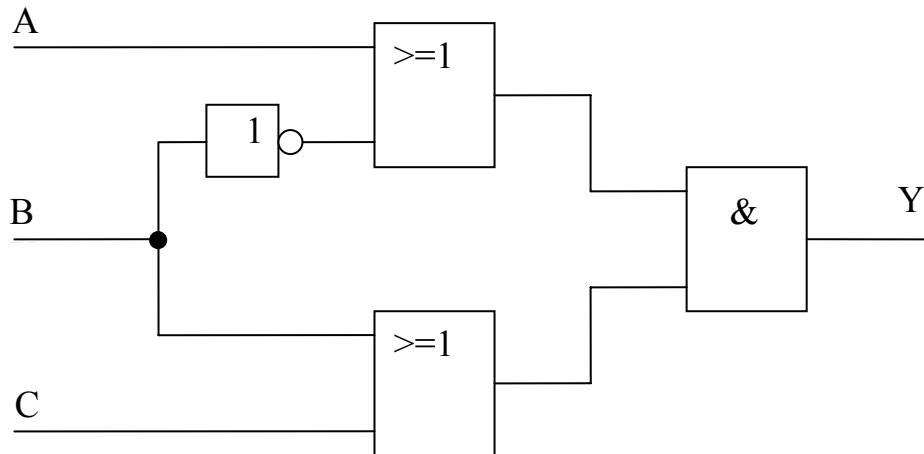

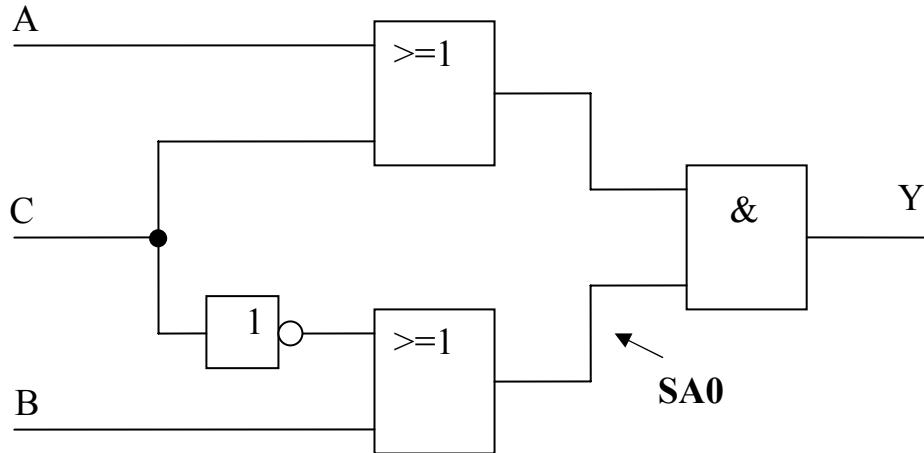

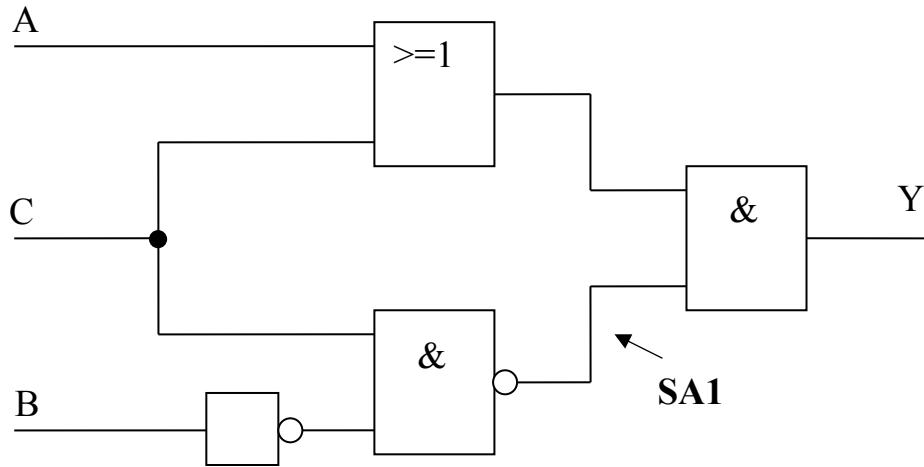

Gegeben ist die Schaltung in Abbildung 1. Arbeiten Sie mit dem single-Stuck-at Fehlermodell.

Abbildung 1

- (a) Welche Grundfunktion erfüllt diese Schaltung ?

- (b) Wie viele Testvektoren benötigen Sie für einen Exhaustive Test dieser Schaltung?

Geben Sie die Vektoren an!

- (c) In Abbildung 1 ist ein Knoten mit „SA0“ gekennzeichnet. Ermitteln Sie alle Testvektoren die geeignet sind, diesen Fehler zu entdecken. Bezeichnen Sie die dazu nötigen Schritte.

- (d) Zeigen Sie in der Schaltung ein Beispiel für Fehleräquivalenz!

- (e) Zeigen Sie in der Schaltung ein Beispiel für Fehlerdominanz!

### Beispiel 3

Gegeben ist der folgende VHDL-Code:

```

Architecture BEISPIEL_3 of PRÜFUNG is

begin

signal A, B, C : std_logic ;

A <= '1';

ZUWEISUNGEN: process(B)

variable D: integer;

begin

A <= '0';

B <= '1';

D := 1;

C <= not(B);

D:= D + 3;

end process ZUWEISUNGEN;

end BEISPIEL_3;

```

(a) Zeigen Sie den Ablauf der Simulation, indem Sie Tabelle 1 vervollständigen!

Wie viele Delta-Cycles werden durchlaufen?

(b) Welche stabilen Werte ergeben sich für A, B, C und D schlussendlich?

| t        | A   | B   | C   | D |

|----------|-----|-----|-----|---|

| 0 (init) | '0' | '0' | '0' | 0 |

|          |     |     |     |   |

|          |     |     |     |   |

|          |     |     |     |   |

|          |     |     |     |   |

**Tabelle 1**

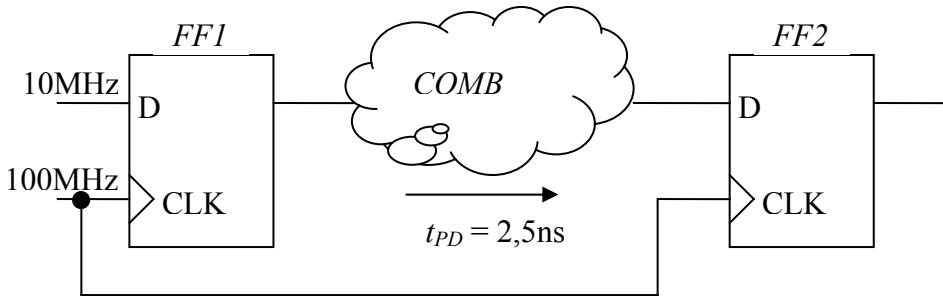

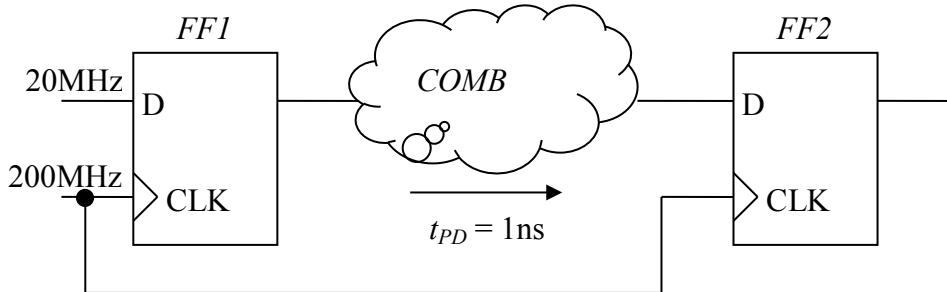

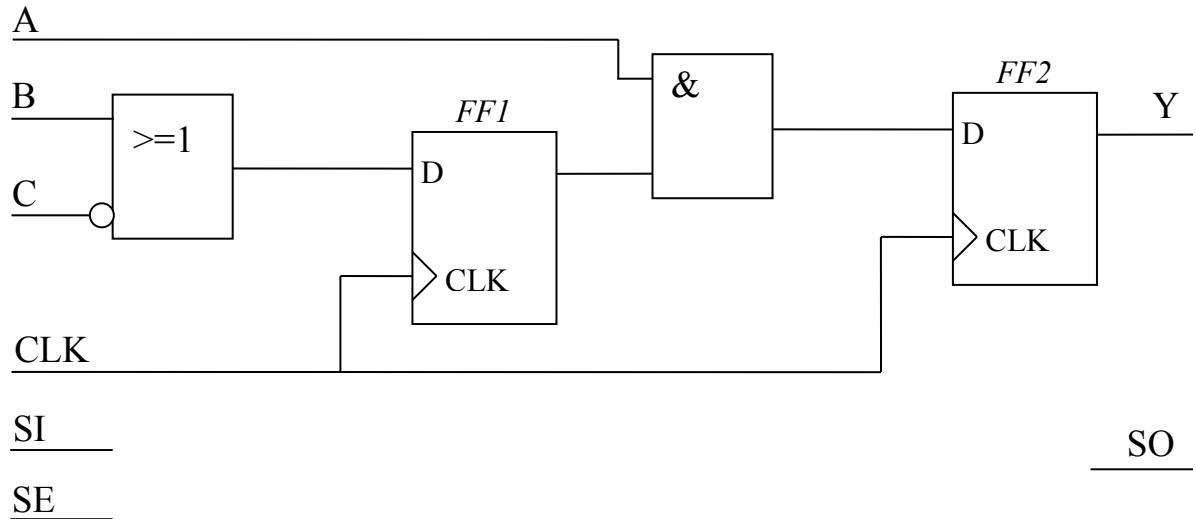

## Beispiel 4

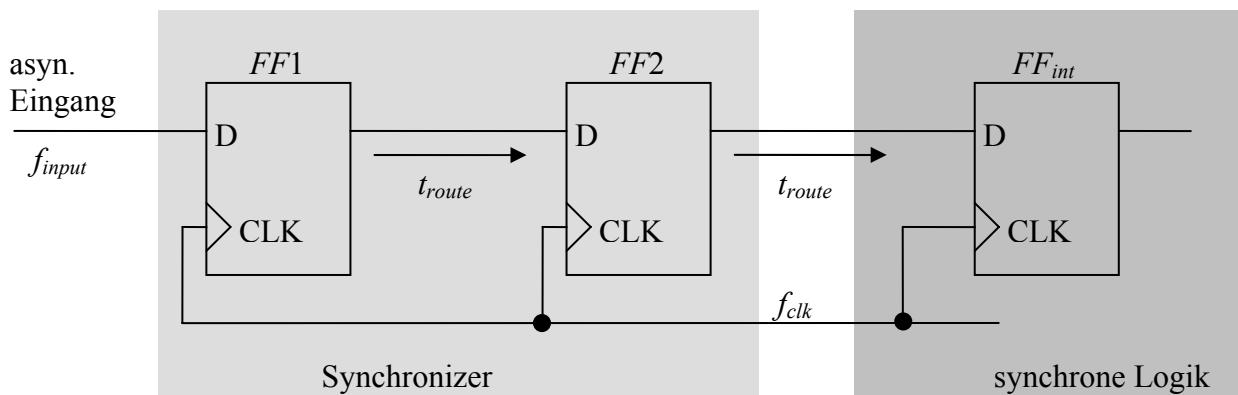

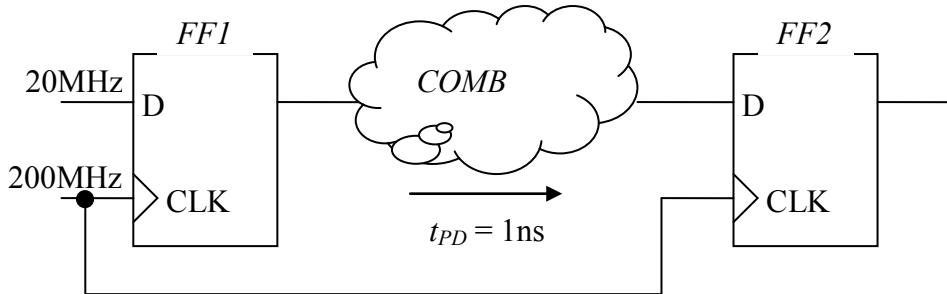

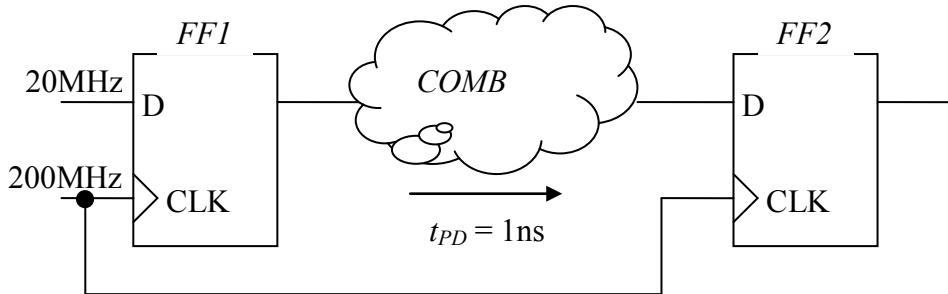

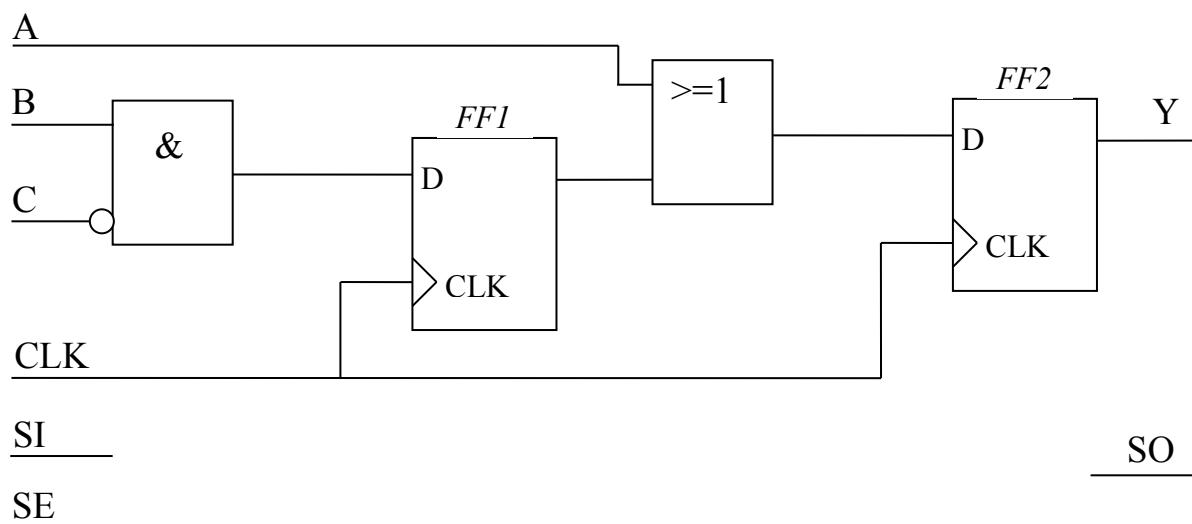

Gegeben ist die in Abbildung 2 dargestellte Schaltung mit 100MHz Takt. Ein asynchrones Eingangssignal mit 100kHz liegt am Eingang von Flip-Flop *FF1*. Der Ausgang von *FF1* geht über kombinatorische Logik *COMB* an den Eingang von Flip-Flop *FF2*. Die Verzögerungszeit der kombinatorischen Logik beträgt 3ns. Laut Datenblatt haben die beiden Flip-Flops folgende Parameter:

$$t_{SU} = 1\text{ns} ; \quad \tau_C = 0,25\text{ns} ; \quad T_0 = 0,1\text{ns} .$$

- (a) Wann spricht man bei dieser Schaltung von einem „Upset“?

- (b) Welche MTBU ist zu erwarten?

- (c) Die beiden FFs werden durch Scan-FFs ersetzt, bei denen dem eigentlichen Flip-Flop ein Multiplexer vorgeschaltet ist. Dieser Multiplexer hat einen Delay von 2ns. Welche MTBU ist nun zu erwarten?

Abbildung 2

# Vorlesungsprüfung aus Digitales Design

3. März 2004

---

Die Arbeitszeit beträgt 2 Stunden. Als Hilfsmittel sind ausnahmslos Schreibzeug, Lineal und (nicht programmierbarer) Taschenrechner erlaubt. Schreiben Sie Ihre Antworten und Lösungen (incl. Lösungsweg!) mit dokumentechten Stiften (Füllfeder, Kugelschreiber, KEIN Bleistift!) und streichen Sie alles durch, was nicht zur Beurteilung herangezogen werden soll. Ein Abbruch der Prüfung nach Erhalt der Angaben führt in jedem Fall zu einer Beurteilung.

Tragen Sie Namen, Kennzahl und Matrikelnummer **zu Beginn** der Prüfung in die Tabelle ein und beschriften Sie jedes Blatt, das Sie abgeben möchten rechts oben mit Namen und Matrikelnummer.

|               |                 |

|---------------|-----------------|

| Familienname: | Vorname:        |

| Kennzahl:     | Matrikelnummer: |

Viel Erfolg!

**Die nachfolgende Tabelle nicht beschriften!**

| Beispiel       | Mögliche Punkte | Erhaltene Punkte |

|----------------|-----------------|------------------|

| Theoriefragen  | 50              |                  |

| Rechenbeispiel | 1               | 10               |

|                | 2               | 15               |

|                | 3               | 15               |

|                | 4               | 10               |

| Gesamt         | 100             |                  |

## Theoriefragen

**Frage 1:**

Was passiert wenn man beim SR-Latch sowohl S als auch R aktiviert?

**Frage 2:**

Warum sind Wafer rund?

**Frage 3:**

Wie würden Sie in CMOS ein OR2-Gatter realisieren?

**Frage 4:**

Was sind die Besonderheiten beim Clock-Routing?

**Frage 5:**

Was versteht man unter einem non-volatile Memory?

**Frage 6:**

Welche Motivation steht hinter der „Fast Fuse“ beim ACT2/3, die eine direkte Ankopplung an den Long Vertical Track erlaubt?

**Frage 7:**

Welchen Unterschied macht es, ob Sie den Ausgang eines Gatters mit einem oder mit 10 Eingängen nachfolgender Gatter belasten?

**Frage 8:**

Was versteht man unter Electromigration?

**Frage 9:**

Angenommen Sie finden in Ihrer Chip-Library einen TAP-Controller. Wozu könnten Sie diesen verwenden?

**Frage 10:**

Was versteht man unter dem „Delay insensitive Model“ ?

## Rechenbeispiele

### Beispiel 1

Zu realisieren ist eine Schaltung, die für eine Zahl  $b$  den Wert  $y = 8 - b$  berechnet. Der Eingangswert  $b$  ist als positive Binärzahl ( $b_2, b_1, b_0$ ) dargestellt, ebenso das Ergebnis  $y$ .

- Beschreiben Sie eine Realisierung mittels ROM: Welches ROM benötigen Sie (Anzahl der Adressleitungen und der Speicherzellen, Wortbreite), wie beschalten Sie die Adressen, wie die Daten? Geben Sie eine Liste der Speicherinhalte an!

- Gehen Sie von der Liste der Speicherinhalte aus (a) aus und beschreiben Sie für jedes Ausgangsbit ( $y_n \dots y_0$ ) die logische Verknüpfung, die realisieren müssten, wenn Sie die Funktion mittels logischer Grundfunktionen realisieren wollten!

- Leiten Sie eine Realisierung für die Funktion  $y_1(b_2, b_1, b_0)$  mittels Multiplexer-basierter Logik (wie im ACTEL-FPGA) her! Zeichnen Sie das Schaltbild Ihrer Lösung!

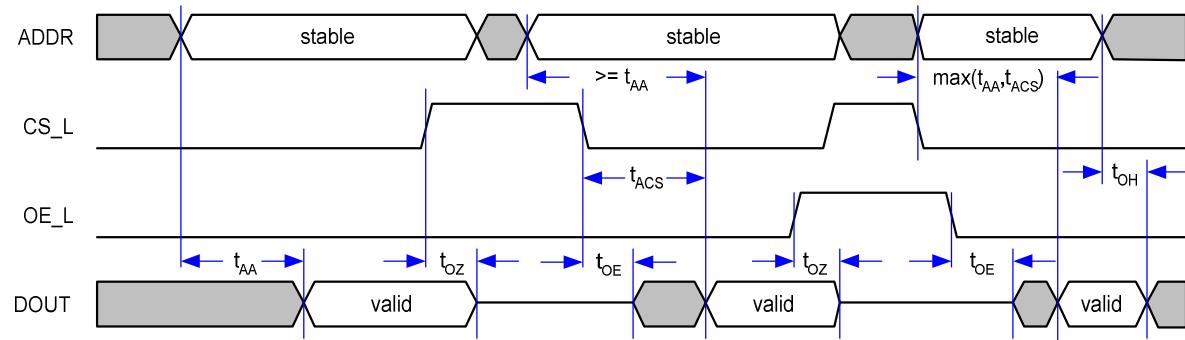

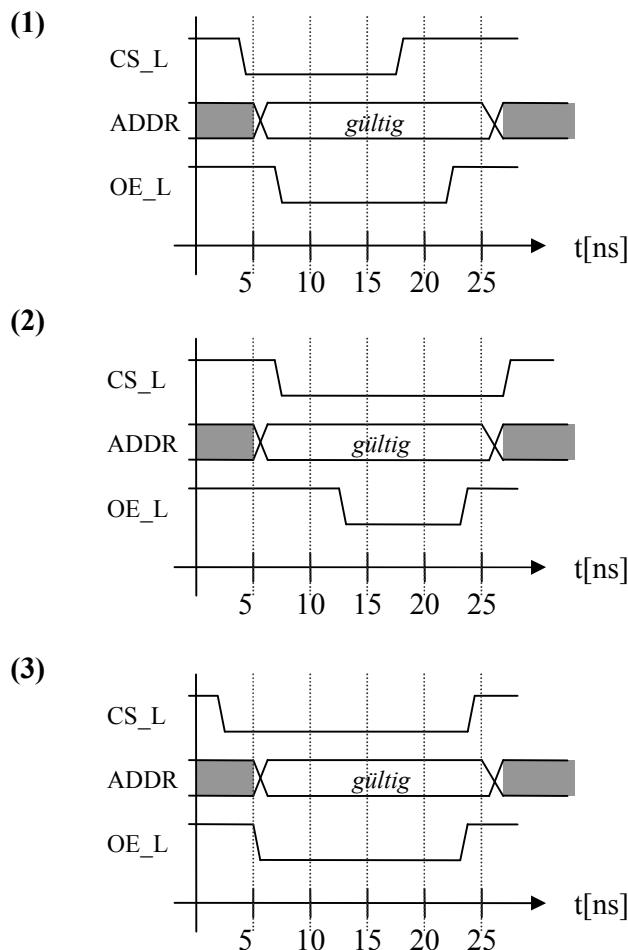

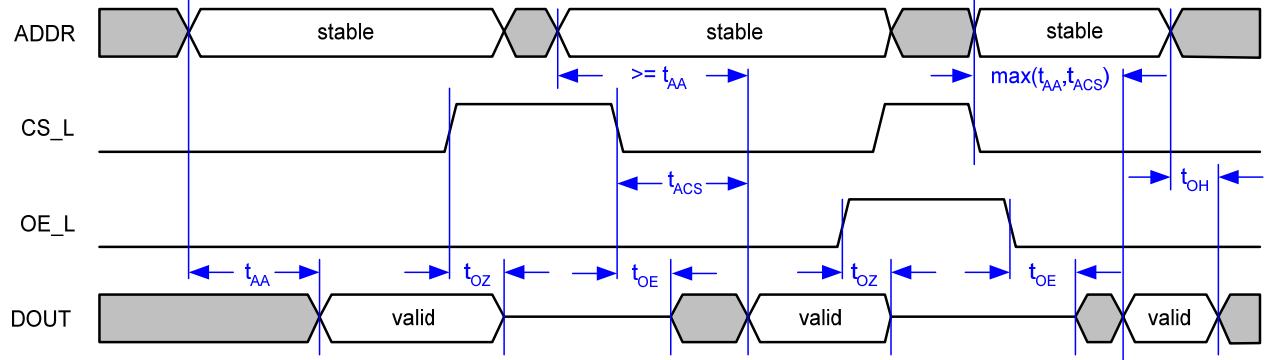

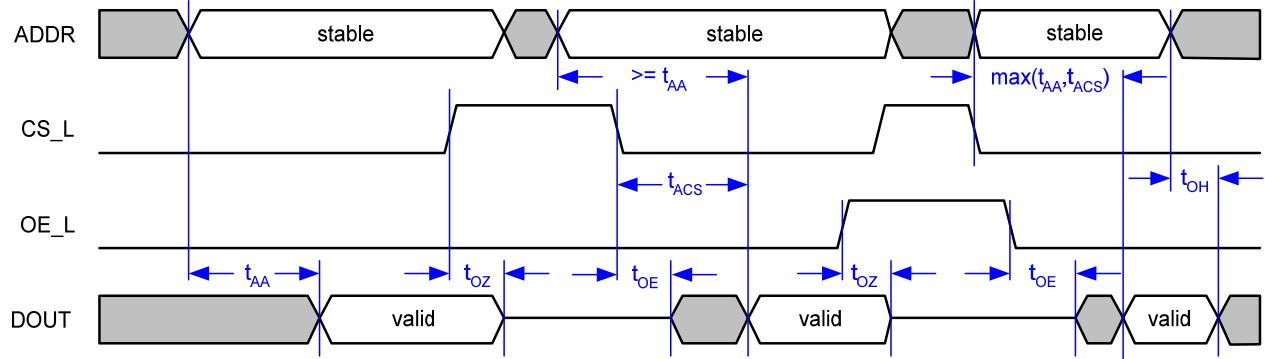

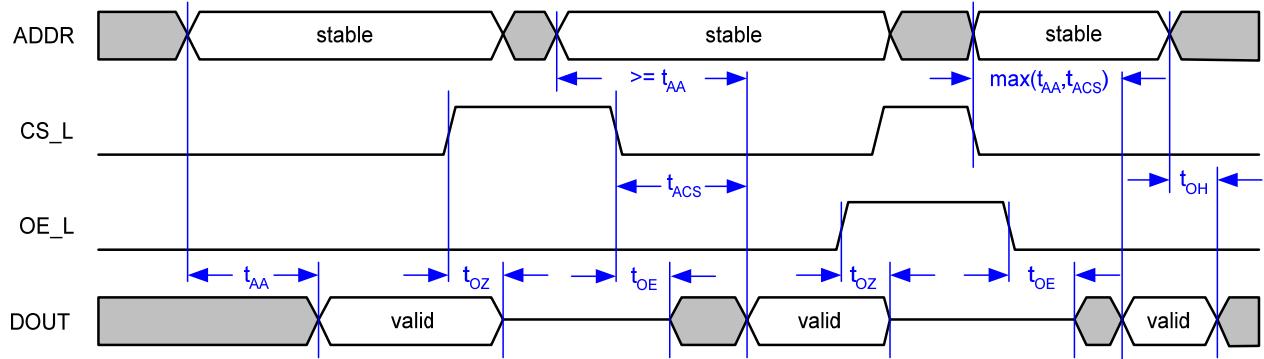

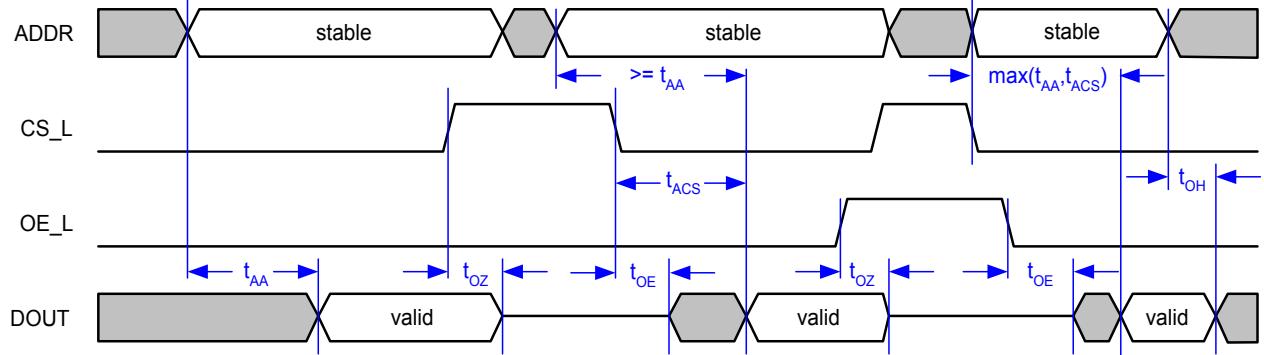

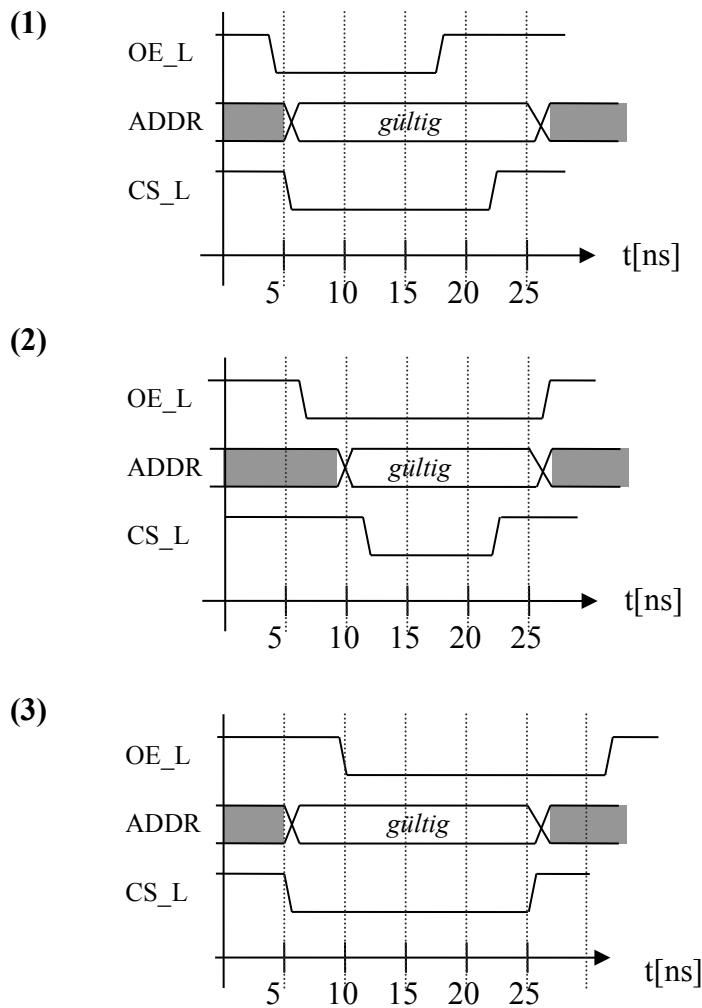

### Beispiel 2

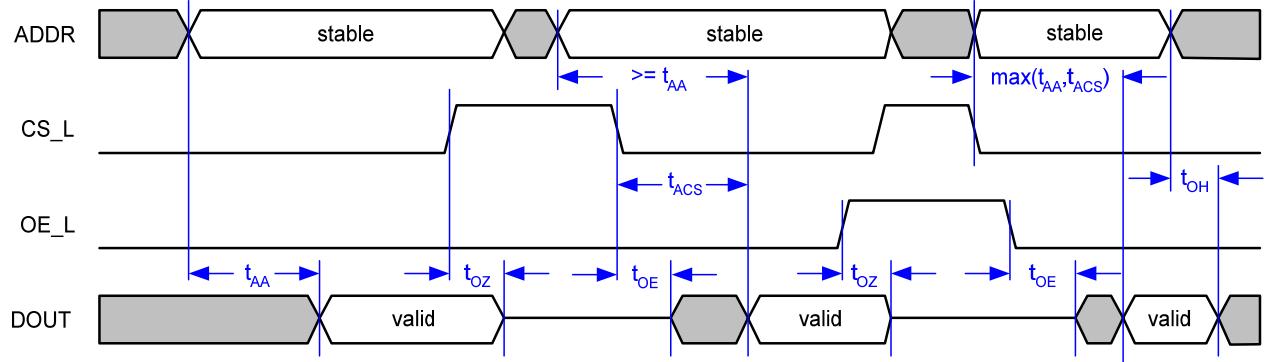

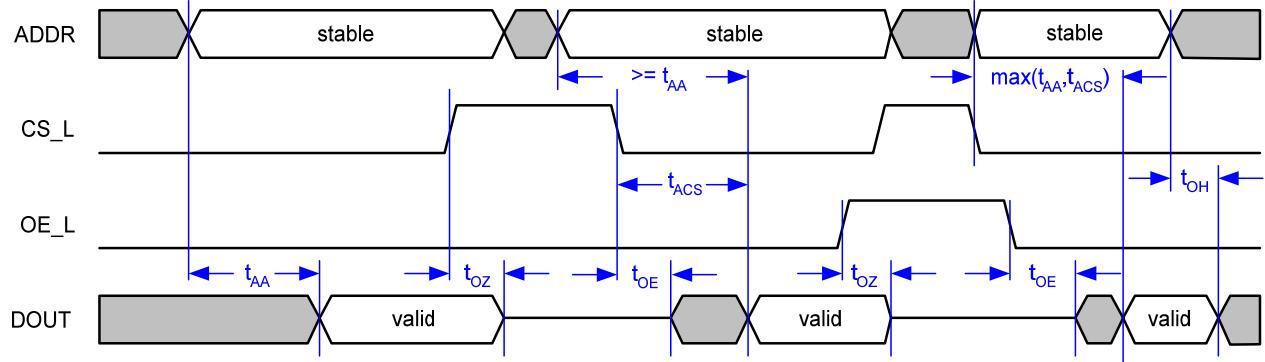

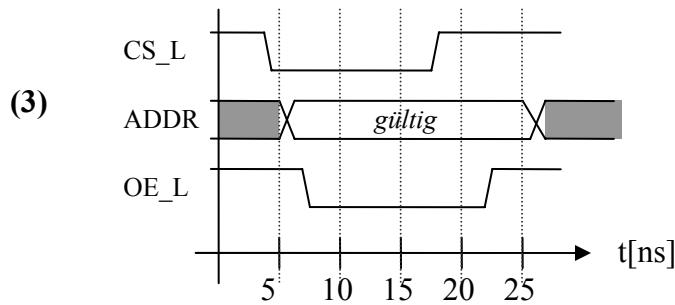

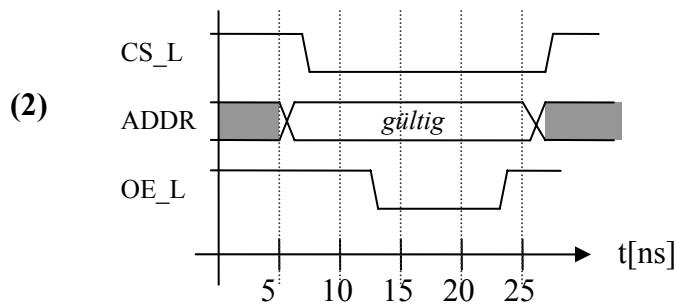

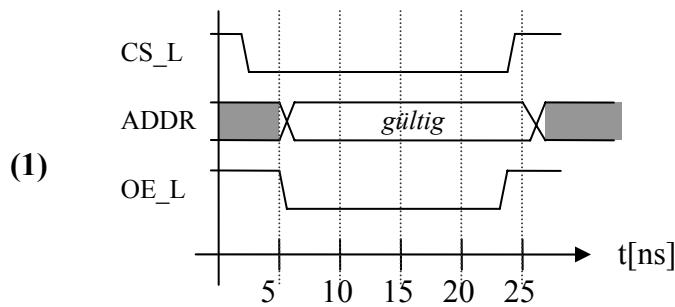

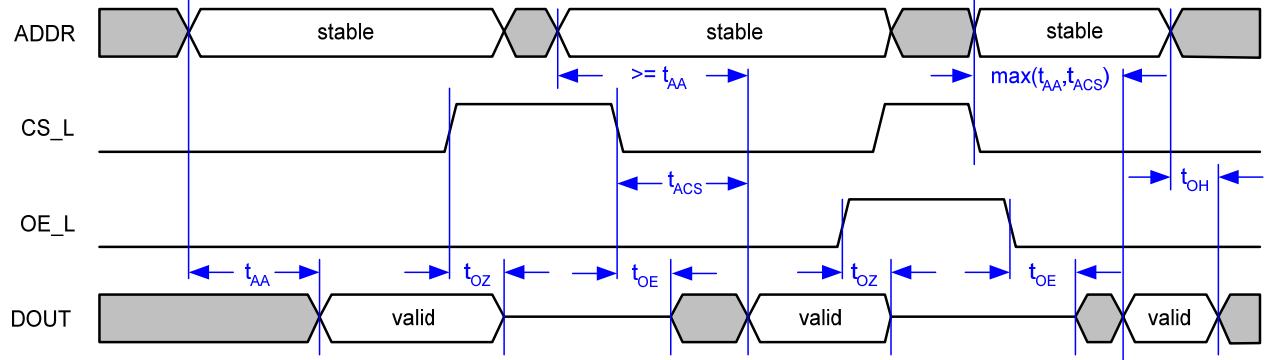

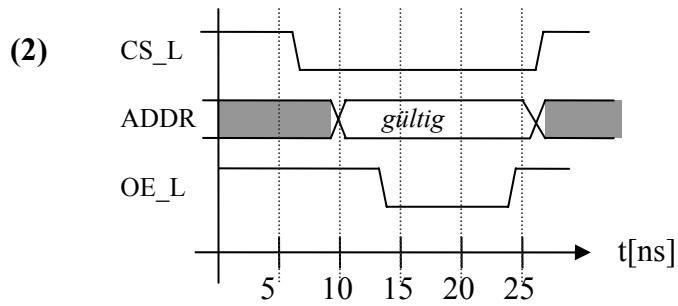

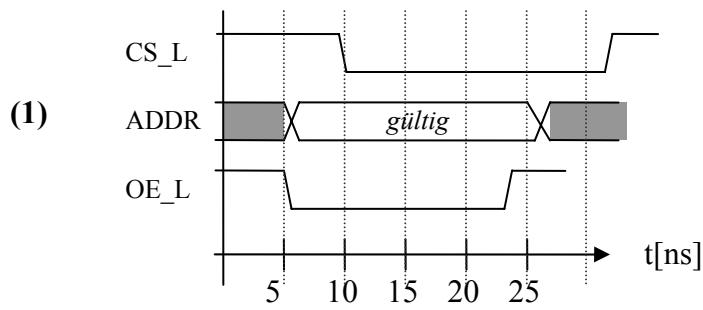

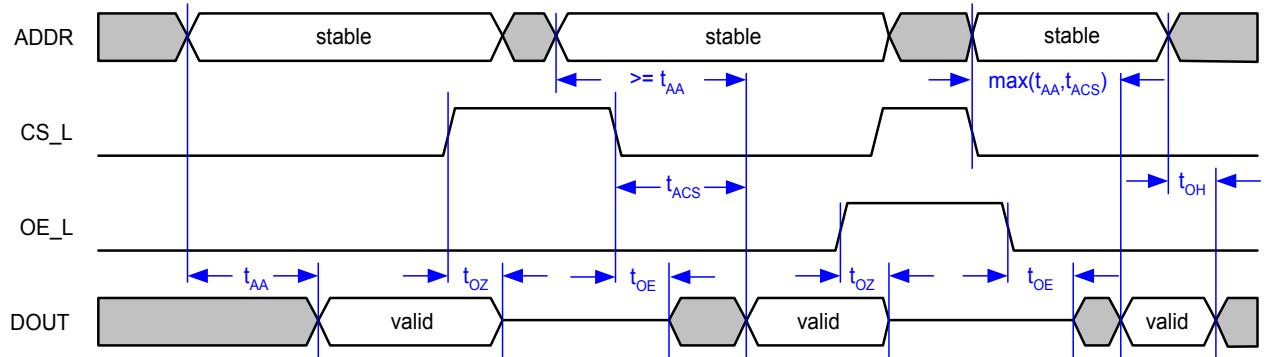

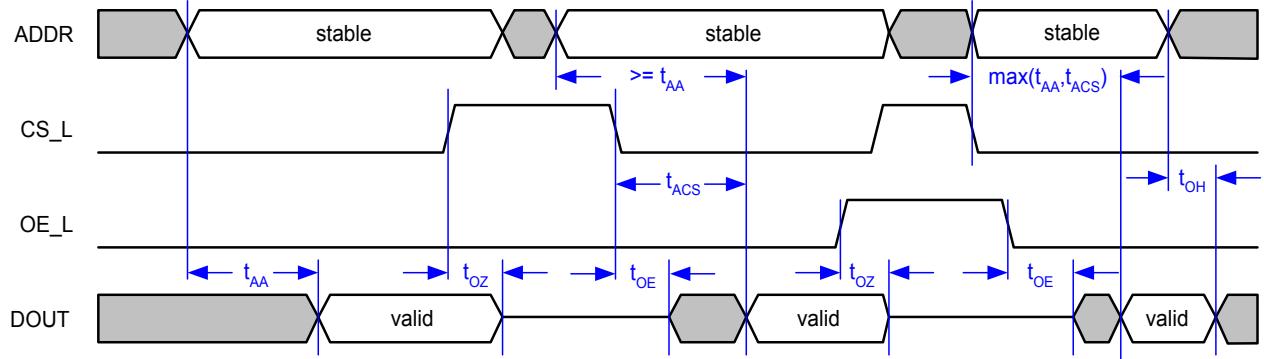

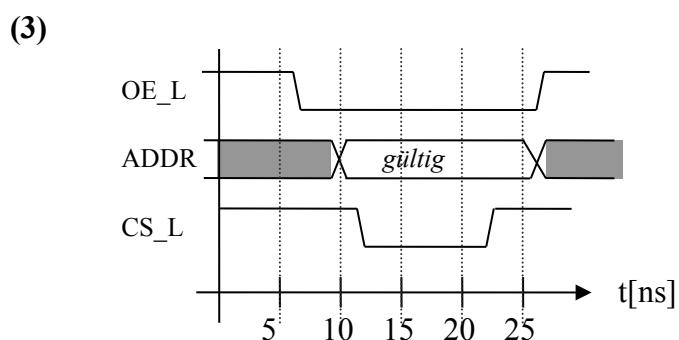

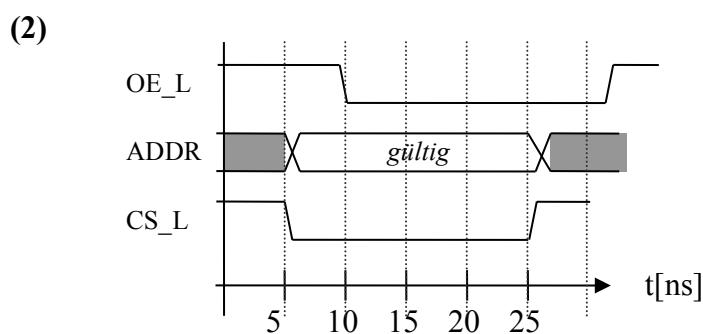

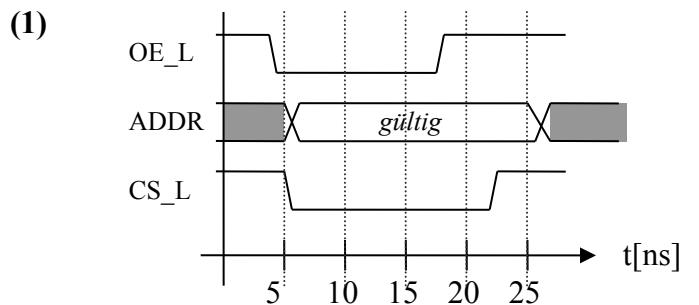

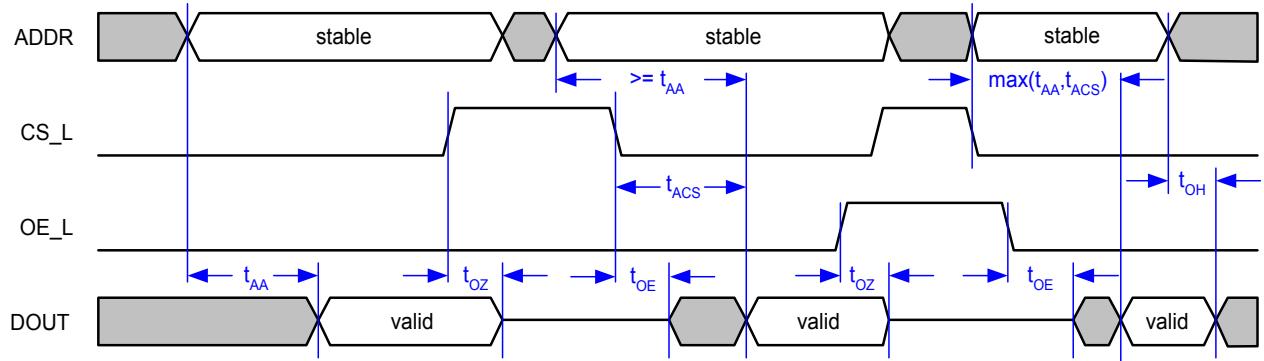

Gegeben ist ein SRAM mit Read-Timing nach folgendem Datenblatt (Abbildung 2.1)

$$t_{AA} = 15\text{ns}, t_{ACS} = 10\text{ns}, t_{OE} = 5\text{ns}$$

Abbildung 2.1

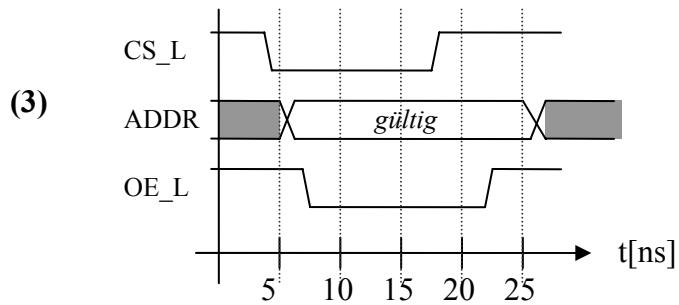

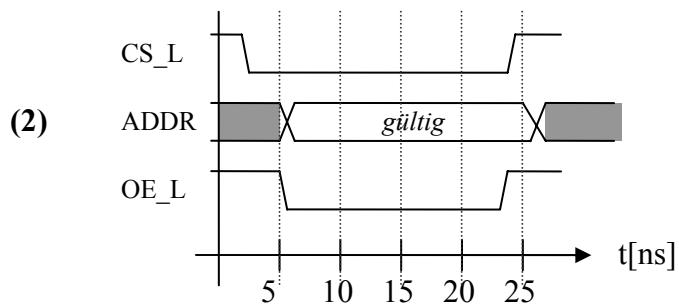

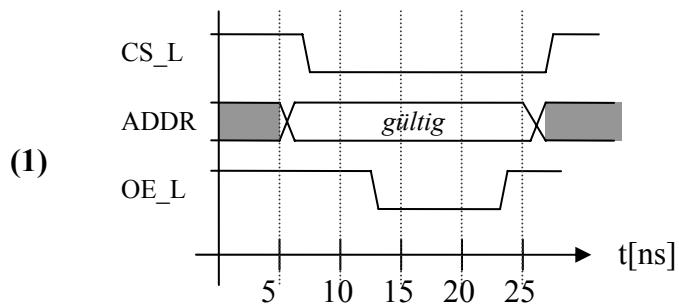

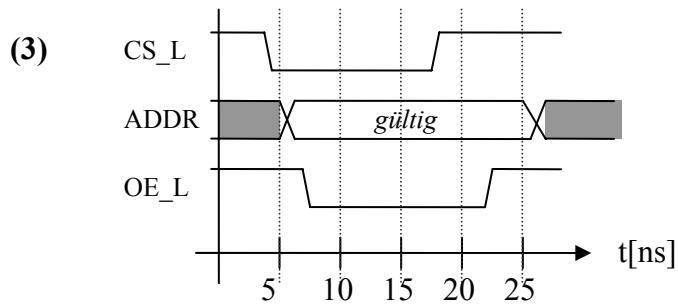

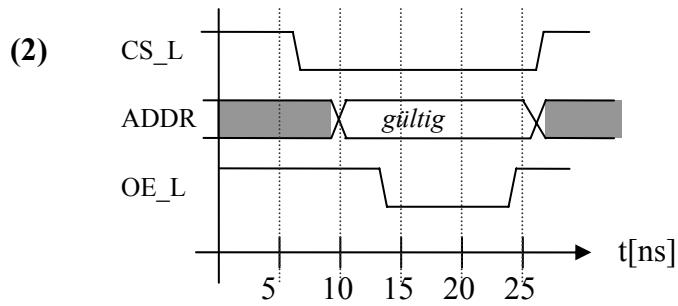

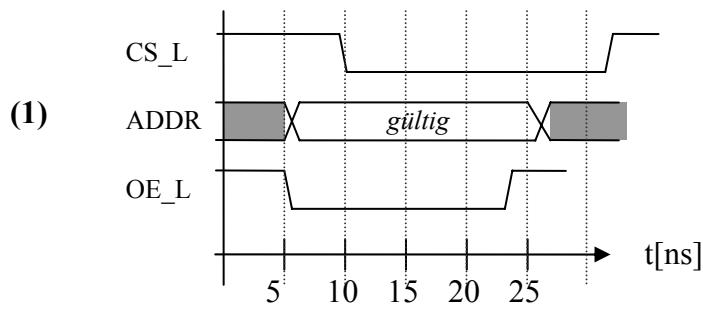

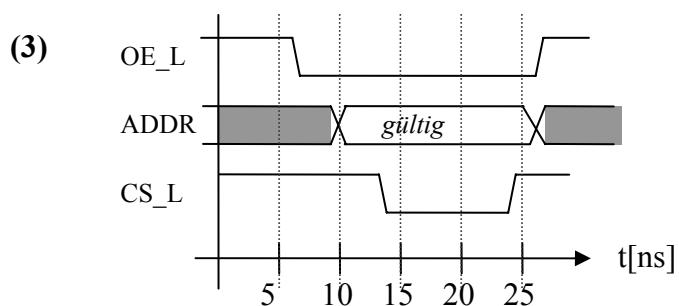

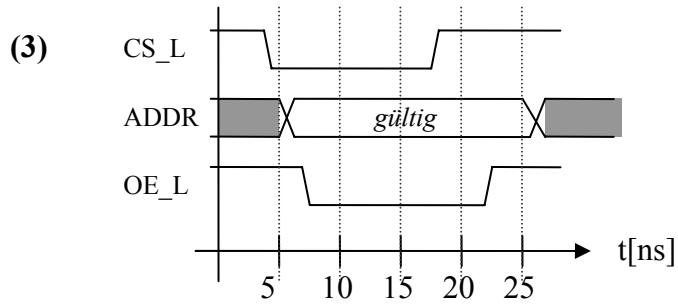

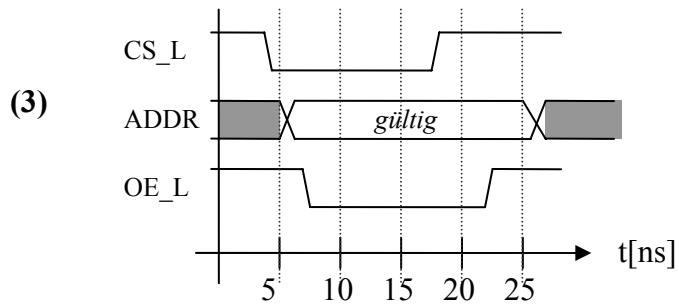

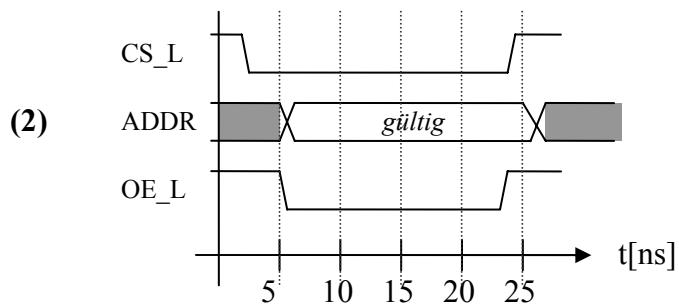

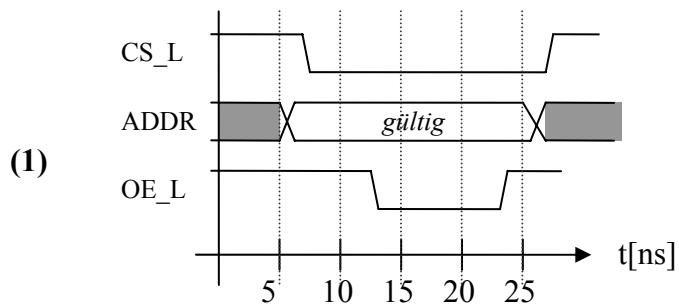

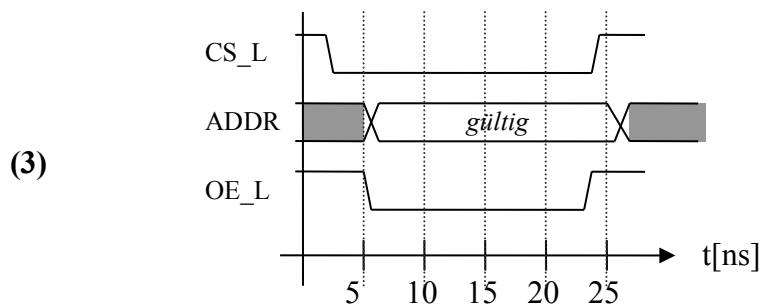

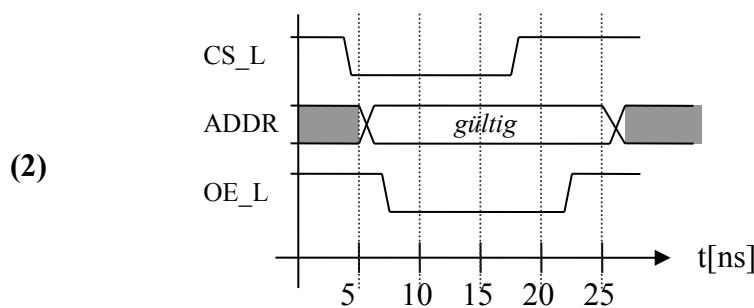

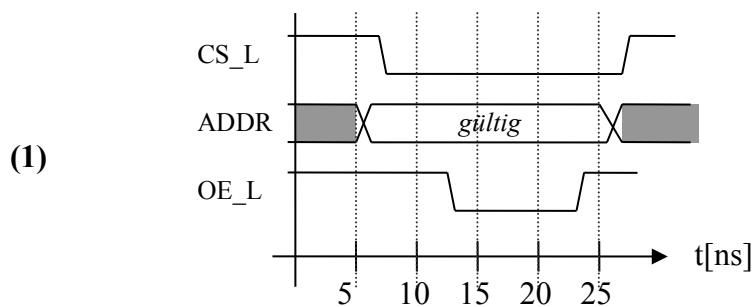

Gegeben sind weiters die Ausgangsmuster von drei State-Machines, die einen Zugriff auf dieses SRAM implementieren sollen (Abbildung 2.2).

- Geben Sie zu jeder Implementierung an, ob sie geeignet ist, einen gültigen Zugriff durchzuführen. Begründen Sie jeweils Ihre Antwort!

- Tragen Sie bei den korrekten Implementierungen den Zeitpunkt ein, ab dem auf die Daten zugegriffen werden kann!

- Machen Sie bei den mangelhaften Implementierungen einen Korrekturvorschlag: Welche Flanke müsste wie verschoben werden, damit der Zugriff gültig wird?

**Abbildung 2.2**

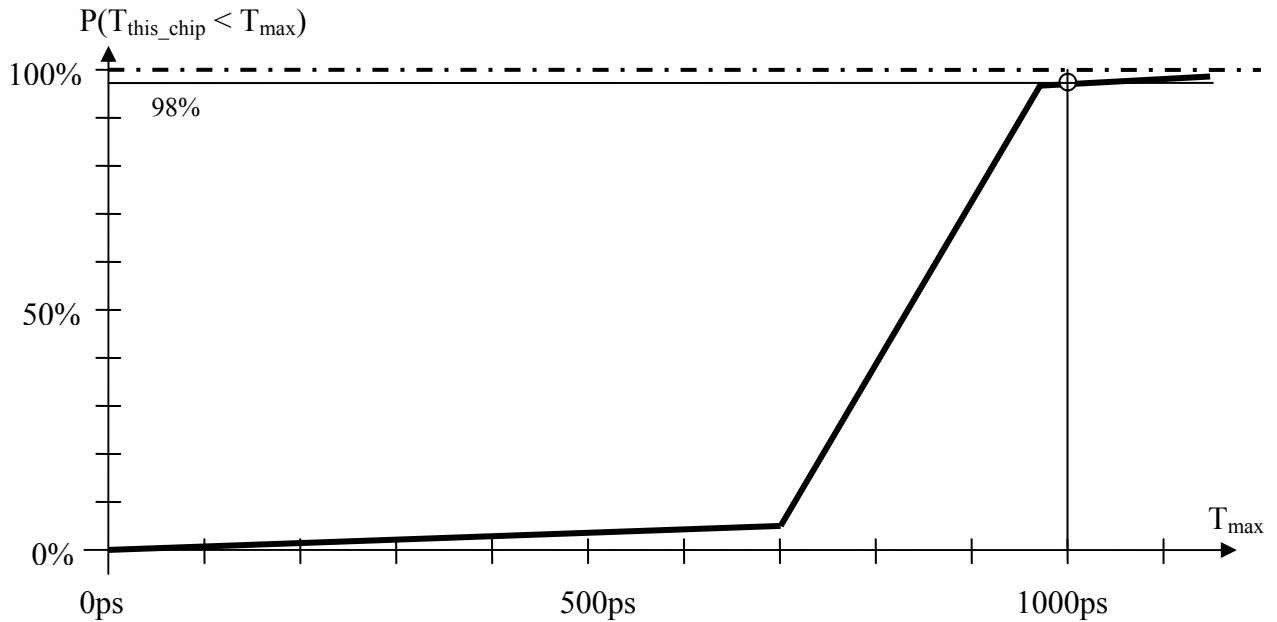

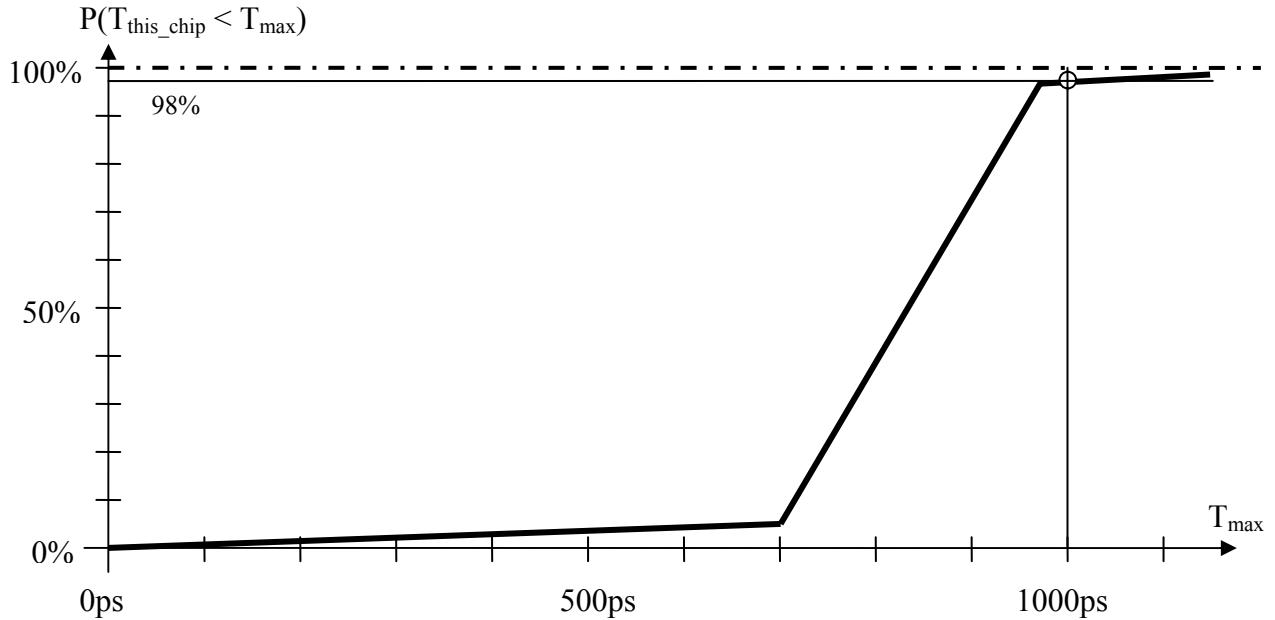

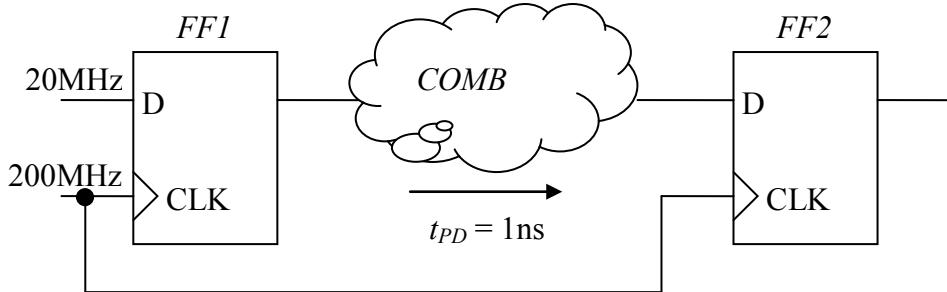

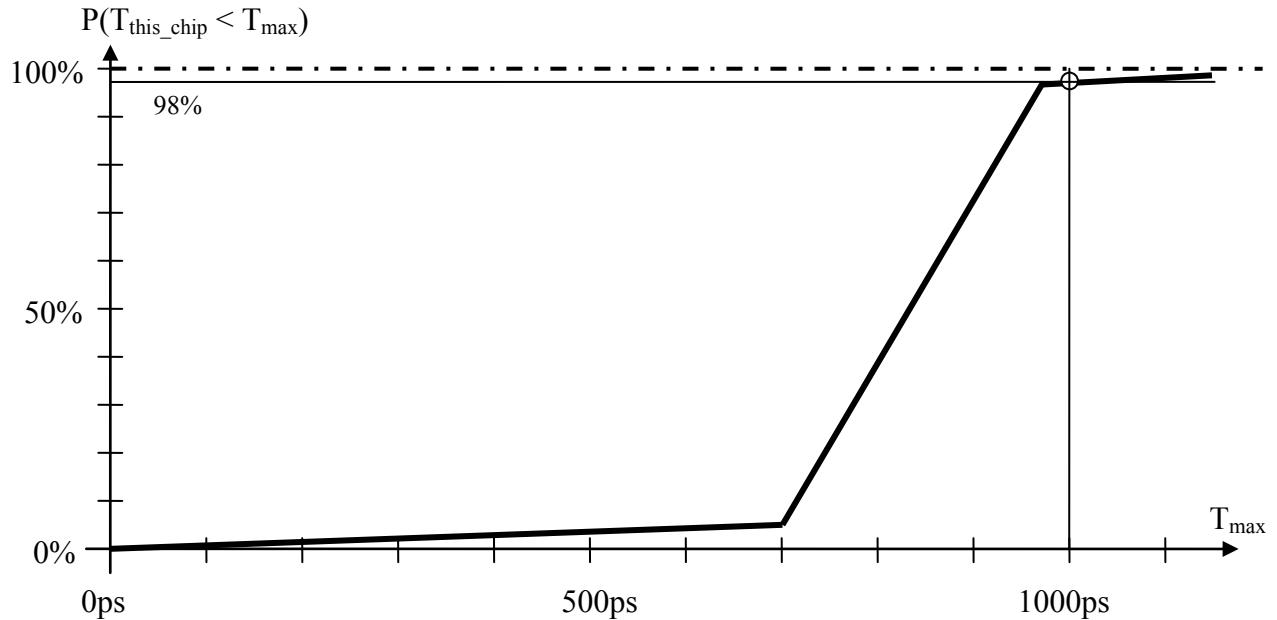

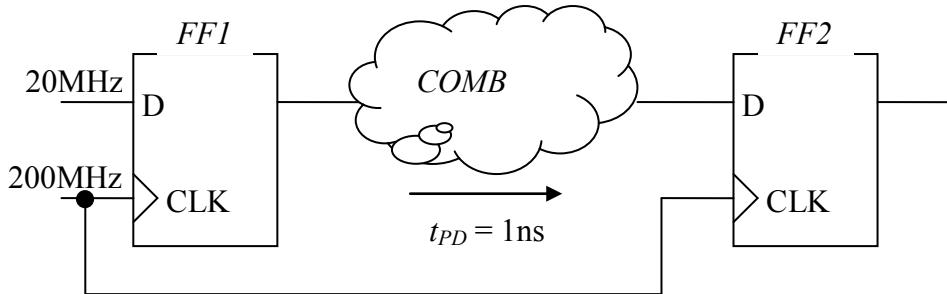

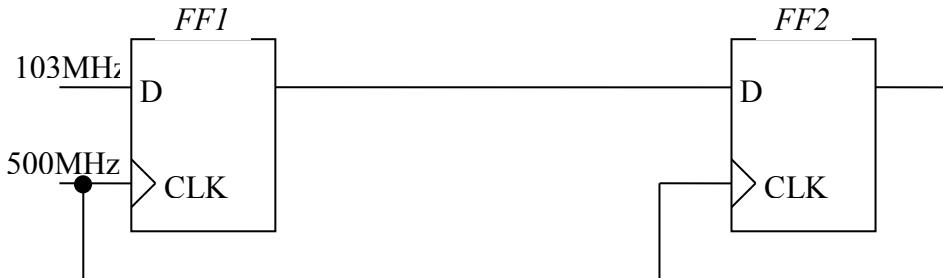

### Beispiel 3

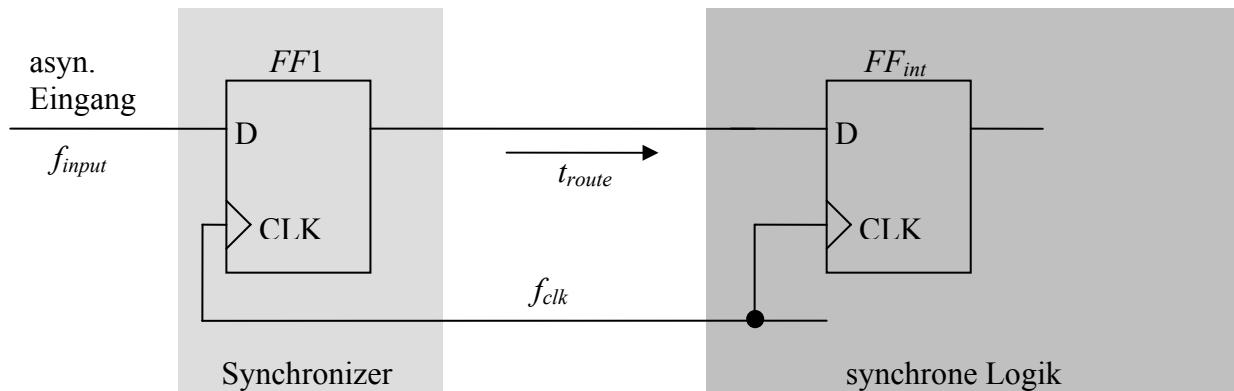

Gegeben ist die in Abbildung 3.1 dargestellte Schaltung mit 200MHz Takt. Ein asynchrones Eingangssignal mit 50kHz liegt am Eingang von Flip-Flop *FF1*. Der Ausgang von *FF1* geht über kombinatorische Logik *COMB* an den Eingang von Flip-Flop *FF2*. Die Verzögerungszeit der kombinatorischen Logik beträgt nominal 2ns. Laut Datenblatt haben die beiden Flip-Flops folgende Parameter:

$$t_{SU} = 1\text{ns} ; \quad \tau_C = 0,25\text{ns} ; \quad T_0 = 0,1\text{ns} .$$

- (a) Wann spricht man bei dieser Schaltung von einem „Upset“?

- (b) Welche MTBU ist bei Betrieb unter Nominal-Bedingungen zu erwarten?

Die Derating Factors für die kombinatorische Logik sind in Tabelle 3.1 gegeben.

- (c) Welche Temperatur und welche Betriebsspannung stellen nach dieser Tabelle den ungünstigsten Betriebsfall dar? Warum?

- (d) Welche Verzögerungszeit hat die kombinatorische Logik in diesem ungünstigsten Fall? Welche MTBU ergibt sich damit?

Abbildung 3.1

|      | 4.50 V | 4.75 V | 5.00 V | 5.25 V | 5.50 V |

|------|--------|--------|--------|--------|--------|

| -40° | 0.77   | 0.73   | 0.68   | 0.64   | 0.61   |

| 0°   | 1.00   | 0.93   | 0.87   | 0.82   | 0.78   |

| 25°  | 1.14   | 1.07   | 1.00   | 0.94   | 0.90   |

| 85°  | 1.50   | 1.40   | 1.33   | 1.26   | 1.20   |

| 100° | 1.60   | 1.49   | 1.41   | 1.34   | 1.28   |

| 125° | 1.76   | 1.65   | 1.56   | 1.47   | 1.41   |

Tabelle 3.1

## Beispiel 4

Ihr Chef gibt Ihnen den folgenden VHDL Code, den er auf dunklen Wegen von der Konkurrenz erschlichen hat. Ihre Aufgabe ist es nun, zu analysieren, wie das Produkt der Konkurrenz funktioniert:

```

library IEEE;

use     IEEE.std_logic_1164.all;

entity world is

port(

risk    : in std_logic;

gun     : in std_logic;

danger  : in std_logic;

love    : out std_logic

);

end world;

```

```

architecture man of world is

signal money, penny: std_logic;

DR_NO: process(gun, danger)

if gun = '0' then

money <= '0';

else

if danger'event and danger = '0' then

money <= penny;

end if;

end if;

end process DR_NO;

BOND: process(risk, money)

if risk = '1' then

love <= '0';

else

love <= money;

end if;

end process BOND;

OCTOPUSSY: process(risk, money)

if risk = '0' then

penny <= money;

else

penny <= NOT(money);

end if;

end process OCTOPUSSY;

end man;

```

- (a) Welches Signal entspricht dem Takt? Begründen Sie!

Ist die steigende oder die fallende Taktflanke die aktive?

- (b) Welches Signal entspricht dem Reset?

Handelt es sich um einen synchronen oder einen asynchronen Reset?

Ist der Reset HI-aktiv oder LO-aktiv? Begründen Sie!

- (c) Handelt es sich um eine State-Machine vom Moore-Type oder vom Mealy-Type?

Begründen Sie! Beschreiben Sie die Teilaufgaben der einzelnen Prozesse!

- (d) Beschreiben Sie die Funktion der Schaltung:

Welches Signal entspricht dem Eingang, welches dem Ausgang?

Was passiert mit dem Zustand und dem Ausgang wenn der Eingang auf '1' liegt, was bei Eingang '0'?

# Vorlesungsprüfung aus Digitales Design

12. Januar 2004

---

Die Arbeitszeit beträgt 2 Stunden. Als Hilfsmittel sind ausnahmslos Schreibzeug, Lineal und (nicht programmierbarer) Taschenrechner erlaubt. Schreiben Sie Ihre Antworten und Lösungen (incl. Lösungsweg!) mit dokumentechten Stiften (Füllfeder, Kugelschreiber, KEIN Bleistift!) und streichen Sie alles durch, was nicht zur Beurteilung herangezogen werden soll. Ein Abbruch der Prüfung nach Erhalt der Angaben führt in jedem Fall zu einer Beurteilung.

Tragen Sie Namen, Kennzahl und Matrikelnummer **zu Beginn** der Prüfung in die Tabelle ein und beschriften Sie jedes Blatt, das Sie abgeben möchten rechts oben mit Namen und Matrikelnummer.

|               |                 |

|---------------|-----------------|

| Familienname: | Vorname:        |

| Kennzahl:     | Matrikelnummer: |

Viel Erfolg!

**Die nachfolgende Tabelle nicht beschriften!**

| Beispiel       | Mögliche Punkte | Erhaltene Punkte |

|----------------|-----------------|------------------|

| Theoriefragen  | 50              |                  |

| Rechenbeispiel | 1               | 10               |

|                | 2               | 15               |

|                | 3               | 15               |

|                | 4               | 10               |

| Gesamt         | 100             |                  |

## Theoriefragen

**Frage 1:**

Welche Strecke legt eine elektromagnetische Welle auf einer Leitung innerhalb von 1ns zurück?

**Frage 2:**

Was versteht man unter einem „Flip-Chip“ ?

**Frage 3:**

Nennen Sie zwei Möglichkeiten, in CMOS einen Multiplexer zu realisieren!

**Frage 4:**

Nennen Sie drei typische Beispiele für Datenpfad-Elemente!

**Frage 5:**

Was versteht man unter „Refresh“? Bei welchem Speichertyp wird er benötigt? Warum?

**Frage 6:**

Kann man mit einer LUT mit 32 Bit *alle* Funktionen mit 5 Variablen realisieren? Begründen Sie!

**Frage 7:**

Was versteht man unter dem „Störspannungsabstand“?

**Frage 8:**

Erklären Sie Zweck und Prinzip des Burn-in!

**Frage 9:**

Was ist ein IDDQ-Test? Benötigt man dafür auch Testvektoren? Begründen Sie!

**Frage 10:**

Welche Zustände unterscheidet man bei der Null-Convention Logic?

## Rechenbeispiele

### Beispiel 1

Die folgende Funktion ist in Hardware zu realisieren:

$$Y = (\neg A \vee \neg B) \wedge (\neg A \vee \neg C)$$

- (a) Geben Sie die Wahrheitstabelle und das KV-Diagramm für diese Funktion an!

- (b) Vereinfachen Sie die Funktion bevor Sie die HW-Realisierung weiter planen!

- (c) Wenn Sie die Wahl zwischen einer Realisierung als AOI oder als OAI haben, was würden Sie bevorzugen? Begründen Sie!

- (d) Entwerfen Sie zunächst den n-Stack für Ihre bevorzugte Lösung!

- (e) Entwerfen Sie weiters den dazugehörigen p-Stack!

- (f) Stellen Sie die Realisierung der Gesamtlösung mittels FETs dar (Schaltbild)! Bezeichnen Sie Eingänge und Ausgang!

### Beispiel 2

Zu realisieren ist eine Schaltung, die von einer Zahl  $b$  die Restklasse Modulo 3  $y = b \bmod 3$  berechnet. Der Eingangswert  $b$  ist als positive Binärzahl  $(b_2, b_1, b_0)$  dargestellt, ebenso das Ergebnis  $y$ .

- (a) Beschreiben Sie eine Realisierung als ROM: Welches ROM benötigen Sie (Anzahl der Adressleitungen und der Speicherzellen, Wortbreite), wie beschalten Sie die Adressen, wie die Daten? Geben Sie eine Liste der Speicherinhalte an!

- (b) Gehen Sie von der Liste der Speicherinhalte aus (a) aus und beschreiben Sie für jedes Ausgangsbit  $y_i$  die logische Verknüpfung, die realisieren müssten, wenn Sie die Funktion mittels logischer Grundfunktionen realisieren wollten!

- (c) Leiten Sie eine Realisierung für die Funktion  $y_1(b_2, b_1, b_0)$  mittels Multiplexer-basierter Logik (wie im ACTEL-FPGA) her! Zeichnen Sie das Schaltbild Ihrer Lösung!

### Beispiel 3

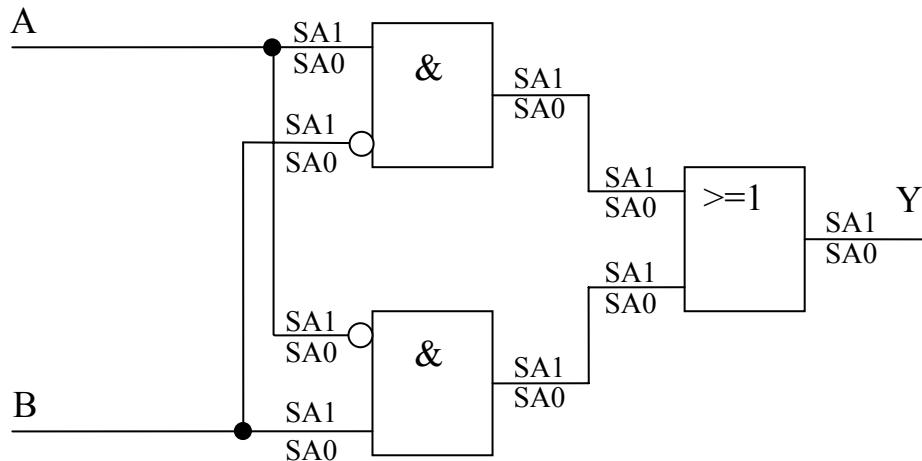

Gegeben ist die Schaltung in Abbildung 1. Arbeiten Sie mit dem single-Stuck-at Fehlermodell.

Abbildung 1

- Geben Sie Wahrheitstabelle und KV-Diagramm für diese Schaltung an!

Welche Grundfunktion erfüllt die Schaltung ?

- Wie viele Testvektoren benötigen Sie für einen Exhaustive Test dieser Schaltung?

Geben Sie die Vektoren an!

- In Abbildung sind alle möglichen Stuck-at Fehler eingetragen (SA0, SA1). Streichen Sie jene Fehler durch ein Kreuz durch („X“), die Sie aufgrund von Fehleräquivalenz nicht weiter zu berücksichtigen brauchen!

- Streichen Sie weiters jene Fehler durch einen einfachen Schrägstreich durch („/“), die Sie aufgrund von Fehlerdominanz nicht weiter zu berücksichtigen brauchen!

- Ermitteln Sie alle Testvektoren, die geeignet sind, den SA1-Fehler am Ausgang des oberen UND-Gatters zu erkennen! Beschreiben Sie die für die Ermittlung nötigen Schritte!

Ermitteln Sie ebenso alle Vektoren für SA1 am Ausgang des unteren UND-Gatters sowie für SA0 am Ausgang des OR-Gatters!

- Geben Sie einen minimalen Satz von Testvektoren an, der geeignet ist, alle in Abbildung 1 eingetragenen Fehler zu erkennen!

## Beispiel 4

Gegeben ist folgender VHDL-Code einer State-Machine:

```

library IEEE;

use      IEEE.std_logic_1164.all;

entity love is

port(

pink      : in std_logic;

panther : in std_logic;

popeye:out std_logic_vector(0 to 2)

);

end love;

```

```

architecture sea of love is

signal tom, jerry:

std_logic_vector(0 to 1);

begin

happy: process(tom)

begin

case tom is

when "00"  => jerry <= "01";

when "01"  => jerry <= "10";

when "10"  => jerry <= "11";

when others => jerry <= "00";

end case;

end process happy;

new: process(tom)

begin

case tom is

when "00"  => popeye <= "101";

when "01"  => popeye <= "001";

when "10"  => popeye <= "110";

when others => popeye <= "010";

end case;

end process new;

year: process(pink, panther)

begin

if panther = '0' then

tom <= "00";

else

if pink'event and pink = '1' then

tom <= jerry;

end if;

end if;

end process year;

end sea;

```

- Identifizieren Sie Taktsignal und Reset! Ist der Reset synchron oder asynchron?

- Nennen Sie die 3 Funktionsblöcke, die eine State-Machine stets umfassen muß? Welcher Process im obigen Code entspricht welchem Funktionsblock?

- Um welchen Typ von State-Machine (Moore oder Mealy) handelt es sich? Begründen Sie!

- Angenommen beim Process `year` fehlt das Signal `panther` in der Sensitivity List. Was würde sich dadurch ändern?

# Vorlesungsprüfung aus Digitales Design

16. Juni 2004

---

Die Arbeitszeit beträgt 2 Stunden. Als Hilfsmittel sind ausnahmslos Schreibzeug, Lineal und (nicht programmierbarer) Taschenrechner erlaubt. Schreiben Sie Ihre Antworten und Lösungen (incl. Lösungsweg!) mit dokumentechten Stiften (Füllfeder, Kugelschreiber, KEIN Bleistift!) und streichen Sie alles durch, was nicht zur Beurteilung herangezogen werden soll. Ein Abbruch der Prüfung nach Erhalt der Angaben führt in jedem Fall zu einer Beurteilung.

Tragen Sie Namen, Kennzahl und Matrikelnummer **zu Beginn** der Prüfung in die Tabelle ein und beschriften Sie jedes Blatt, das Sie abgeben möchten rechts oben mit Namen und Matrikelnummer.

|               |                 |

|---------------|-----------------|

| Familienname: | Vorname:        |

| Kennzahl:     | Matrikelnummer: |

Viel Erfolg!

**Die nachfolgende Tabelle nicht beschriften!**

| Beispiel       | Mögliche Punkte | Erhaltene Punkte |

|----------------|-----------------|------------------|

| Theoriefragen  | 50              |                  |

| Rechenbeispiel | 1               | 10               |

|                | 2               | 15               |

|                | 3               | 15               |

|                | 4               | 10               |

| Gesamt         | 100             |                  |

## Theoriefragen

**Frage 1:**

Was versteht man unter einem Maxterm?

**Frage 2:**

Welche Strecke legt eine elektromagnetische Welle auf einer Leitung innerhalb von 1ns zurück?

**Frage 3:**

Handelt es sich bei einem ROM um rein kombinatorische oder sequentielle Logik? Begründen Sie!

**Frage 4:**

Geben Sie die Signal-Resolution-Table für die Funktion OR und die Zustände {0,1,X} an!

**Frage 5:**

Was versteht man unter einem non-volatile Memory?

**Frage 6:**

Wie werden beim Gate-Array mittels lauter gleicher Zellen unterschiedliche Funktionen realisiert?

**Frage 7:**

Warum verursacht ein Scan-Test einen Overhead in der Chipfläche?

**Frage 8:**

Altert ein Chip auch wenn er nicht in Betrieb ist? Begründen Sie!

**Frage 9:**

Was ist ein Schmitt-Trigger-Eingang? Wozu wird er verwendet?

**Frage 10:**

Warum werden bei CMOS-Logik die Funktionen NAND und NOR bevorzugt verwendet und nur selten AND und OR?

## Rechenbeispiele

### Beispiel 1

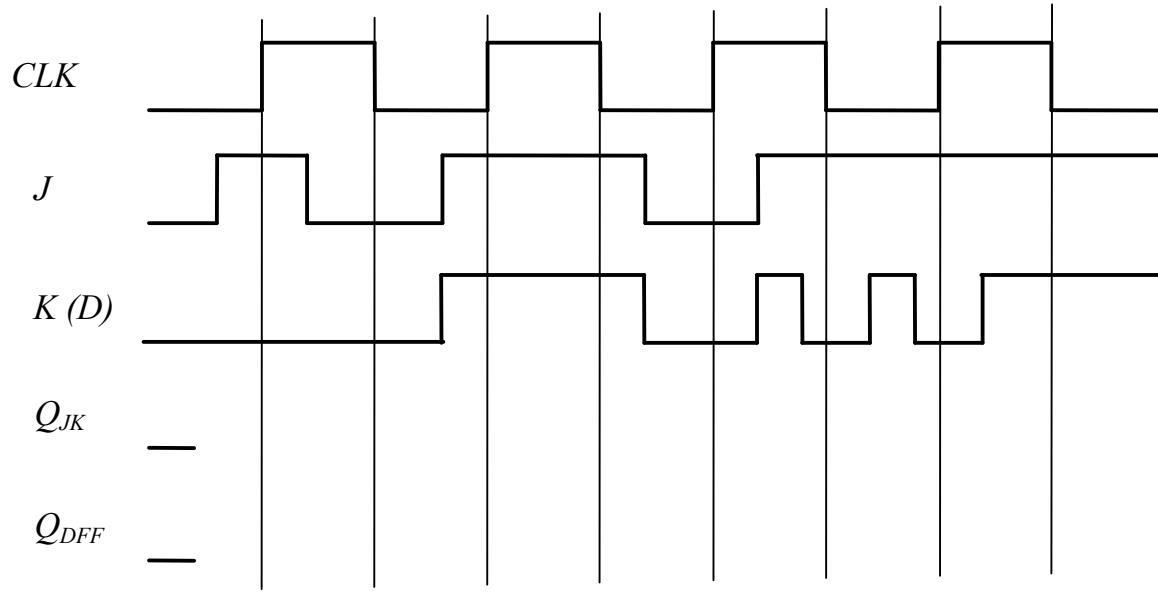

Gegeben sind die in Abbildung 1 dargestellten Signalverläufe für die Eingangssignale J und K und CLK eines JK-Flip-Flop.

Abbildung 1

(a) Tragen Sie in die Zeile  $Q_{JK}$  das zugehörige Ausgangssignal Q ein! Beschreiben Sie jeweils, in welcher Funktion das Flip-Flop gerade betrieben wird!

(b) Skizzieren Sie eine Schaltung, mit der Sie unter Verwendung eines JK-Flip-Flop die Frequenz eines Taktsignals CLK halbieren!

(c) Interpretieren Sie nun die Signale CLK als Takt und K als D-Eingang eines D-Flipflop (J hat hier keine Verwendung). Zeichnen Sie wieder das zugehörige Ausgangssignal in die Zeile  $Q_{DFF}$ !

## Beispiel 2

Das in Abbildung 2 dargestellte Feedback Gate realisiert eine logische Verknüpfung in Null-Convention Logic (NCL).

| a | N |   |   | F |   |   | T |   |   | N |   |   | F |   |   | T |   |   | N |   |   | F |   |   | T |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| b | N |   | F | T |   | N | F | T | N | F | T | N | F | T | N | F | T | N | F | T | N | F | T | N | F | T |   |

| y | N | F | T | N | F | T | N | F | T | N | F | T | N | F | T | N | F | T | N | F | T | N | F | T | N | F | T |

| Y | N | N | N | N | F | T | N | F | T | N | F | T | F | F | F | F | F | F | N | F | T | T | T | T | F | F | F |

**Abbildung 2**

(a) Die Eingänge (a,b) der Schaltung durchlaufen folgende Sequenz:

(F,F)

(F,N)

(N,N)

(N,T)

(F,T)

(N,T)

(F,T)

Geben Sie neben jedem Eingangswort jeweils den zugehörigen Ausgang an!

- (b) Kennzeichnen Sie in Abbildung 1 alle instabilen Zustände (Spalten in der Tabelle), also jene, in denen die Schaltung sich nur vorübergehend befinden kann, durch ein „x“ unter der jeweiligen Spalte.

- (c) Welche logische Verknüpfung von a und b wird durch die Schaltung realisiert?

- (d) Welche Einträge müsste man ändern, um aus der Schaltung die Verknüpfung  $Y=a \text{ XOR } b$  zu machen? (Rahmen Sie die zu ändernden Einträge in der Tabelle ein und geben Sie die neuen Einträge an)

- (e) Welchen Zweck hat die Rückkopplung für die Realisierung der NCL-Schaltung?

### Beispiel 3

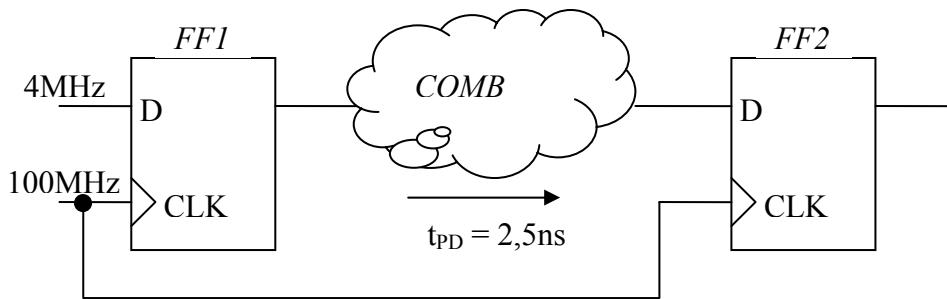

Gegeben ist die in Abbildung 3 dargestellte Schaltung mit 100MHz Takt. Ein asynchrones Eingangssignal mit 2MHz liegt am Eingang von Flip-Flop  $FF1$ . Der Ausgang von  $FF1$  geht über kombinatorische Logik  $COMB$  an den Eingang von Flip-Flop  $FF2$ . Die Verzögerungszeit der kombinatorischen Logik beträgt 2ns. Laut Datenblatt haben die beiden Flip-Flops folgende Parameter:

$$t_{SU} = 1\text{ns} ; \quad \tau_C = 0,2\text{ns} ; \quad T_0 = 0,1\text{ns} .$$

Abbildung 3

- (a) Welche MTBU ist zu erwarten ?

- (b) Die Testabteilung schreibt nun vor, dass vor die D-Eingänge der beiden Flipflops jeweils ein Multiplexer geschaltet werden muss. Welchen Grund wird die Testabteilung dafür haben?

- (c) Die Multiplexer verursachen im Datenpfad ein Delay von 2ns. Welche MTBU ergibt sich nun?

- (d) Auf welchen Wert müssten Sie die Frequenz des asynchronen Eingangssignals verringern, um wieder die ursprüngliche MTBU zu erreichen?

## Beispiel 4

Gegeben ist folgender VHDL-Code einer State-Machine:

```

library IEEE;

use      IEEE.std_logic_1164.all;

entity championship is

port(

italy:  in std_logic;

france : in std_logic;

germany: out std_logic_vector(0 to 2)

);

end championship;

```

```

architecture leader of championship is

signal cyprus, greece:

std_logic_vector(0 to 1);

begin

corner: process(cyprus)

begin

case cyprus is

when "10"  => greece <= "00";

when "11"  => greece <= "10";

when "01"  => greece <= "11";

when others => greece <= "11";

end case;

end process corner;

foul: process(cyprus)

begin

case cyprus is

when "00"  => germany <= "101";

when "11"  => germany <= "000";

when "10"  => germany <= "111";

when others => germany <= "010";

end case;

end process foul;

goal: process(italy, france)

begin

if france = '0' then

cyprus <= "00";

else

if italy'event and italy = '1' then

cyprus <= greece;

end if;

end if;

end process goal;

end leader;

```

- Identifizieren Sie Taktsignal und Reset! Ist der Reset synchron oder asynchron? Begründen Sie!

- Nennen Sie die 3 Funktionsblöcke, die eine State-Machine stets umfassen muß? Welcher Process im obigen Code entspricht welchem Funktionsblock?

- Wie viele Bit umfasst der Ausgang dieser Schaltung? Begründen Sie!

- Wie viele interne Zustände nimmt die State-Machine im Betrieb ein? In welcher Reihenfolge werden sie ausgehend vom Reset durchlaufen?

# Vorlesungsprüfung aus Digitales Design

17. November 2004

---

Die Arbeitszeit beträgt 2 Stunden. Als Hilfsmittel sind ausnahmslos Schreibzeug, Lineal und (nicht programmierbarer) Taschenrechner erlaubt. Schreiben Sie Ihre Antworten und Lösungen (incl. Lösungsweg!) mit dokumentechten Stiften (Füllfeder, Kugelschreiber, KEIN Bleistift!) und streichen Sie alles durch, was nicht zur Beurteilung herangezogen werden soll. Ein Abbruch der Prüfung nach Erhalt der Angaben führt in jedem Fall zu einer Beurteilung.

Tragen Sie Namen, Kennzahl und Matrikelnummer **zu Beginn** der Prüfung in die Tabelle ein und beschriften Sie jedes Blatt, das Sie abgeben möchten rechts oben mit Namen und Matrikelnummer.

|               |                 |

|---------------|-----------------|

| Familienname: | Vorname:        |

| Kennzahl:     | Matrikelnummer: |

Viel Erfolg!

**Die nachfolgende Tabelle nicht beschriften!**

| Beispiel       | Mögliche Punkte | Erhaltene Punkte |

|----------------|-----------------|------------------|

| Theoriefragen  | 50              |                  |

| Rechenbeispiel | 1               | 10               |

|                | 2               | 10               |

|                | 3               | 15               |

|                | 4               | 15               |

| Gesamt         | 100             |                  |

## Theoriefragen

**Frage 1:**

Skizzieren Sie die Prinzipschaltung eines D-Latch!

**Frage 2:**

Warum eignet sich Silizium besonders gut für die Herstellung integrierter Schaltungen?

**Frage 3:**

Was ist der Vorteil von BiCMOS-Logik?

**Frage 4:**

Was ist der Unterschied zwischen Floorplanning und Partitionierung?

**Frage 5:**

Was ist ein OTP-ROM?

**Frage 6:**

Wie werden beim Gate-Array mittels lauter gleicher Zellen unterschiedliche Funktionen realisiert?

**Frage 7:**

Nennen Sie drei Faktoren, von denen der thermische Widerstand eines Gehäuses abhängt!

**Frage 8:**

Wovon hängt das Ausmaß der Electromigration ab?

**Frage 9:**

Warum wendet man beim BIST das Prinzip des nondeterministic Testing an?

**Frage 10:**

Was versteht man unter einem „Hazard“?

## Rechenbeispiele

### Beispiel 1

Gegeben ist das KV-Diagramm einer logischen Funktion lt. Abbildung 1.1:

|          |     | $\neg C$ | $C$ | $\neg C$ |     |

|----------|-----|----------|-----|----------|-----|

|          |     | 0        | 1   | 0        | 0   |

|          |     | 0        | 1   | 1        | 0   |

|          |     | 0        | 0   | 1        | 0   |

|          |     | 0        | 0   | 1        | 1   |

|          |     |          |     | $\neg D$ | $D$ |

| $\neg A$ | $A$ |          |     | $\neg B$ | $B$ |

Abbildung 1.1

(a) Geben Sie die zugehörige logische Funktion als konjunktive Normalform an!

(b) Beschreiben Sie, wie Sie diese Funktion mittels eines ROM realisieren würden:

Wie viele Adressleitungen benötigen Sie?

Welche Signale schließen sie daran an?

Welche Speichergröße benötigen Sie?

Geben Sie zu jeder ROM-Adresse den zugehörigen Speicherinhalt an!

(c) Leiten Sie eine Realisierung für die Funktion mittels Multiplexer-basierter Logik her! Zeichnen Sie das Schaltbild Ihrer Lösung!

## Beispiel 2

An einem Chip messen Sie bei einer Versorgungsspannung von  $V_{DD}=3,25\text{V}$  einen mittleren Strom von 4A. Im Datenblatt finden Sie für das Gehäuse folgende Angabe:

$$\theta_{JC} = 2\text{K/W}$$

$\theta_{JA} = 4\text{K/W}$  für Betrieb ohne Kühlkörper.

- (a) Welche Temperatur  $T_J$  erreicht der Die im Betrieb bei  $T_{AMB}=25^\circ\text{C}$ ?

- (b) Angenommen Sie erhöhen für einen Burn-in dieses Chips die Versorgungsspannung auf  $V_{DD} = 4,0\text{V}$ . Welche Temperatur  $T_J$  erreicht der Die nun?

(Nehmen Sie an, die Verlustleistung sei durch Ladeströme dominiert)

- (c) Bestimmen Sie Temperature Acceleration Factor  $AF_T$  und Voltage Acceleration Factor  $AF_V$  für den Betrieb bei  $V_{DD} = 4,0\text{V}$  und  $T_{AMB} = 25^\circ\text{C}$  gegenüber einem Normalbetrieb bei  $V_{DD} = 3,25\text{V}$  und  $T_{AMB} = 25^\circ\text{C}$ !

$k = 8,6 \cdot 10^{-5} \text{ eV/K}$  ;  $E_{act} = 0,7 \text{ eV}$  ;  $\gamma = 3,2 \text{ V}^{-1}$

- (d) Angenommen, Sie wollen erreichen, dass der Chip beim Burn-in innerhalb von 36 Stunden um 1 Jahr altert (als Normalbetrieb gilt wieder  $T_{AMB} = 25^\circ\text{C}$ ;  $V_{DD} = 3,25\text{V}$ ).

Welchen Acceleration Factor  $AF$  benötigen Sie insgesamt?

Welcher Temperature Acceleration Factor  $AF_T$  ist nun erforderlich ( $V_{DD}$  ist weiterhin 4,0V)?

Bei welcher Die-Temperatur  $T_J$  und welcher Umgebungstemperatur  $T_{AMB}$  muss man den Chip dafür betreiben?

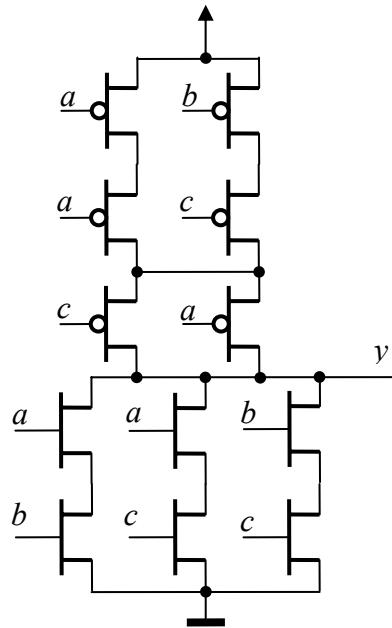

### Beispiel 3

Gegeben ist die Schaltung in Abbildung 3.1. Arbeiten Sie mit dem single-Stuck-at Fehlermodell.

**Abbildung 3.1**

- Geben Sie Wahrheitstabelle und KV-Diagramm für die Schaltung in Abbildung 3.1 an!

Leiten Sie aus dem Schaltbild die logische Funktion dieser Schaltung ab, und versuchen Sie diese durch Umformungen zu vereinfachen.

- Wie viele Testvektoren benötigen Sie für einen Exhaustive Test dieser Schaltung?

Geben Sie die Vektoren an!

- In Abbildung 3.1 sind alle möglichen Stuck-at Fehler eingetragen (SA0, SA1). Streichen Sie jene Fehler durch ein Kreuz durch („X“), die Sie aufgrund von Fehleräquivalenz nicht weiter zu berücksichtigen brauchen!

- Streichen Sie weiters jene Fehler durch einen einfachen Schrägstreich durch („/“), die Sie aufgrund von Fehlerdominanz nicht weiter zu berücksichtigen brauchen!

- Ermitteln Sie alle Testvektoren, die geeignet sind, den SA1-Fehler am Ausgang des UND-Gatters zu erkennen! Beschreiben Sie die für die Ermittlung nötigen Schritte!

- Wiederholen Sie (e), diesmal jedoch für einen SA0-Fehler am Ausgang des UND-Gatters.

Was ist nun anders? Begründen Sie!

- Geben Sie einen minimalen Satz von Testvektoren an, der geeignet ist, möglichst viele der in Abbildung 3.1 eingetragenen Fehler zu erkennen!

## Beispiel 4

Gegeben ist folgender VHDL-Code einer State-Machine:

```

library IEEE;

use     IEEE.std_logic_1164.all;

use     IEEE.std_logic_UNSIGNED.all;

entity glass is

port(

beat  : in std_logic;

energy : in std_logic;

polka : out std_logic;

waltz : out std_logic;

tango : out std_logic_vector(0 to 3)

);

end glass;

```

```

architecture heart of glass is

signal girl, boy:

std_logic_vector(0 to 1);

begin

ball: process(girl)

begin

case girl is

when "00"  => boy <= "01";

when "01"  => boy <= "10";

when "10"  => boy <= "11";

when others => boy <= "00";

end case;

end process ball;

contest: process(girl, energy)

variable chacha: std_logic_vector(0 to 3);

begin

if energy = '0' then

chacha := "0000";

end if;

case girl is

when "10"  => polka <= '1';

waltz  <= '1';

when "01"  => polka <= '0';

chacha := chacha + '1';

waltz  <= '1';

when others => polka <= '0';

waltz  <= '0';

end case;

tango <= chacha;

end process contest;

party: process(beat, energy)

begin

if energy = '0' then

girl <= "00";

else

if beat'event and beat = '1' then

girl <= boy;

end if;

end if;

end process party;

end heart;

```

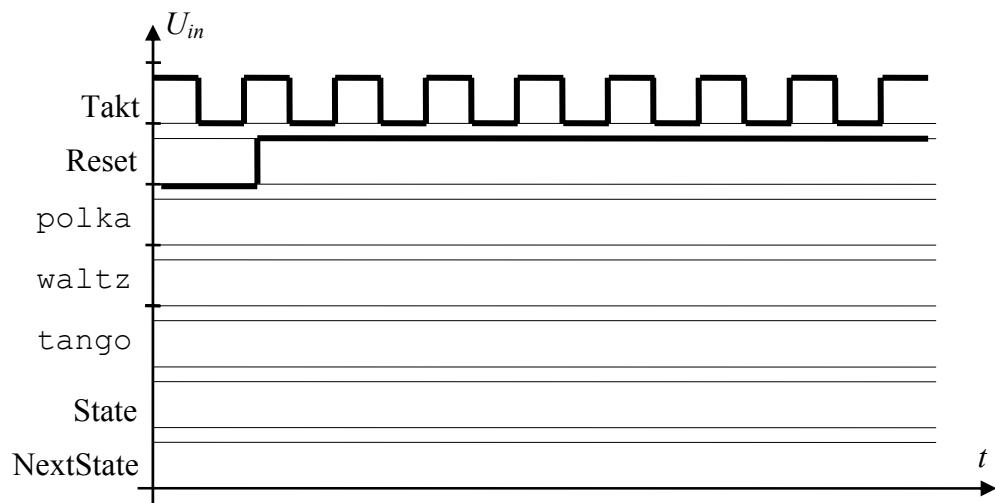

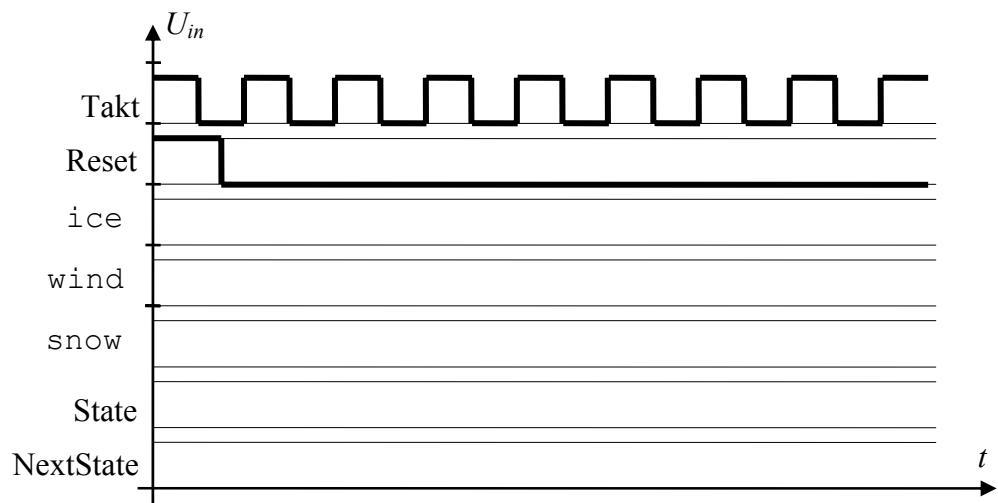

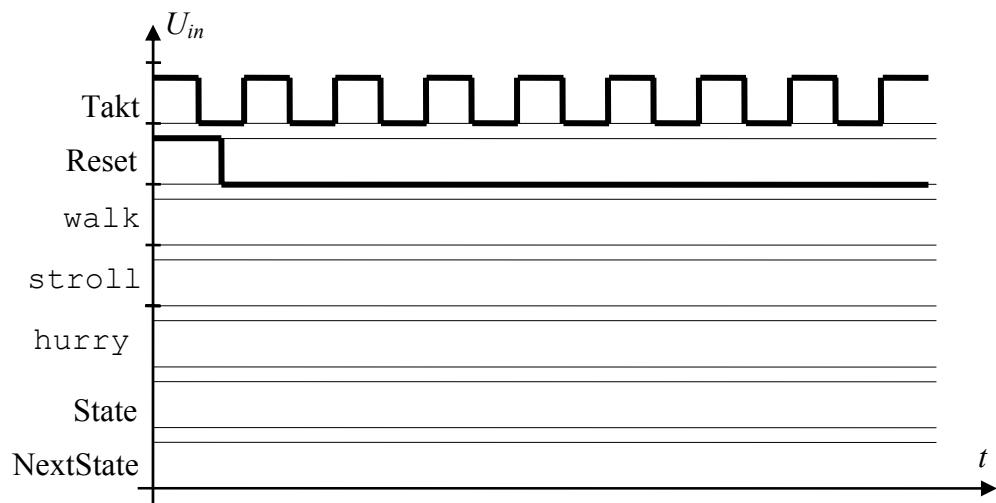

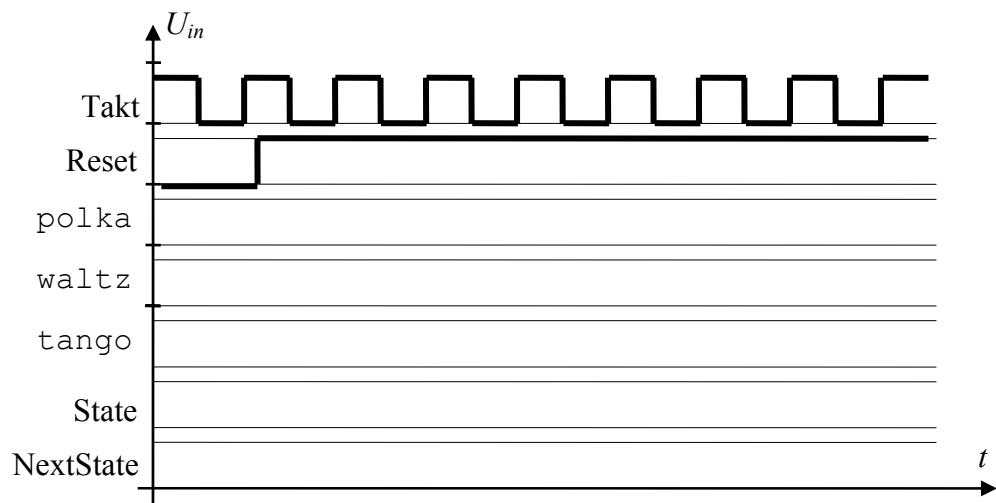

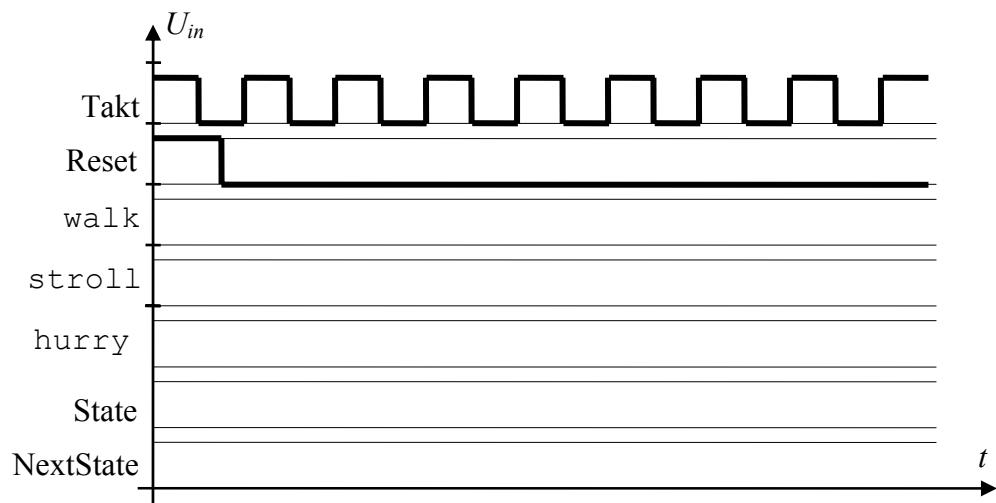

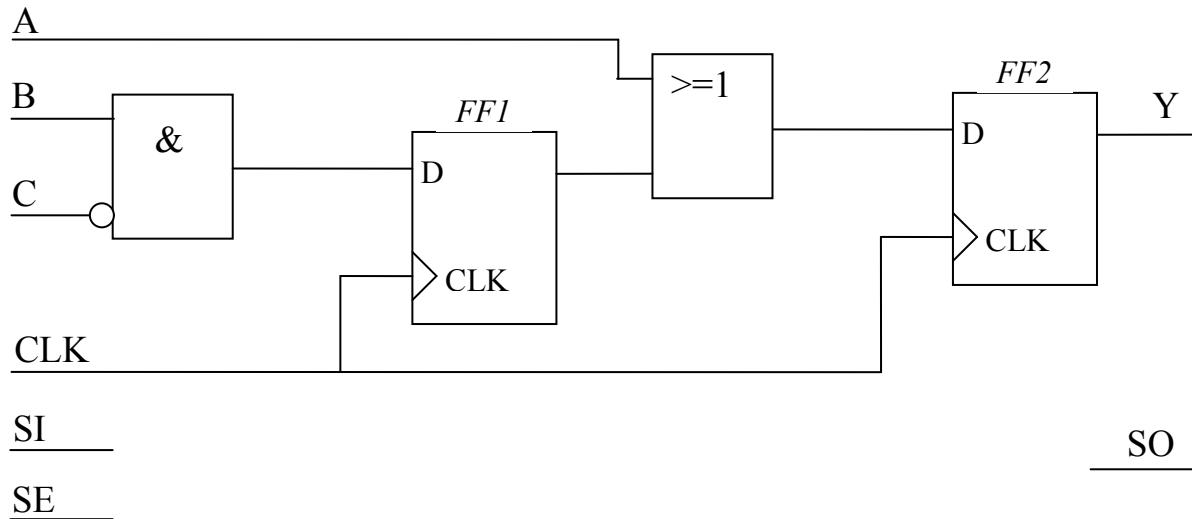

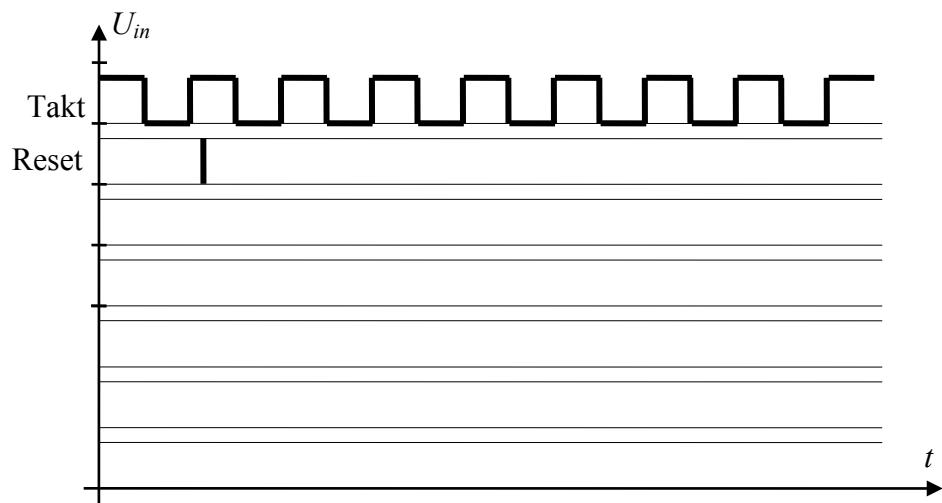

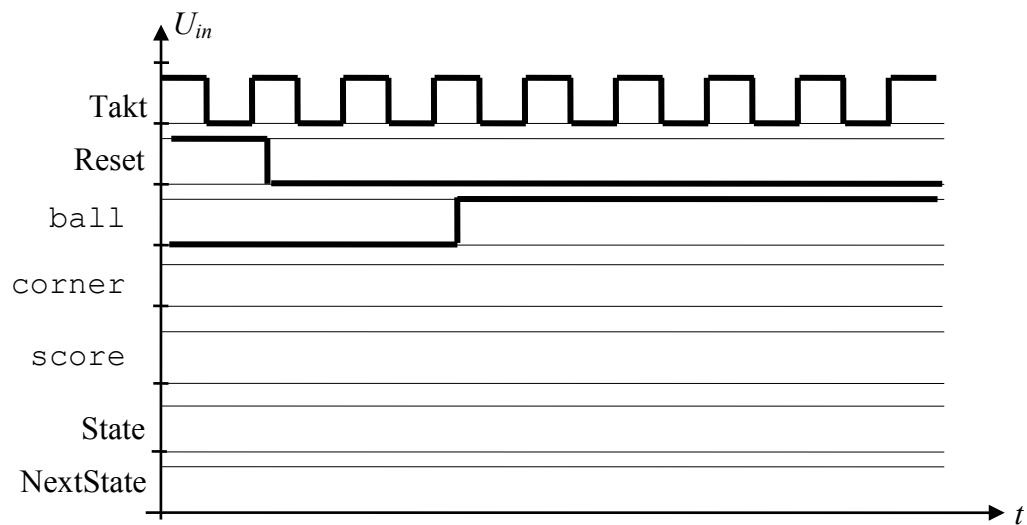

- Identifizieren Sie Taktsignal und Reset!

- Handelt es sich um einen synchronen oder einen asynchronen Reset? Begründen Sie!

- Welches ist die aktive Taktflanke (steigend oder fallend)? Begründen Sie!

- Nennen Sie die 3 Funktionsblöcke, die eine State-Machine stets umfassen muß? Welcher Process im obigen Code entspricht welchem Funktionsblock?

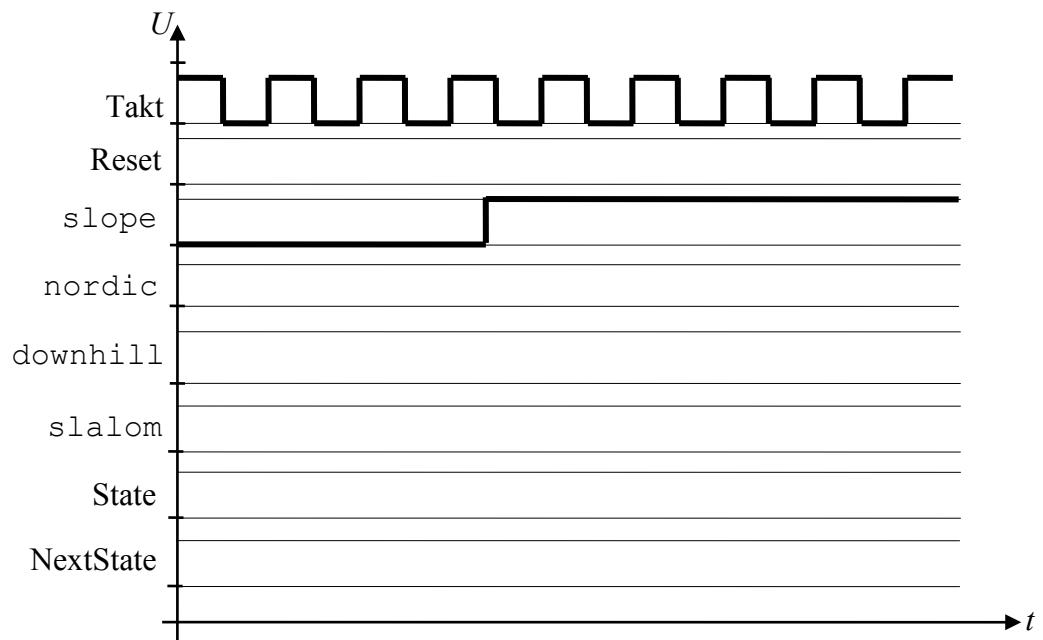

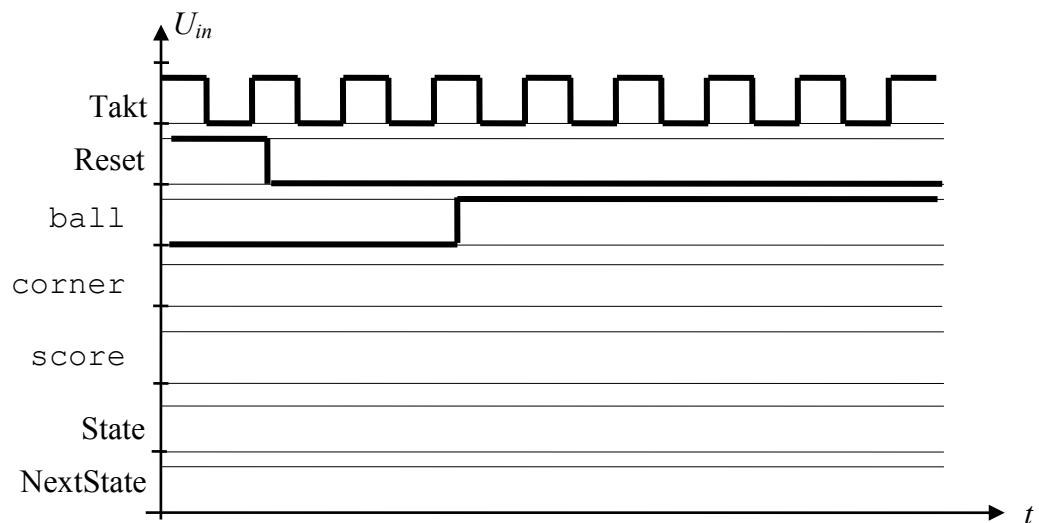

- Tragen Sie den Ablauf der Zustände (State plus zugehöriger Next-State) in Abbildung 4.1 ein! Ergänzen Sie weiters den Zeitverlauf von polka, waltz und tango !

Abbildung 4.1

# Vorlesungsprüfung aus Digitales Design

## 20. Oktober 2004

---

Die Arbeitszeit beträgt 2 Stunden. Als Hilfsmittel sind ausnahmslos Schreibzeug, Lineal und (nicht programmierbarer) Taschenrechner erlaubt. Schreiben Sie Ihre Antworten und Lösungen (incl. Lösungsweg!) mit dokumentechten Stiften (Füllfeder, Kugelschreiber, KEIN Bleistift!) und streichen Sie alles durch, was nicht zur Beurteilung herangezogen werden soll. Ein Abbruch der Prüfung nach Erhalt der Angaben führt in jedem Fall zu einer Beurteilung.

Tragen Sie Namen, Kennzahl und Matrikelnummer **zu Beginn** der Prüfung in die Tabelle ein und beschriften Sie jedes Blatt, das Sie abgeben möchten rechts oben mit Namen und Matrikelnummer.

|               |                 |

|---------------|-----------------|

| Familienname: | Vorname:        |

| Kennzahl:     | Matrikelnummer: |

Viel Erfolg!

**Die nachfolgende Tabelle nicht beschriften!**

| Beispiel       | Mögliche Punkte | Erhaltene Punkte |

|----------------|-----------------|------------------|

| Theoriefragen  | 50              |                  |

| Rechenbeispiel | 1               | 10               |

|                | 2               | 15               |

|                | 3               | 15               |

|                | 4               | 10               |

| Gesamt         | 100             |                  |

## Theoriefragen

**Frage 1:**

Welche 4 Funktionen lassen sich mit einem JK-Flip-Flop realisieren (Bitkombinationen von J und K)

**Frage 2:**

Was besagt das Moore'sche Gesetz

**Frage 3:**

Wie werden in VLSI-Chips Widerstände realisiert?

**Frage 4:**

Erläutern Sie die Auswirkung einer verspäteten Markteinführung eines Produktes auf den Gewinn.

**Frage 5:**

Nennen Sie zwei wesentliche Vorteile des MRAM gegenüber einem EEPROM!

**Frage 6:**

Wozu verwendet man eine Antifuse?

**Frage 7:**

Angenommen die Versorgungsspannung eines Chip liegt am unteren Ende des Toleranzbereiches. Wird der Chip dadurch schneller oder langsamer als beim Nominalwert?

**Frage 8:**

Was versteht man unter infant mortality?

**Frage 9:**

Was ist redundante Logik? Warum sollte sie im Design vermieden werden?

**Frage 10:**

Nennen Sie zwei Beispiele für den negativen Einfluss hoher Temperatur auf einen VLSI-Chip!

## Rechenbeispiele

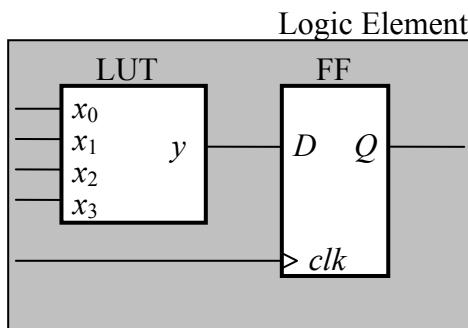

### Beispiel 1

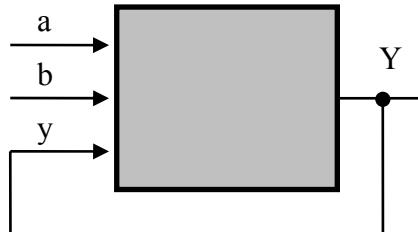

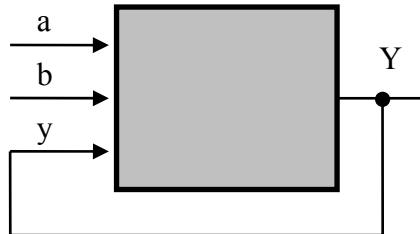

Entwerfen Sie eine Schaltung, die für eine Eingangsvariable  $b$  ( $b_3 \dots b_0$ ) die Ausgangsvariable  $m$  nach folgender Funktion berechnet:  $m = b \bmod 3$ , wobei  $b$  und  $m$  als positive Binärzahlen zu interpretieren sind. Eingang  $b$  und Ausgang  $m$  sind jeweils mittels Register zu synchronisieren. Für die Realisierung steht ihnen ein FPGA mit Logic Elements (LE) bestehend aus LUTs mit nachgeschalteten Flip-Flops (siehe Abbildung 1.1) zur Verfügung.

Abbildung 1.1

- Zeichnen Sie ein Schaltbild für Ihre Lösung, in dem alle benötigten Logic Elements dargestellt sind. Wie viele Logic Elements benötigen Sie ?

- Geben Sie für alle (!) LUTs in diesem Schaltbild Anschlussbelegung und Programmierabelle an!

Im Datenblatt finden Sie für das FPGA unter anderem die folgenden Timing-Angaben:

| Symbol      | Parameter                                             | Value        |

|-------------|-------------------------------------------------------|--------------|

| $t_{LUT}$   | LUT delay                                             | 1.4 ns (max) |

| $t_{SU}$    | register setup time for data before clock             | 1.3 ns (min) |

| $t_H$       | register hold time for data after clock               | 1.4 ns (min) |

| $t_{CO}$    | register clock-to-output delay                        | 0.9 ns (max) |

| $t_{route}$ | interconnect delay from any LE output to any LE input | 1.2 ns (max) |

- Ermitteln Sie anhand dieser Angaben die Laufzeit im kritischen Pfad. Mit welcher Taktfrequenz dürfen Sie die Schaltung maximal betreiben?

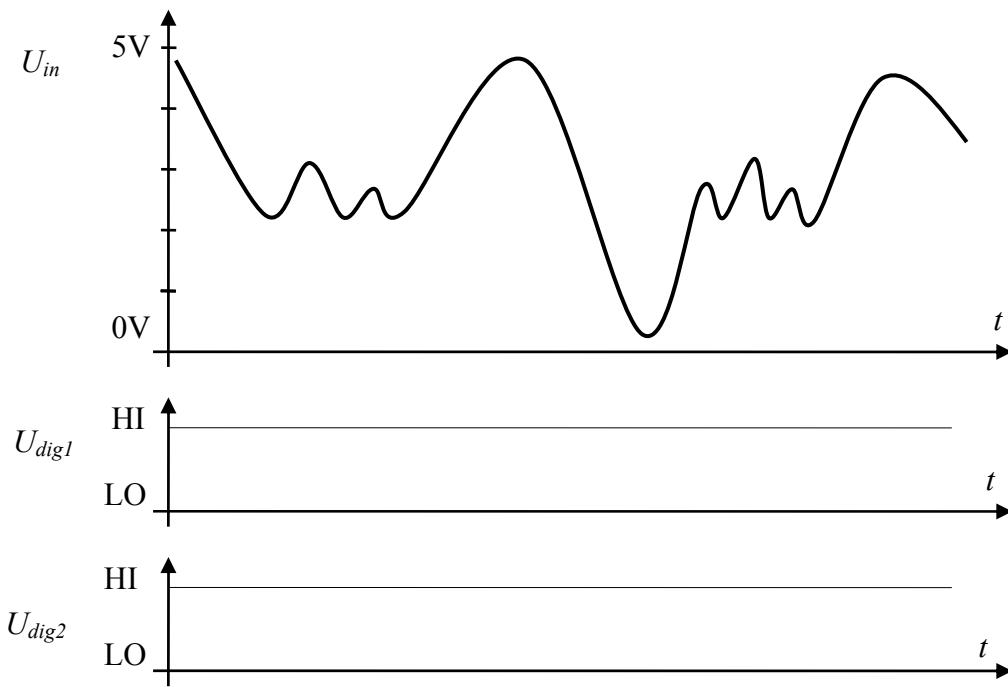

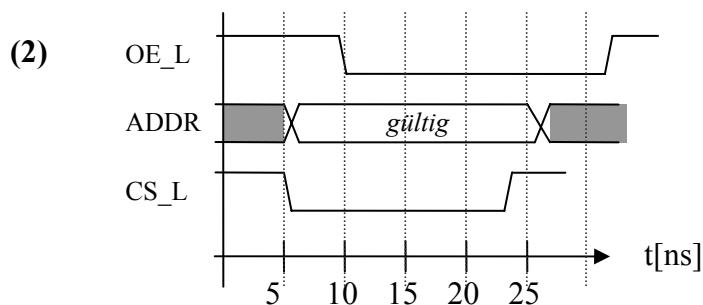

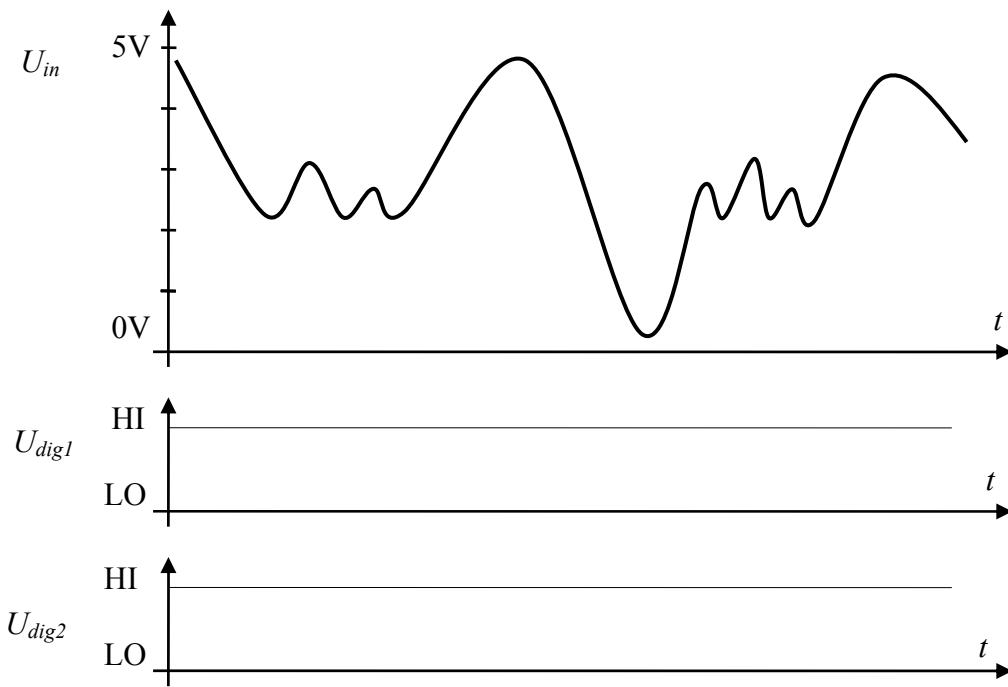

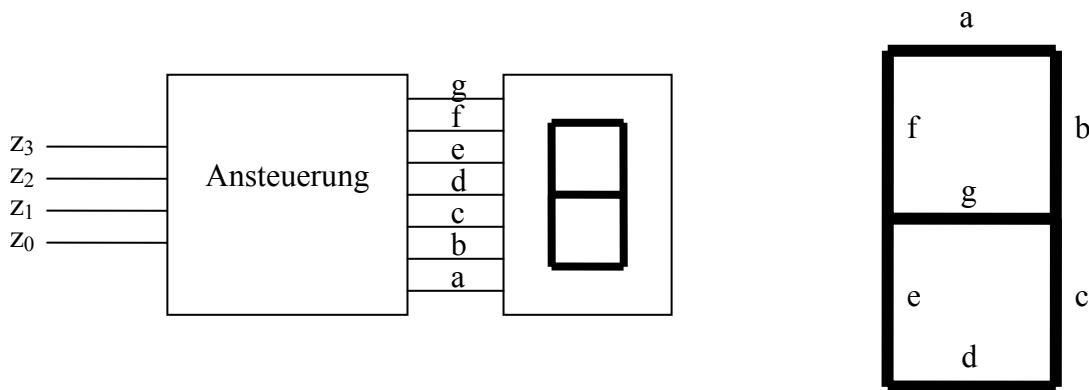

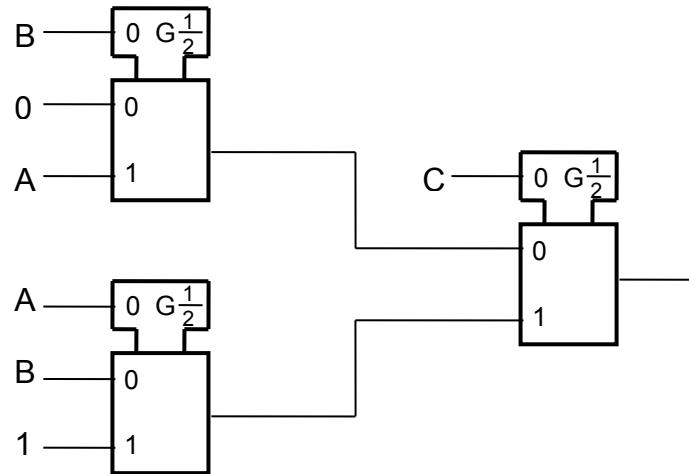

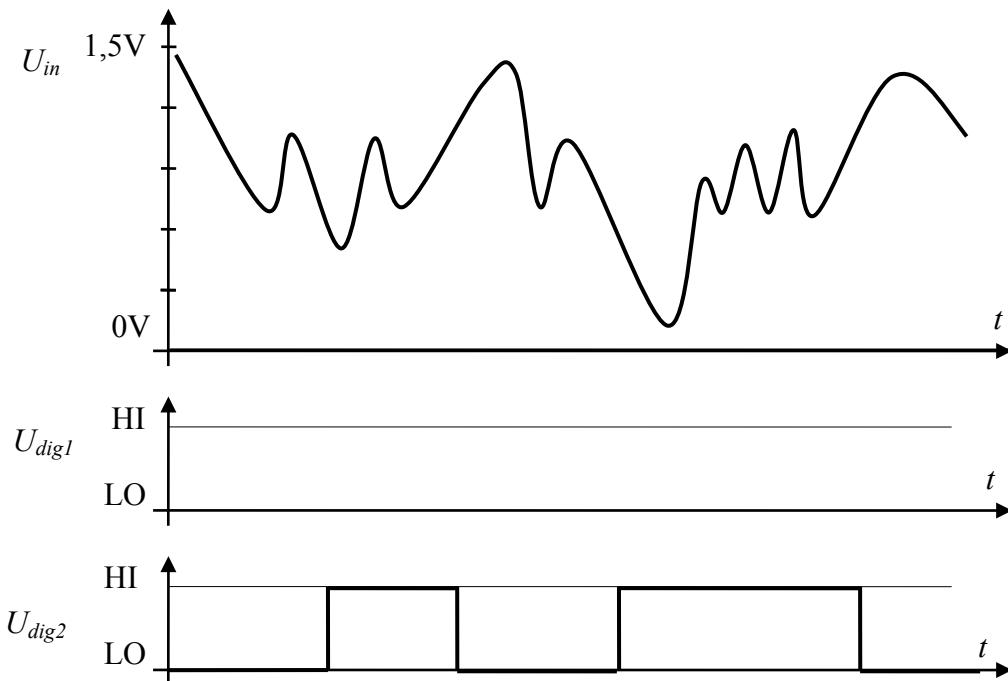

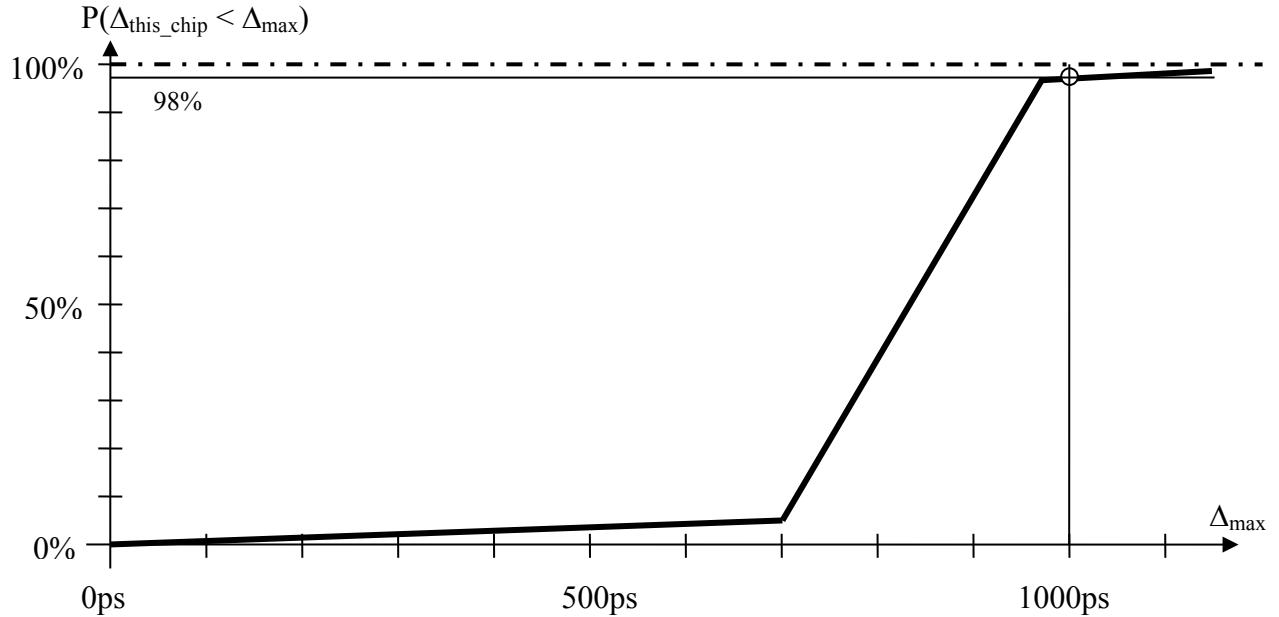

## Beispiel 2

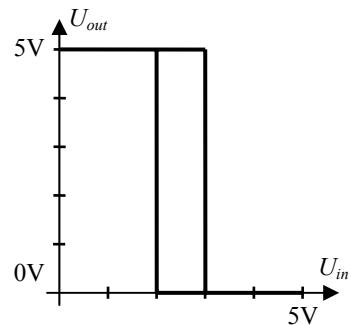

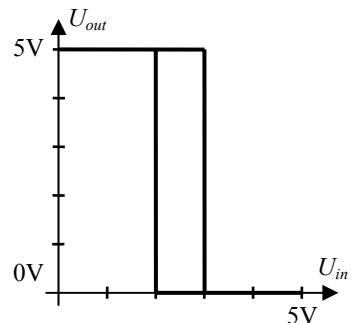

In Abbildung 2.1 ist die Kennlinie eines Schmitt-Trigger gegeben.

Abbildung 2.1

- Kennzeichnen Sie durch Pfeile in den vertikalen Abschnitten der Kennlinie die Richtung, in der die Kennlinie durchlaufen wird.

- Wie groß ist die Hysteresis dieses Schmitt-Trigger (incl. Einheit!) ?

- Handelt es sich um einen invertierenden Schmitt-Trigger oder einen nicht-invertierenden? Begründen Sie!

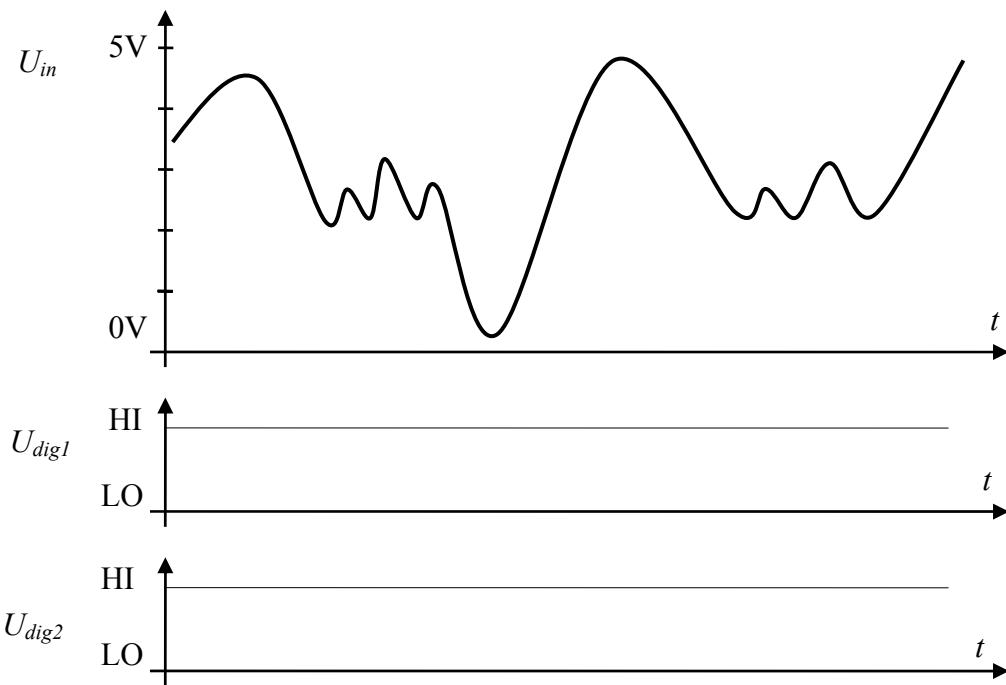

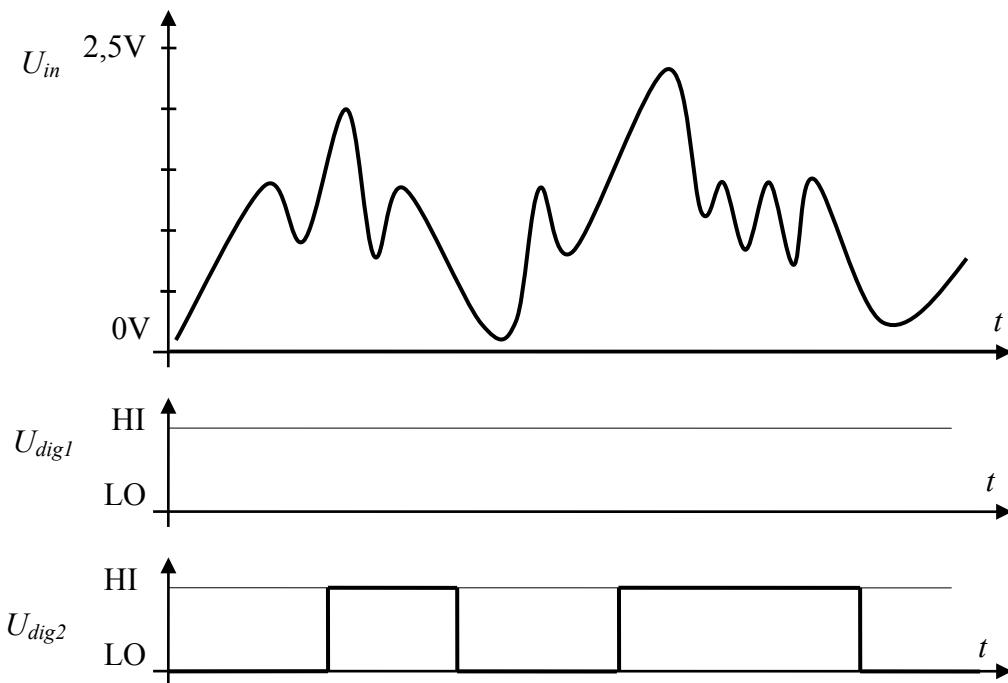

Gegeben ist weiters der Spannungsverlauf  $U_{in}$  in Abbildung 2.2:

Abbildung 2.2

- Wie sieht die Ausgangsspannung am Ausgang des Schmitt-Trigger aus, wenn Sie die Eingangsspannung nach Abbildung 2.2 anlegen? Tragen Sie den Verlauf als  $U_{dig1}$  in Abbildung 2.2 ein!

- Wie könnte man die untere Schwellspannung des Schmitt-Trigger für diese Eingangsspannung besser auslegen, um Störimpulse im mittleren Spannungsbereich wirkungsvoller zu unterdrücken? Tragen Sie Ihren Verbesserungsvorschlag in die Kennlinie ein und stellen Sie den Ausgangsspannungsverlauf der verbesserten Schaltung als  $U_{dig2}$  in Abbildung 2.2 dar!

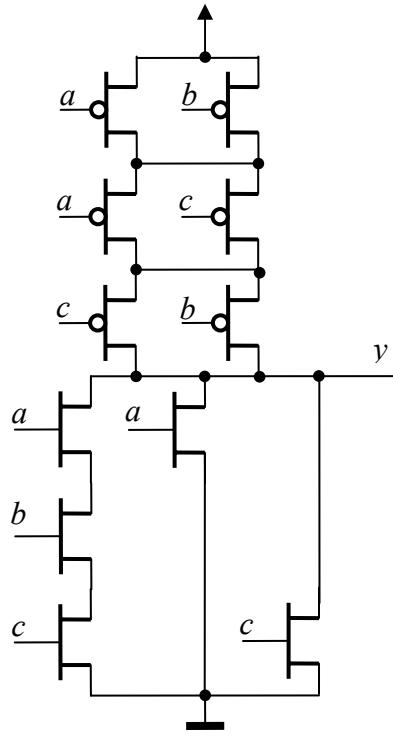

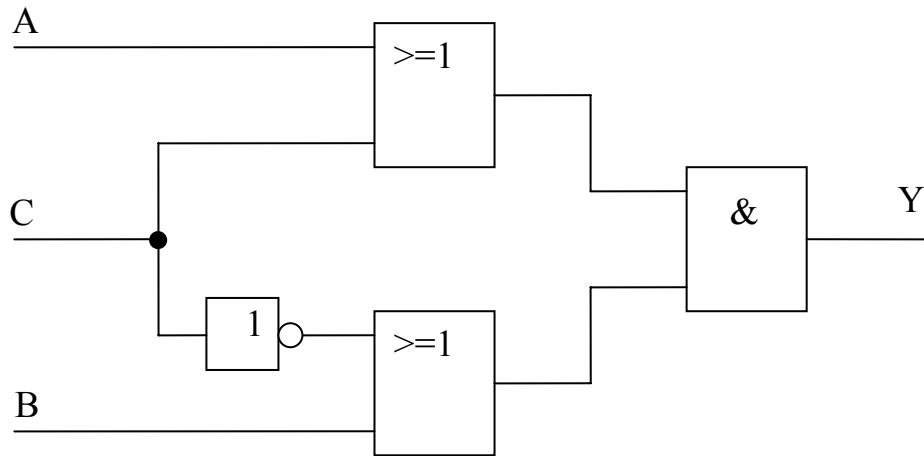

### Beispiel 3

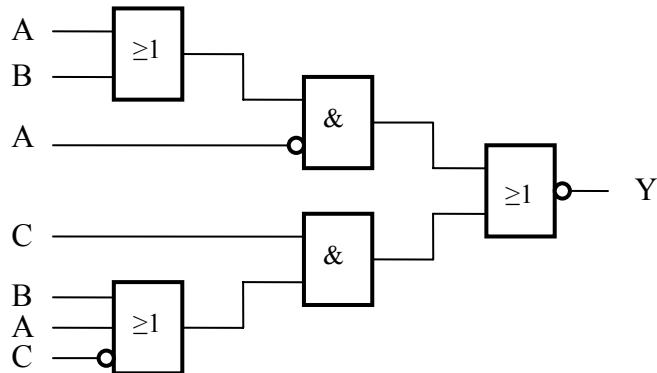

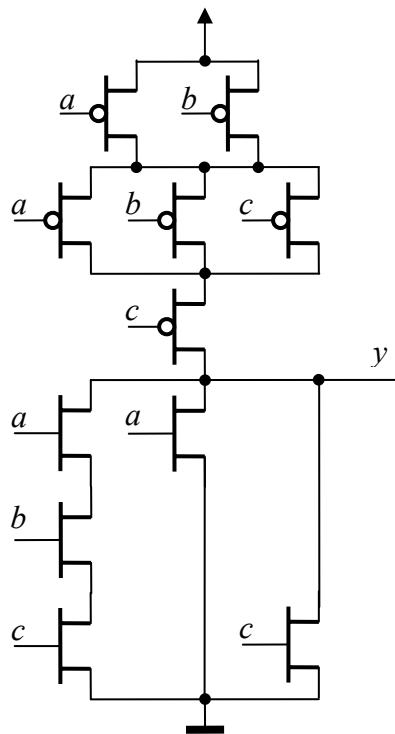

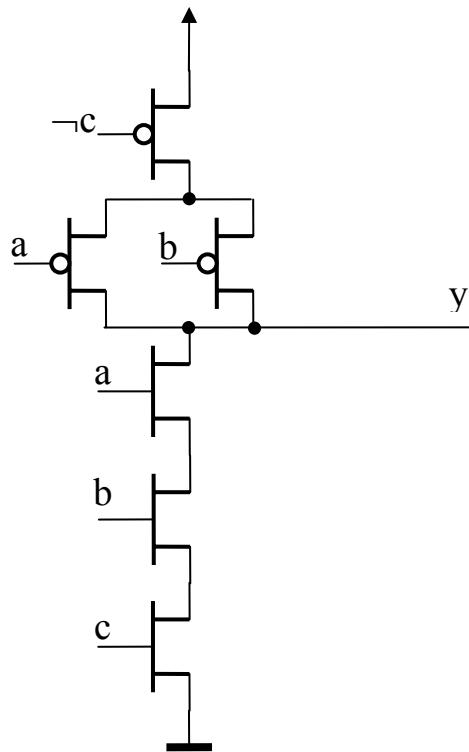

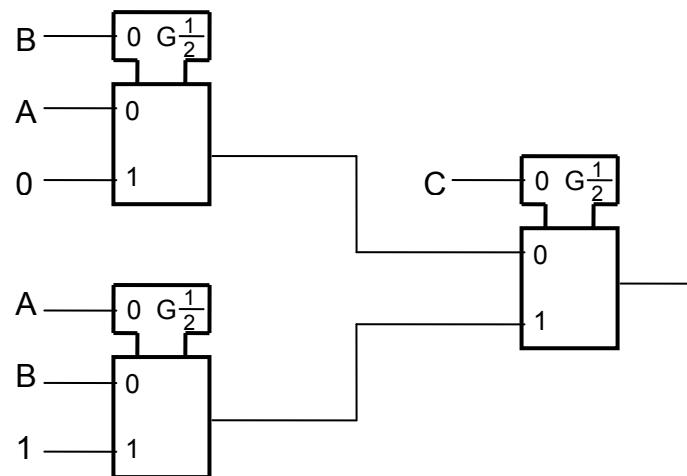

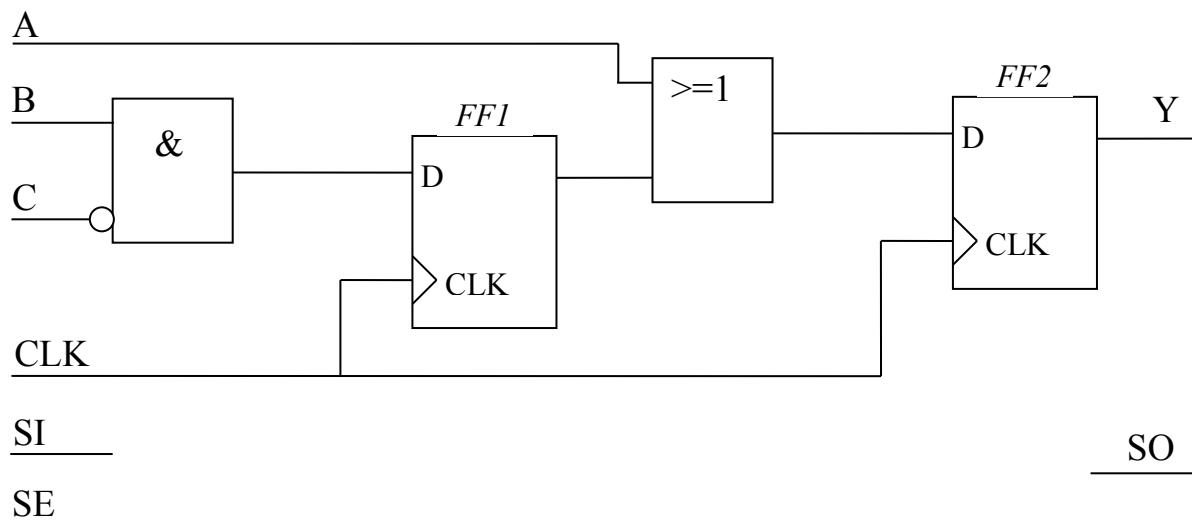

Gegeben ist die Schaltung in Abbildung 3.1:

Abbildung 3.1

- (a) Ermitteln Sie für diese Schaltung die logische Gleichung, die Wahrheitstabelle und das KV-Diagramm!

Erarbeiten Sie für diese logische Funktion eine Implementierung mittels OAI-Gatter.

- (b) Leiten Sie dazu aus dem KV-Diagramm eine vereinfachte Darstellung der Gleichung ab, die Sie als OAI implementieren können!

- (c) Entwerfen und zeichnen Sie die entsprechende Schaltung für den n-Stack!

- (d) Entwerfen und zeichnen Sie die entsprechende Schaltung für den p-Stack!

- (e) Zeigen Sie, wie man die beiden Stacks richtig zur Gesamtschaltung zusammenfügt!

## Beispiel 4

Gegeben ist folgender VHDL-Code einer State-Machine:

```

library IEEE;

use      IEEE.std_logic_1164.all;

entity mine is

port(

robert:  in std_logic;

monica :  in std_logic;

paula: out std_logic_vector(0 to 2)

);

end mine;

```

```

architecture friends of mine is

signal jessica, david:

std_logic_vector(0 to 1);

begin

party: process(jessica)

begin

case jessica is

when "00"  => paula <= "101";

when "01"  => paula <= "001";

when "10"  => paula <= "110";

when others => paula <= "010";

end case;

end process party;

holiday: process(jessica)

begin

case jessica is

when "00"  => david <= "01";

when "11"  => david <= "01";

when "01"  => david <= "10";

when others => david <= "00";

end case;

end process holiday;

dinner: process(robert, monica)

begin

if monica = '1' then

jessica <= "00";

else

if robert'event and robert = '0'

then

jessica <= david;

end if;

end if;

end process dinner;

end friends;

```

- (a) Identifizieren Sie Taktsignal und Reset! Ist die steigende oder die fallende Taktflanke die aktive?

- (b) Nennen Sie die 3 Funktionsblöcke, die eine State-Machine stets umfassen muß? Welcher Process im obigen Code entspricht welchem Funktionsblock?

- (c) Ist der Reset synchron oder asynchron? Begründen Sie

- (d) Wie viele interne Zustände nimmt die State-Machine im normalen Betrieb ein? Begründen Sie! In welcher Reihenfolge werden sie ausgehend vom Reset durchlaufen?

# Vorlesungsprüfung aus Digitales Design

21. April 2004

---

Die Arbeitszeit beträgt 2 Stunden. Als Hilfsmittel sind ausnahmslos Schreibzeug, Lineal und (nicht programmierbarer) Taschenrechner erlaubt. Schreiben Sie Ihre Antworten und Lösungen (incl. Lösungsweg!) mit dokumentechten Stiften (Füllfeder, Kugelschreiber, KEIN Bleistift!) und streichen Sie alles durch, was nicht zur Beurteilung herangezogen werden soll. Ein Abbruch der Prüfung nach Erhalt der Angaben führt in jedem Fall zu einer Beurteilung.

Tragen Sie Namen, Kennzahl und Matrikelnummer **zu Beginn** der Prüfung in die Tabelle ein und beschriften Sie jedes Blatt, das Sie abgeben möchten rechts oben mit Namen und Matrikelnummer.

|               |                 |

|---------------|-----------------|

| Familienname: | Vorname:        |

| Kennzahl:     | Matrikelnummer: |

Viel Erfolg!

**Die nachfolgende Tabelle nicht beschriften!**

| Beispiel       | Mögliche Punkte | Erhaltene Punkte |

|----------------|-----------------|------------------|

| Theoriefragen  | 50              |                  |

| Rechenbeispiel | 1               | 10               |

|                | 2               | 15               |

|                | 3               | 10               |

|                | 4               | 15               |

| Gesamt         | 100             |                  |

## Theoriefragen

**Frage 1:**

Was ist eine Sign-off Simulation?

**Frage 2:**

Welche Strecke legt eine elektromagnetische Welle auf einer Leitung innerhalb von 1ns zurück?

**Frage 3:**

Handelt es sich bei einem ROM um rein kombinatorische oder sequentielle Logik? Begründen Sie!

**Frage 4:**

Was versteht man im Zusammenhang mit der Simulation unter einem „Delta-Cycle“?

**Frage 5:**

Was ist ein EEPROM?

**Frage 6:**

Wozu verwendet man eine Antifuse?

**Frage 7:**

Angenommen die Versorgungsspannung eines Chip liegt am unteren Ende des Toleranzbereiches. Wird der Chip dadurch schneller oder langsamer als beim Nominalwert?

**Frage 8:**

Was ist Latch-up?

**Frage 9:**

Welche Probleme treten beim „exhaustive Test“ in der praktischen Anwendung auf?

**Frage 10:**

Was versteht man unter dem „Delay insensitive Model“?

## Rechenbeispiele

### Beispiel 1

Die folgende Funktion ist in Hardware zu realisieren:

$$Y = (\neg A \vee \neg C) \wedge (B \vee \neg C)$$

- (a) Geben Sie Wahrheitstabelle und KV-Diagramm für diese Funktion an und vereinfachen Sie!

- (b) Wenn Sie die Wahl zwischen einer Realisierung als AOI oder als OAI haben, was würden Sie bevorzugen? Begründen Sie!

- (c) Entwerfen Sie zunächst den n-Stack für Ihre bevorzugte Lösung!

- (d) Entwerfen Sie weiters den dazugehörigen p-Stack!

- (e) Stellen Sie die Realisierung der Gesamtlösung mittels FETs dar (Schaltbild)! Stellen Sie dabei auch eventuell benötigte Inverter an Ein- oder Ausgang als Transistorschaltung dar.

### Beispiel 2

An einem Chip messen Sie bei einer Versorgungsspannung von  $V_{DD}=3,3V$  einen mittleren Strom von 2A. Im Datenblatt finden Sie für das Gehäuse folgende Angabe:

$$\theta_{JC} = 3K/W$$

$$\theta_{JA} = 5K/W \text{ für Betrieb ohne Kühlkörper.}$$

- (a) Welche Temperatur  $T_J$  erreicht der Die im Betrieb bei  $T_{AMB}=20^\circ C$ ?

- (b) Angenommen Sie erhöhen für einen Burn-in dieses Chips die Versorgungsspannung auf  $V_{DD}=4,0V$ . Welche Temperatur  $T_J$  erreicht der Die nun?

(Nehmen Sie an, die Verlustleistung sei durch Ladeströme dominiert)

- (c) Bestimmen Sie Temperature Acceleration Factor  $AF_T$  und Voltage Acceleration Factor  $AF_V$  für den Betrieb bei  $V_{DD} = 4,0V$  und  $T_{AMB} = 20^\circ C$  gegenüber einem Normalbetrieb bei  $V_{DD} = 3,3V$  und  $T_{AMB} = 20^\circ C$ !

$$k = 8,6 \cdot 10^{-5} \text{ eV/K} ; E_{act} = 0,7 \text{ eV} ; \gamma = 3,2 \text{ V}^{-1}$$

- (d) Angenommen, Sie wollen erreichen, dass der Chip beim Burn-in innerhalb von 20 Stunden um 1 Jahr altert (als Normalbetrieb gilt wieder  $T_{AMB} = 20^\circ C$ ;  $V_{DD} = 3,3V$ ).

Welchen Acceleration Factor  $AF$  benötigen Sie insgesamt?

Welcher Temperature Acceleration Factor  $AF_T$  ist nun erforderlich ( $V_{DD}$  ist weiterhin 4,0V)?

Bei welcher Die-Temperatur  $T_J$  und welcher Umgebungstemperatur  $T_{AMB}$  muss man den Chip dafür betreiben? Ist das technisch machbar? Begründen Sie!

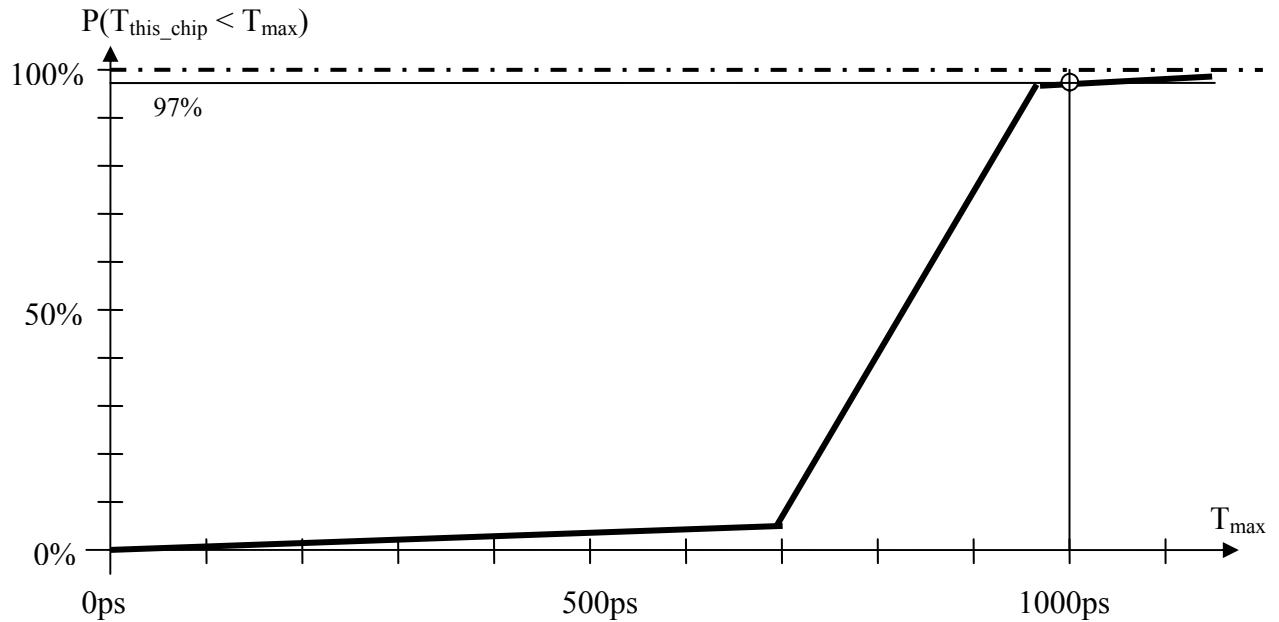

### Beispiel 3

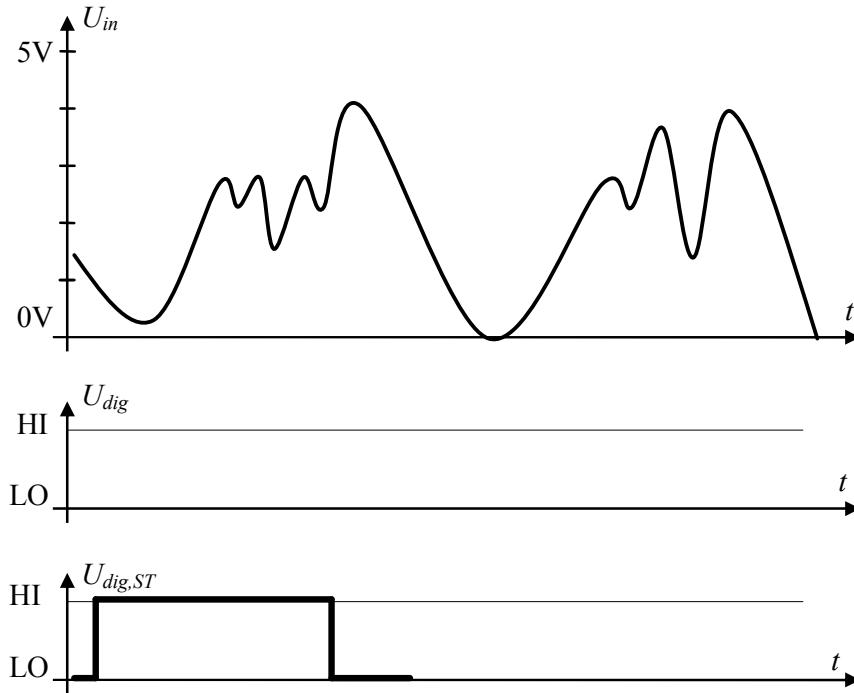

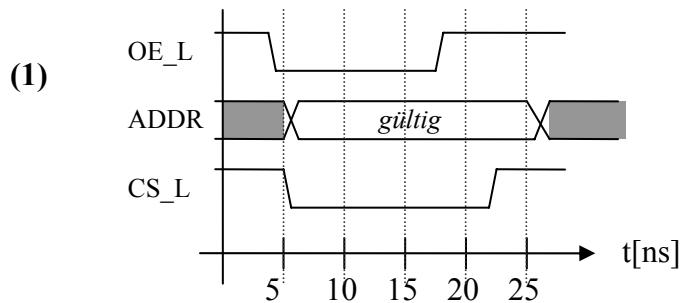

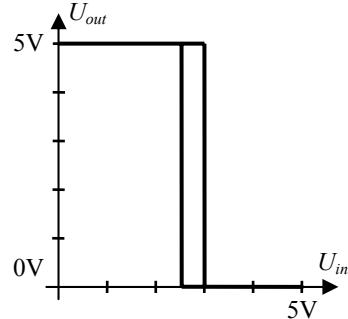

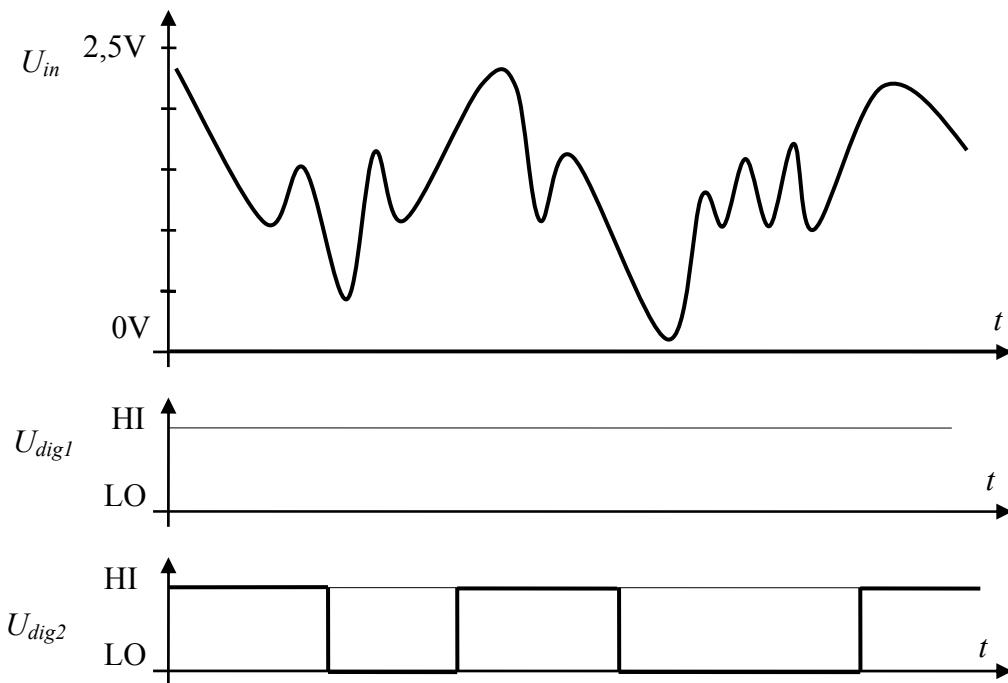

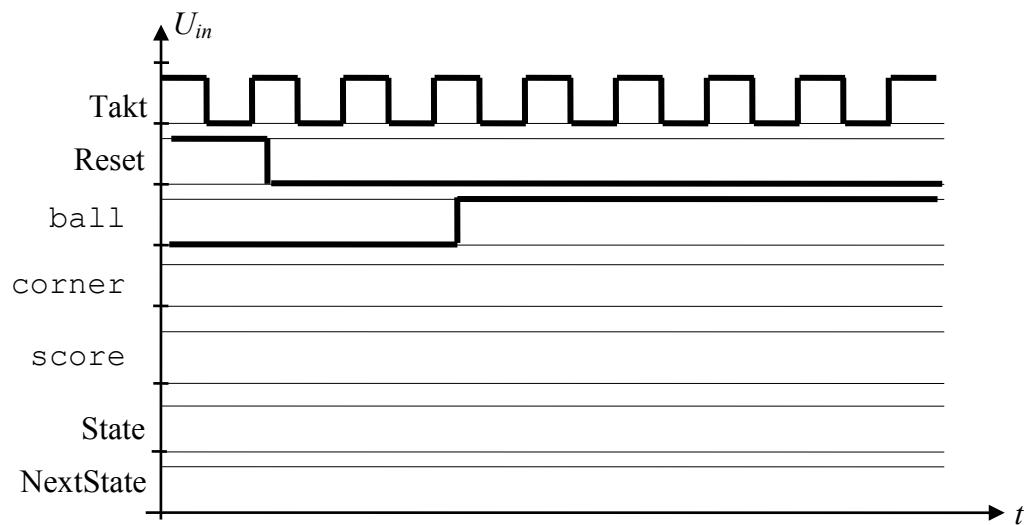

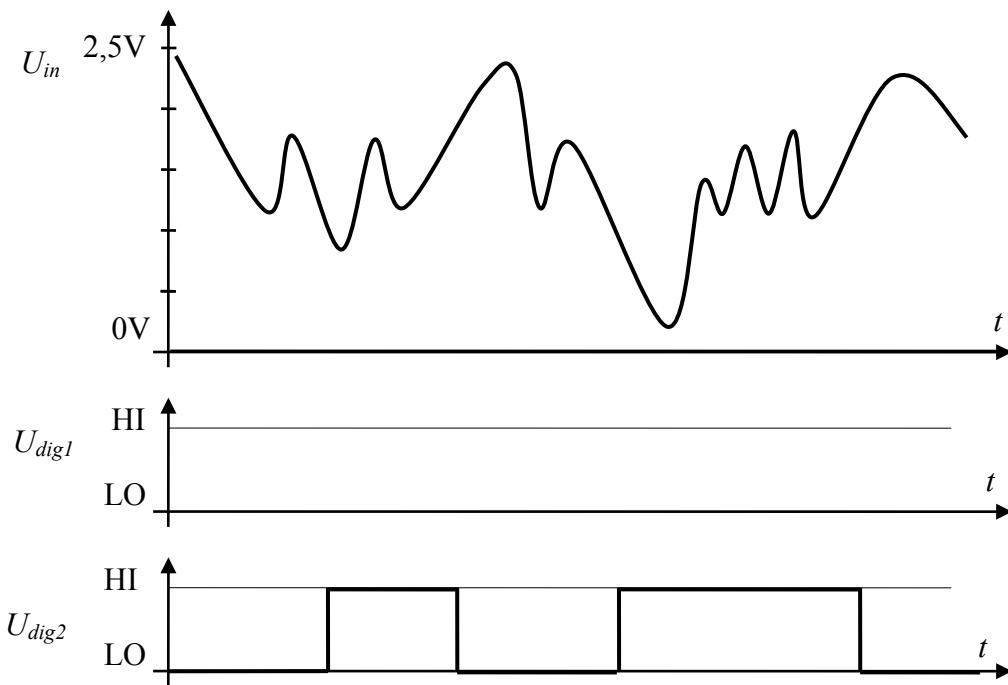

Gegeben ist der Spannungsverlauf  $U_{in}$  in Abbildung 1:

Abbildung 1

- (a) Tragen Sie in die Abbildung den Spannungsverlauf  $U_{dig}$  nach der Digitalisierung dieser Eingangsspannung ein, wenn der Schwellwert fix bei 2,0V liegt.

Angenommen Sie legen  $U_{in}$  am Eingang eines Schmitt Trigger an und erhalten am Ausgang die in Abbildung 1 unten dargestellte Spannung  $U_{dig,ST}$ .

- (b) Wo liegen die Schwellwerte dieses Schmitt-Trigger?

(c) Wie groß ist die Hysterese dieses Schmitt-Trigger (incl. Einheit)?

(d) Stellen Sie die Kennlinie dieses Schmitt-Trigger dar (Achsen beschriften!). Kennzeichnen Sie durch Pfeile in den vertikalen Abschnitten der Kennlinie die Richtung, in der die Kennlinie durchlaufen wird!

(e) Handelt es sich um einen invertierenden Schmitt-Trigger oder einen nicht-invertierenden? Begründen Sie!

(f) Vervollständigen Sie den Verlauf der Spannung  $U_{dig,ST}$  in Abbildung 1 unten!

## Beispiel 4

Gegeben ist folgender VHDL-Code einer State-Machine:

```

library IEEE;

use      IEEE.std_logic_1164.all;

entity universe is

port(

moon:      in std_logic;

jupiter : in std_logic;

neptun:out std_logic_vector(0 to 2)

);

end universe;

```

```

architecture master of universe is

signal earth, pluto:

std_logic_vector(0 to 1);

begin

fire: process(earth)

begin

case earth is

when "00"  => neptun <= "101";

when "01"  => neptun <= "001";

when "10"  => neptun <= "110";

when others => neptun <= "010";

end case;

end process fire;

water: process(earth)

begin

case earth is

when "00"  => pluto <= "01";

when "10"  => pluto <= "11";

when "01"  => pluto <= "10";

when others => pluto <= "00";

end case;

end process water;

ice: process(moon, jupiter)

begin

if jupiter = '1' then

earth <= "00";

else

if moon'event and moon = '1' then

earth <= pluto;

end if;

end if;

end process ice;

end master;

```

- Identifizieren Sie Taktsignal und Reset! Ist der Reset HI-aktiv oder LO-aktiv?

- Nennen Sie die 3 Funktionsblöcke, die eine State-Machine stets umfassen muß? Welcher Process im obigen Code entspricht welchem Funktionsblock?

- Wie viele Bit umfasst der Eingang dieser Schaltung? Wie viele der Ausgang? Begründen Sie!

- Wie viele interne Zustände kann die State-Machine einnehmen? Begründen Sie! In welcher Reihenfolge werden sie ausgehend vom Reset durchlaufen?

# Vorlesungsprüfung aus Digitales Design

7. Juni 2005

---

Die Arbeitszeit beträgt 2 Stunden. Als Hilfsmittel sind ausnahmslos Schreibzeug, Lineal und (nicht programmierbarer) Taschenrechner erlaubt. Schreiben Sie Ihre Antworten und Lösungen (incl. Lösungsweg!) mit dokumentechten Stiften (Füllfeder, Kugelschreiber, KEIN Bleistift!) und streichen Sie alles durch, was nicht zur Beurteilung herangezogen werden soll. Ein Abbruch der Prüfung nach Erhalt der Angaben führt in jedem Fall zu einer Beurteilung.

Tragen Sie Namen, Kennzahl und Matrikelnummer **zu Beginn** der Prüfung in die Tabelle ein und beschriften Sie jedes Blatt, das Sie abgeben möchten rechts oben mit Namen und Matrikelnummer.

|               |                 |

|---------------|-----------------|

| Familienname: | Vorname:        |

| Kennzahl:     | Matrikelnummer: |

Viel Erfolg!

**Die nachfolgende Tabelle nicht beschriften!**

| Beispiel       | Mögliche Punkte | Erhaltene Punkte |

|----------------|-----------------|------------------|

| Theoriefragen  | 50              |                  |

| Rechenbeispiel | 1               | 15               |

|                | 2               | 10               |

|                | 3               | 10               |

|                | 4               | 15               |

| Gesamt         | 100             |                  |

## Theoriefragen

**Frage 1:**

Was versteht man unter einem Maxterm?

**Frage 2:**

Welche Strecke legt eine elektromagnetische Welle auf einer Leitung innerhalb von 1ns zurück?

**Frage 3:**

Geben Sie die logische Funktion eines OAI11 an!

**Frage 4:**