SpringerWienNewYork

Springers Lehrbücher

der Informatik

Herausgegeben von

o. Univ.-Prof. Dr.-Ing. Gerhard H. Schildt

Technische Universität Wien

SpringerWienNewYork

Gerhard H. Schildt, Daniela Kahn,

Christopher Kruegel, Christian Moerz

Einführung in die

Technische Informatik

Unter Mitarbeit von

Johann Klasek, Heinrich Pangratz,

Alexander Redlein, Ulrich Schmid,

Stefan Stöckler

Zweite, überarbeitete

und erweiterte Auflage

SpringerWienNewYork

o. Univ.-Prof. Dr.-Ing. Dipl.-Ing. u. Ing. (grad.) Gerhard H. Schildt

Daniela Kahn

Christopher Kruegel

Christian Moerz

Institut für Rechnergestützte Automation

Technische Universität, Wien, Österreich

e-mail: schi@auto.tuwien.ac.at

Das Werk ist urheberrechtlich geschützt.

Die dadurch begründeten Rechte, insbesondere die der Übersetzung, des Nachdruckes, der Entnahme von Abbildungen, der Funksendung, der Wiedergabe auf photomechanischem oder ähnlichem Wege und der Speicherung in Datenverarbeitungsanlagen, bleiben, auch bei nur auszugsweiser Verwertung, vorbehalten.

© 2003 und 2005 Springer-Verlag/Wien

Printed in Austria

SpringerWienNewYork ist ein Unternehmen

von Springer Science + Business Media

[springer.at](http://springer.at)

Die Wiedergabe von Gebrauchsnamen, Handelsnamen, Warenbezeichnungen usw. in diesem Buch berechtigt auch ohne besondere Kennzeichnung nicht zu der Annahme, dass solche Namen im Sinne der Warenzeichen- und Markenschutz-Gesetzgebung als frei zu betrachten wären und daher von jedermann benutzt werden dürfen.

Produkthaftung: Sämtliche Angaben in diesem Fachbuch/wissenschaftlichen Werk erfolgen trotz sorgfältiger Bearbeitung und Kontrolle ohne Gewähr. Eine Haftung der Autoren oder des Verlages aus dem Inhalt dieses Werkes ist ausgeschlossen.

Satz: Reproduktionsfertige Vorlage der Autoren

Druck und Bindung: Grasl Druck & Neue Medien, 2540 Bad Vöslau, Österreich

Gedruckt auf säurefreiem, chlorfrei gebleichtem Papier – TCF

SPIN: 11377511

Mit 254 Abbildungen

Bibliografische Information Der Deutschen Bibliothek

Die Deutsche Bibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über <<http://dnb.ddb.de>> abrufbar.

ISSN 0938-9504

ISBN-10 3-211-24346-1 SpringerWienNewYork

ISBN-13 978-3-211-24346-6 SpringerWienNewYork

ISBN 3-211-83853-8 1. Aufl. SpringerWienNewYork

*Meinem verehrten Lehrer Prof. Dr.-Ing. Hans Fricke

( apl. Professor an der Technischen Universität Braunschweig )

gewidmet*

# Vorwort

*Für euch, Kinder der Wissenschaft und der Weisheit,

haben wir dieses geschrieben. Erforschet das Buch

und suchet euch unsere Ansicht zusammen, die wir

verstreut und an mehreren Orten dargetan haben;

was euch an einem Orte verborgen bleibt, das haben

wir an einem anderen offengelegt,

damit es fassbar werde für eure Weisheit.*

Heinrich Cornelius Agrippa von Nettesheim,

„De occulta philosophia“.

Das vorliegende Buch „Technische Informatik“ wendet sich sowohl an Studierende der Informatik als auch an Ingenieure und Entwickler aus der Praxis. Es entstand aus Skripten zur Vorlesung „Einführung in die Technische Informatik“, die wir an der Technischen Universität Wien für Informatikstudierende halten. Es schließt sich nahtlos an das Lehrbuch „Informatik Grundlagen“ von Blieberger, Burgstaller und Schildt an. Unser Anliegen ist es, für den Bereich der technischen Informatik weiterführend zu zeigen, wie man elektronische Bauelemente für Computersysteme einsetzen kann. Der dargebotene Stoff soll den Leser in die Lage versetzen, die technischen Möglichkeiten und Grenzen solcher Systeme zu erkennen. Dadurch soll dem Studierenden das Wissen vermittelt werden, Leistungsmerkmale heutiger Rechnersysteme angemessen zu beurteilen. Wer auch immer heute Computersysteme einsetzt, die seinen persönlichem Anforderungsprofil entsprechen sollen, muss entscheiden, was für ihn effizient und zugleich kostengünstig ist. Daher ist es nötig, sowohl Hardware- als auch Softwareaspekte umfassend kennenzulernen. Das Grundwissen dafür wird in diesem Buch vermittelt. Der präsentierte Stoff ist für Informatikstudierende ohne besondere Kenntnisse der Elektrotechnik aufbereitet. Wo immer es notwendig war, elektrotechnische Grundkenntnisse mit einzubeziehen, haben wir versucht, dieses so einfach wie möglich darzustellen. Für die Lektüre genügen Grundkenntnisse der Physik und Mathematik. Dem vorliegenden Band ist das Buch „Informatik Aufgaben und Lösungen“ zugeordnet, in dem Aufgaben und zugehörige Lösungen dargestellt sind.

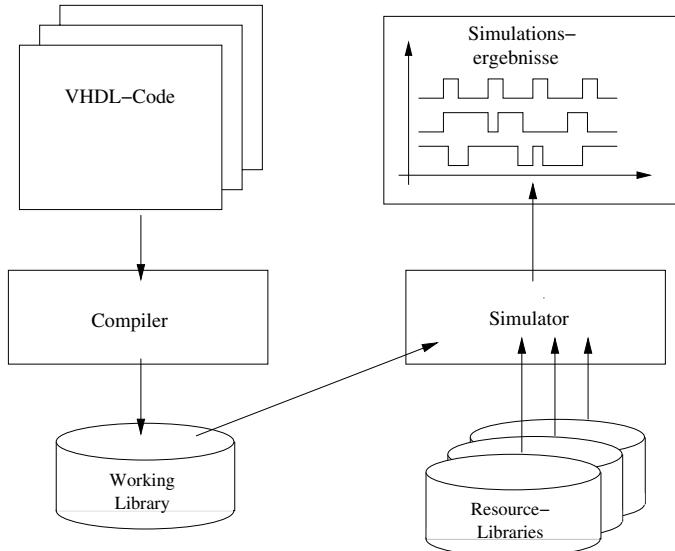

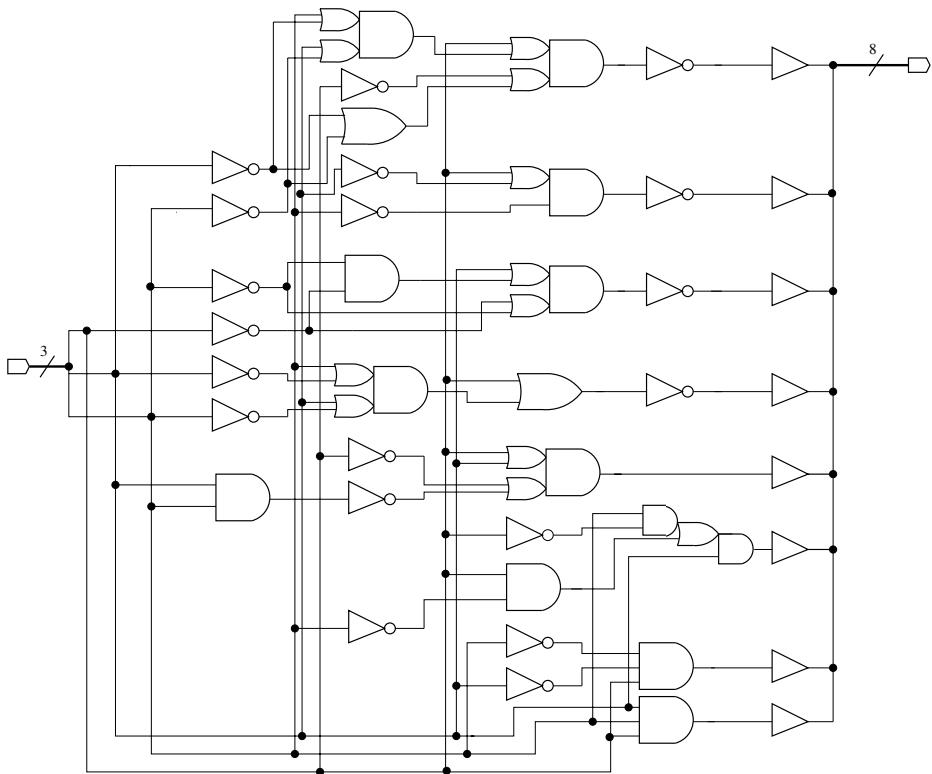

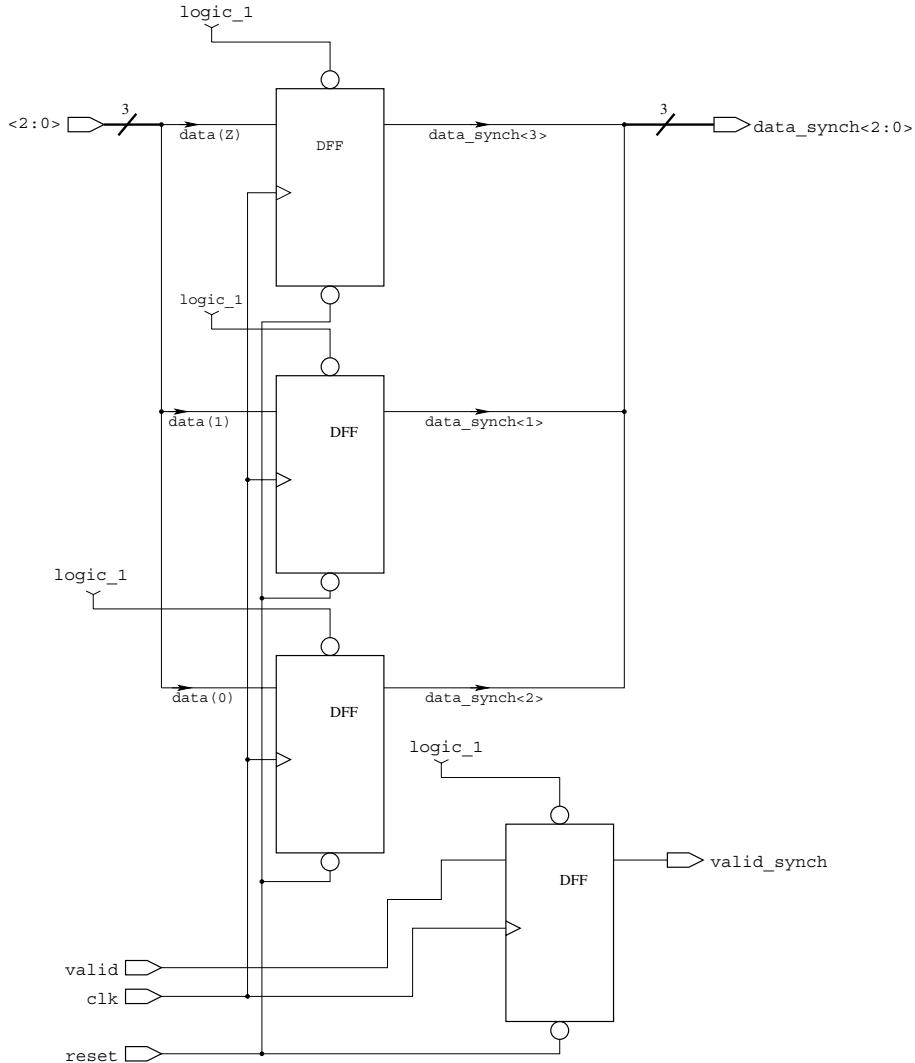

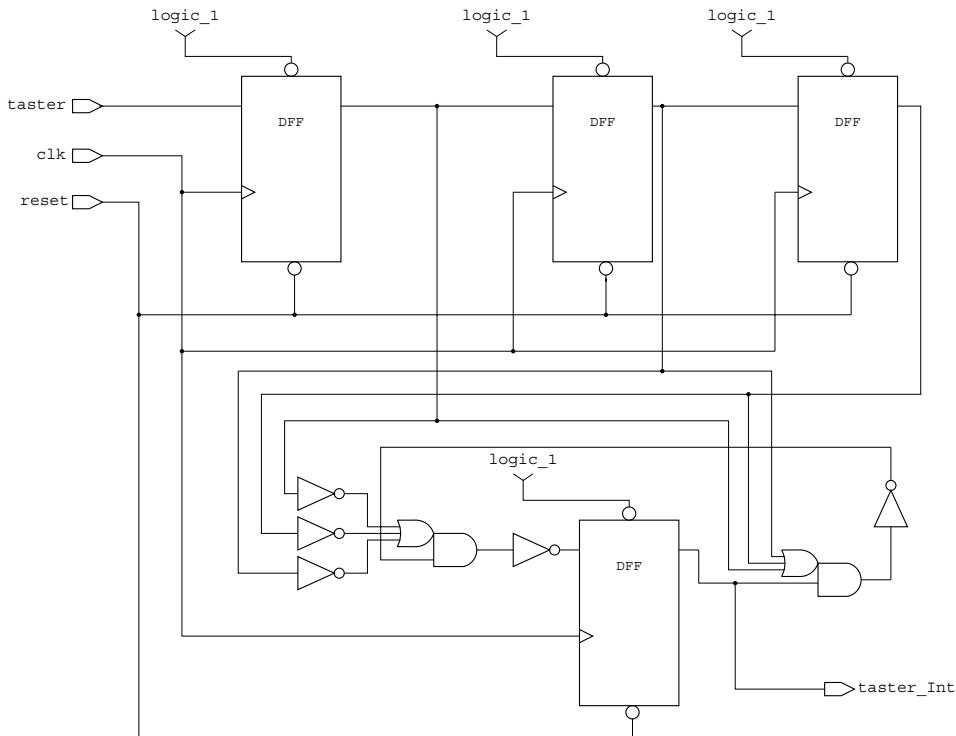

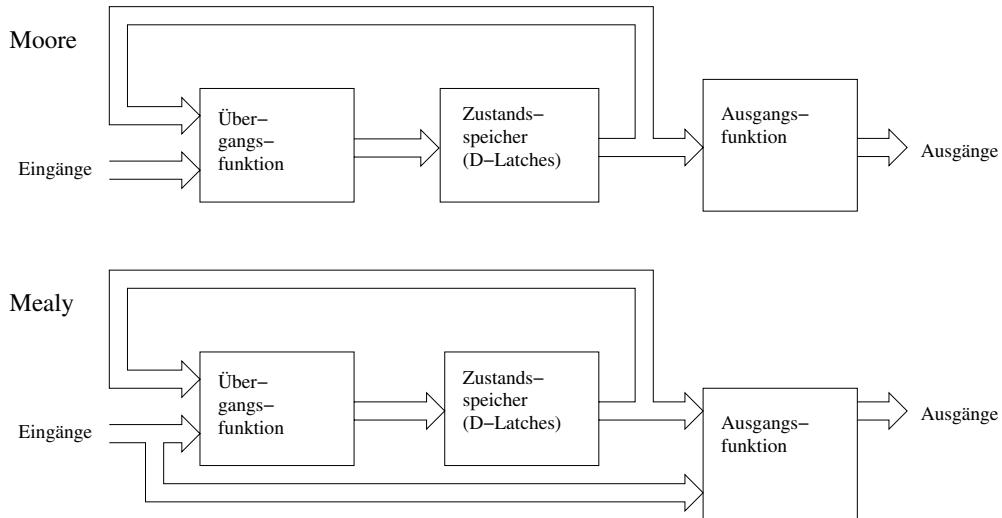

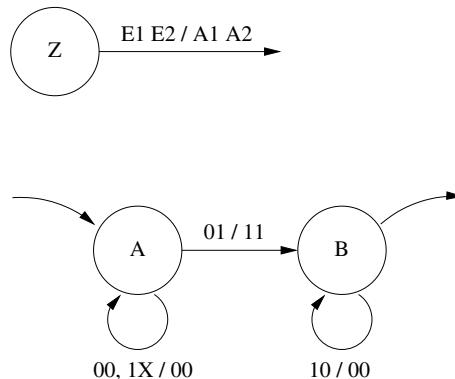

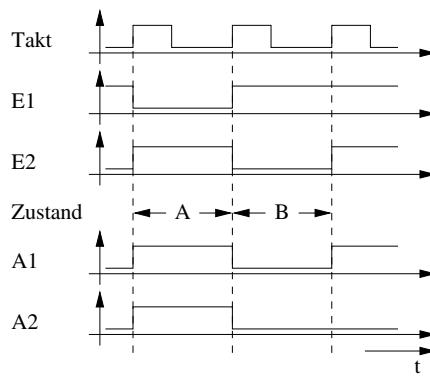

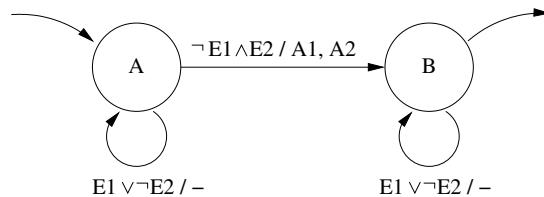

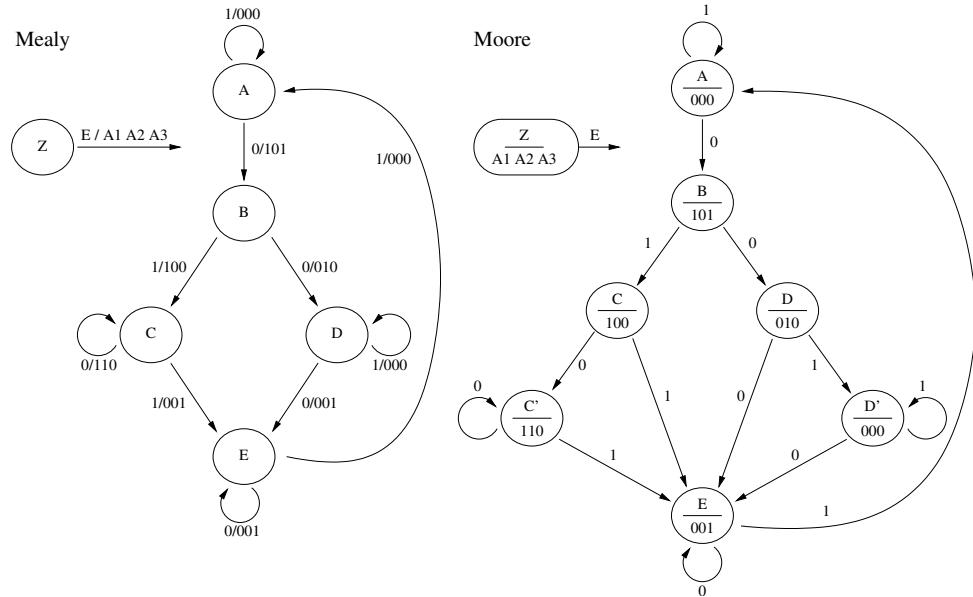

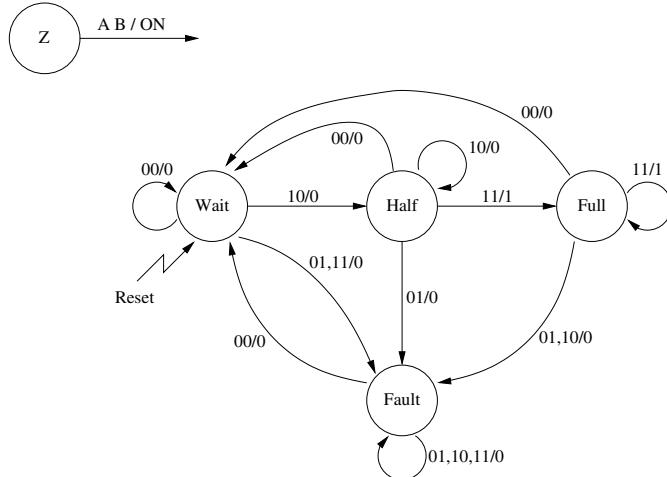

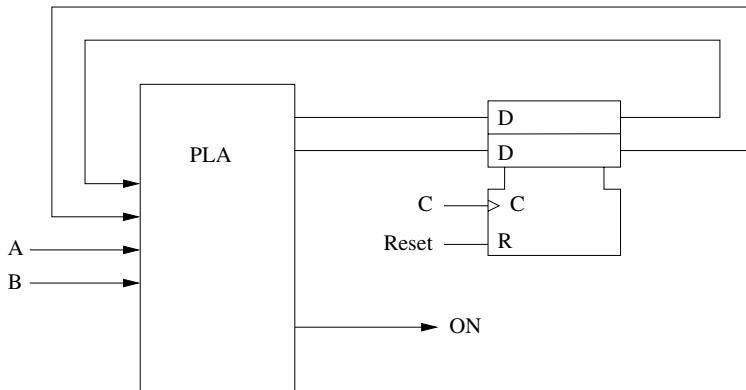

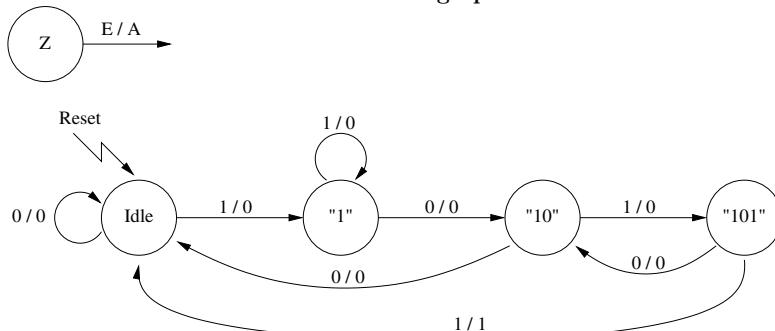

Im ersten Abschnitt zur Hardware werden logische Schaltungen behandelt. Hier werden auch besonders wichtige signalverarbeitende elektronische Schaltungen erläutert. Daran anschließend werden Grundlagen der Entwurfssprache VHDL ( Very High Speed Integrated Circuit Hardware Description Language ) vorgestellt. Dem folgt ein Kapitel über Mikroprozessoren mit der Darstellung von Moore- und Mealy-Schaltwerken. Hier danken wir Prof. Pangratz für die Bereitstellung seines Skriptums „Rechnerstrukturen“, aus dem wir die Beiträge über Mealy- und Moore-Schaltwerke entnommen haben. Anschließend betrachten wir Computersysteme mit Prozessoren, Speichern und peripheren Geräten.

Im zweiten Abschnitt werden Betriebssysteme und Systemsoftware behandelt. Besondere Bedeutung kommt dabei den Programmprozessen, der Speicherverwaltung und der Interprozess-Kommunikation zu. Wir haben ganz gezielt darauf verzichtet, auf ein besonderes Betriebssystem einzugehen, sondern wollten vielmehr die grundsätzlichen Mechanismen eines Betriebssystems darstellen. Hierzu haben wir besonders Herrn Univ.-Prof. Dr. U. Schmid für den Beitrag zu dem

Abschnitt „Betriebssysteme“ zu danken, den wir wiederholt in mehrere Auflagen aufgenommen haben.

Unser Dank gebührt weiter Herrn Dipl.-Ing. J. Klasek für die abschnittsweise Durchsicht und teilweise Überarbeitung des Abschnittes „Betriebssysteme und Systemsoftware“ im Buch „Informatik“ (dritte Auflage). Diesen Abschnitt haben wir nochmals angepasst.

Das vorliegende Buch wendet sich sowohl an Fachkräfte aus Wirtschaft und Industrie als auch an Studierende der Informatik. Das Ziel dieses Buches ist es, dem künftigen Informatiker ingenieurmäßiges Wissen auf dem Gebiet der technischen Informatik zu vermitteln.

Wann immer man ein Buch schreibt, so gilt auch hier der Grundsatz aus dem Bereich der Software-Entwicklung, „dass Software niemals wirklich fehlerfrei ist“ (engl. *"Software will never be errorfree"*). Das trifft ebenso auch für das vorliegende Buch zu. Dieser Erfahrung sind wir auch bei der Verfassung dieses Buches gefolgt und haben deshalb eine e-mail-Adresse unter

[technische-informatik@auto.tuwien.ac.at](mailto:technische-informatik@auto.tuwien.ac.at)

eingerichtet, wo wir gern Korrekturen und Anregungen von unseren Lesern erwarten.

Unser besonderer Dank gilt Herrn Ch. Mörz und Herrn Th. Volpini für die Erstellung des Manuskriptes und der zahlreichen Abbildungen. Darüber hinaus haben wir dem Verlag - vertreten durch Frau Schilgerius - für die bisherige sehr erfolgreiche Zusammenarbeit besonders zu danken.

Gerhard H. Schildt

Pressbaum

Alexander Redlein

Klosterneuburg

Daniela Kahn

Brunn am Gebirge

Pressbaum, Februar 2003

# **Vorwort zur 2. Auflage**

Nach der guten Aufnahme der ersten Auflage unseres Buches „Einführung in die Technische Informatik“ haben wir eine Überarbeitung des Inhaltes zur Aktualisierung wie auch zur Beseitigung von Fehlern vorgenommen. So haben wir neu ein Kapitel über USB und FireWire aufgenommen, sodann ein eigenes Kapitel über Netzwerke eingefügt, das auf die neuesten Standards Bezug nimmt. Hier werden Architekturen und Protokolle detailliert vorgestellt.

Der Abschnitt „Betriebssysteme und Systemsoftware“ erfuhr eine generelle Überarbeitung mit dem Ziel der Aktualisierung. Hier haben wir neu einen Abschnitt zum Thema „Sicherheit“ aus aktuellem Anlass aufgenommen und erhoffen uns dadurch eine hinreichende Akzeptanz von Lesern, die insbesondere am Thema „Security“ interessiert sind.

Wie schon bei der ersten Auflage stellen wir weiterhin die e-mail-Adresse unter

[technische-informatik@auto.tuwien.ac.at](mailto:technische-informatik@auto.tuwien.ac.at)

zur Verfügung, wo wir gern Korrekturen und Anregungen von unseren Lesern erwarten.

Unser besonderer Dank gilt Herrn Univ. Prof. Steininger für Unterlagen zum Thema VHDL und Herrn E. Hirsch für die Bearbeitung des Manuskriptes und der zahlreichen Abbildungen. Weiter möchten wir Frau Schilgerius vom Springer-Verlag unseren besonderen Dank für die bisher erfolgreiche Zusammenarbeit aussprechen.

Gerhard H. Schildt      Daniela Kahn

Christopher Kruegel      Christian Moerz

# Inhaltsverzeichnis

|                                                             |           |

|-------------------------------------------------------------|-----------|

| <b>1 Einleitung</b>                                         | <b>1</b>  |

| <b>Hardware</b>                                             | <b>5</b>  |

| <b>2 Logische Schaltungen</b>                               | <b>7</b>  |

| 2.1 Grundbegriffe . . . . .                                 | 7         |

| 2.1.1 Fan Out . . . . .                                     | 11        |

| 2.1.2 Schaltkreisfamilien . . . . .                         | 13        |

| 2.1.3 Signalnamen und Signalverbindungen . . . . .          | 14        |

| 2.2 Realisierung von Funktionen . . . . .                   | 15        |

| 2.2.1 Halbaddierer . . . . .                                | 16        |

| 2.2.2 Volladdierer . . . . .                                | 17        |

| 2.2.3 Codierer . . . . .                                    | 19        |

| 2.2.4 Decodierer . . . . .                                  | 21        |

| 2.2.5 Multiplexer . . . . .                                 | 22        |

| 2.2.6 Demultiplexer . . . . .                               | 24        |

| 2.3 Sequenzielle Logik . . . . .                            | 24        |

| 2.3.1 Latches . . . . .                                     | 25        |

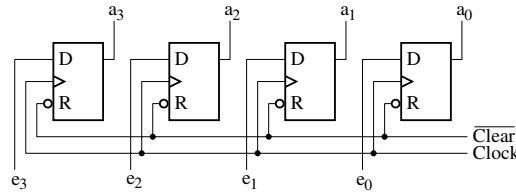

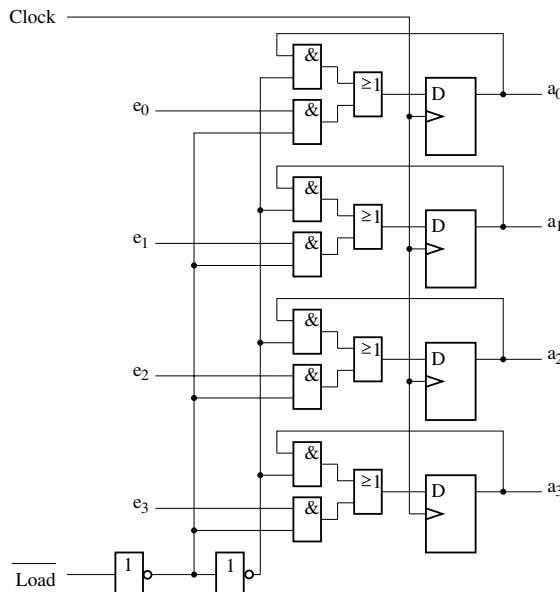

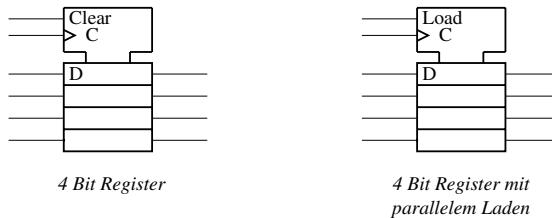

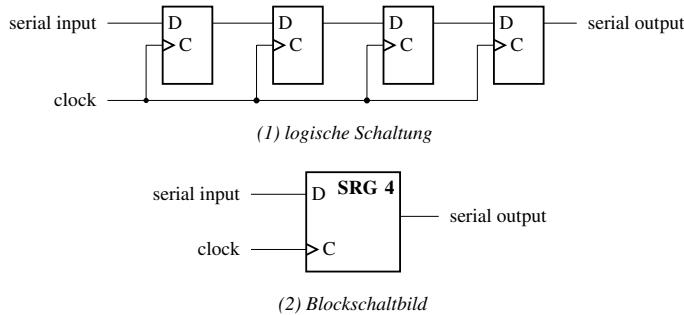

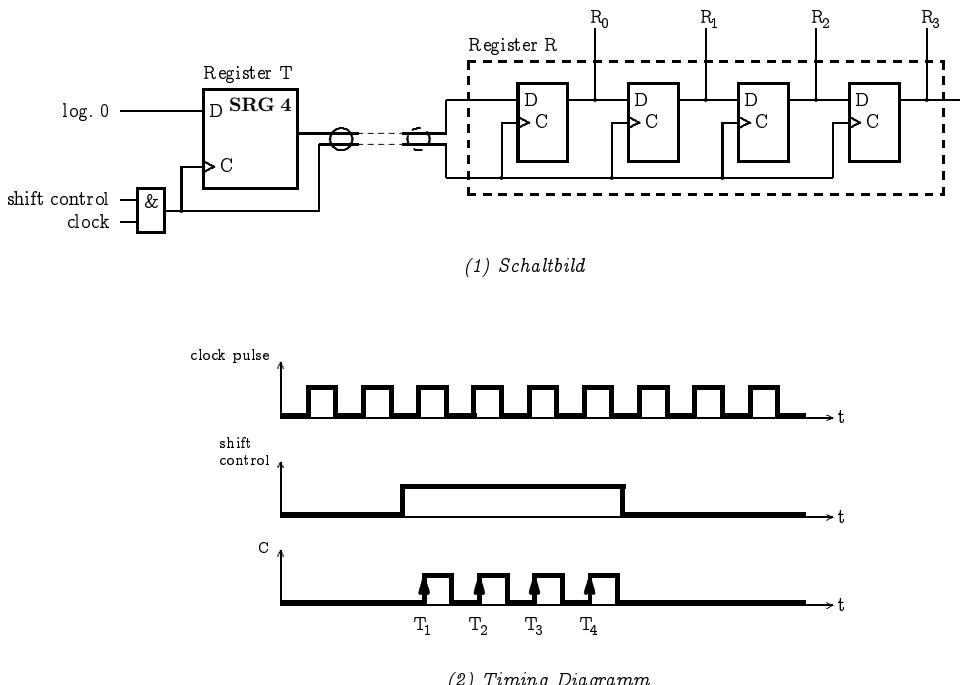

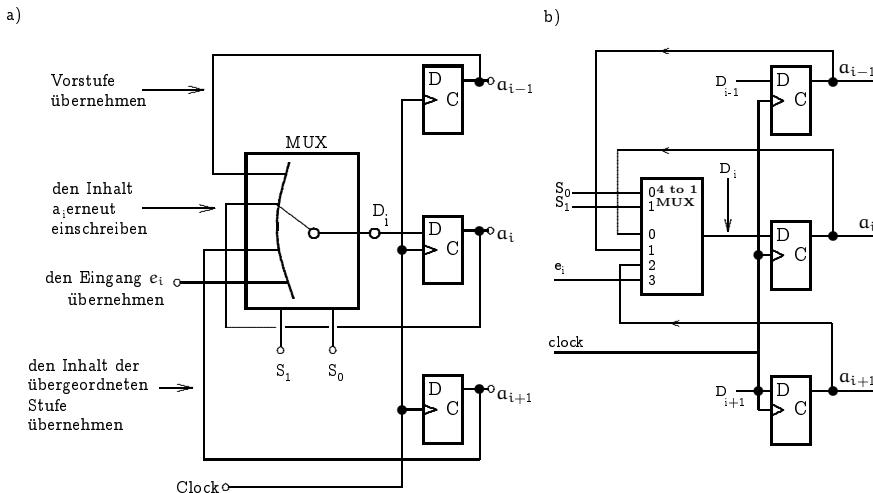

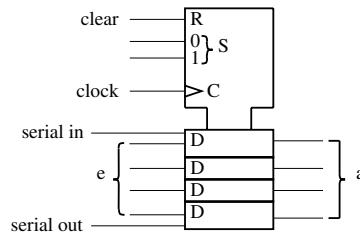

| 2.3.2 Register . . . . .                                    | 30        |

| 2.3.3 Zähler . . . . .                                      | 34        |

| 2.4 Signalverarbeitende elektronische Schaltungen . . . . . | 37        |

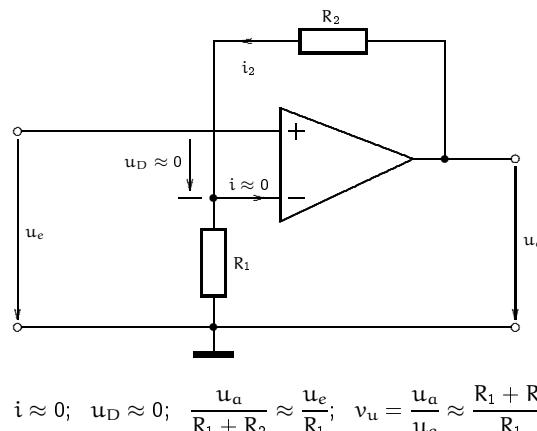

| 2.4.1 Operationsverstärker . . . . .                        | 37        |

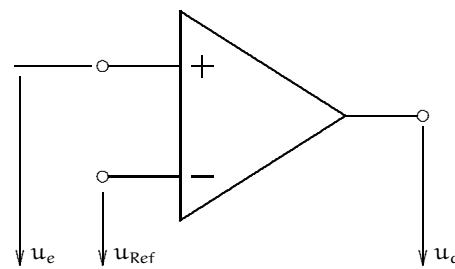

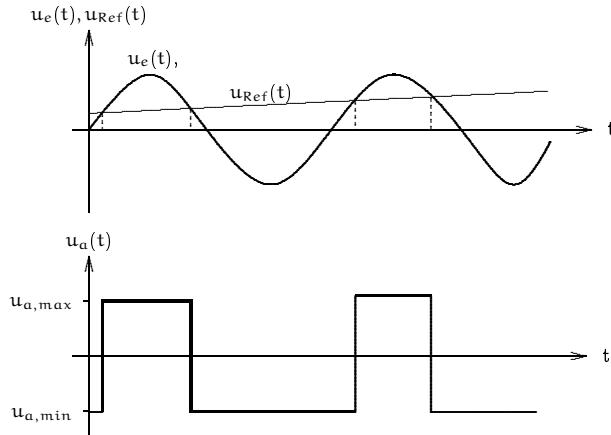

| 2.4.2 Komparatoren . . . . .                                | 39        |

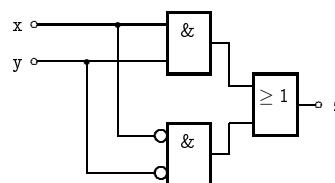

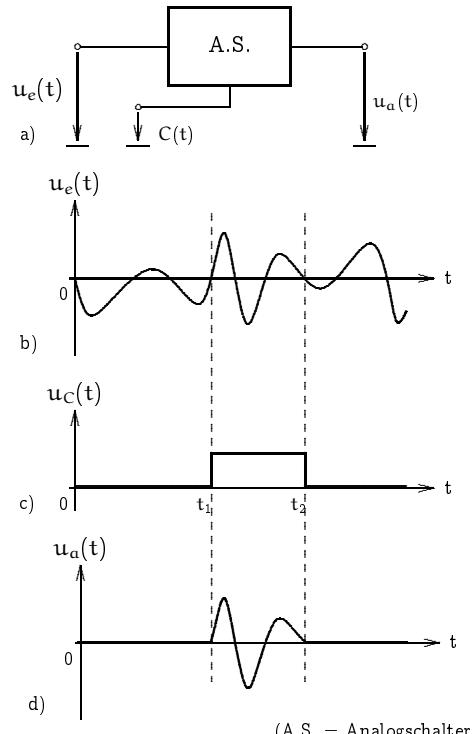

| 2.4.3 Torschaltungen . . . . .                              | 41        |

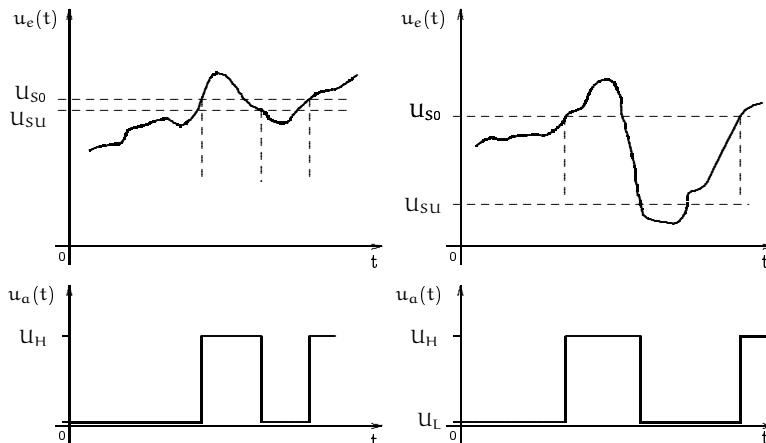

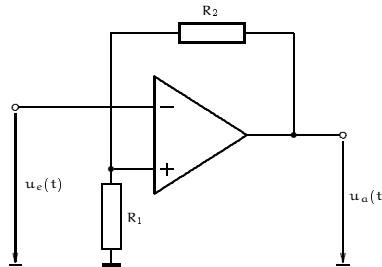

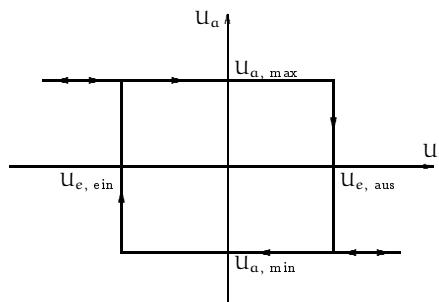

| 2.4.4 Schmitt-Trigger . . . . .                             | 42        |

| 2.4.5 Zero-Crossing-Detector . . . . .                      | 48        |

| 2.4.6 Univibrator . . . . .                                 | 48        |

| 2.4.7 Signalgeneratoren . . . . .                           | 50        |

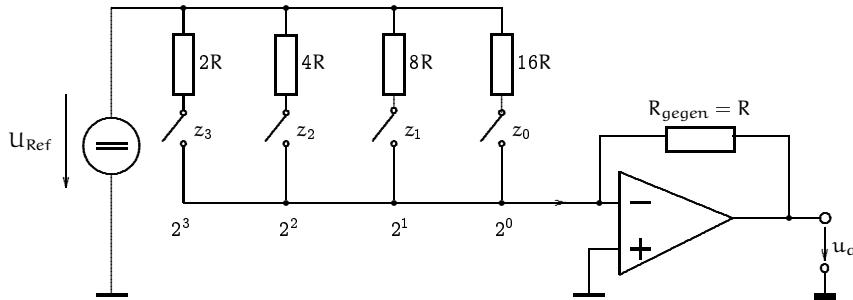

| 2.4.8 Analog-Digital-Umsetzer . . . . .                     | 55        |

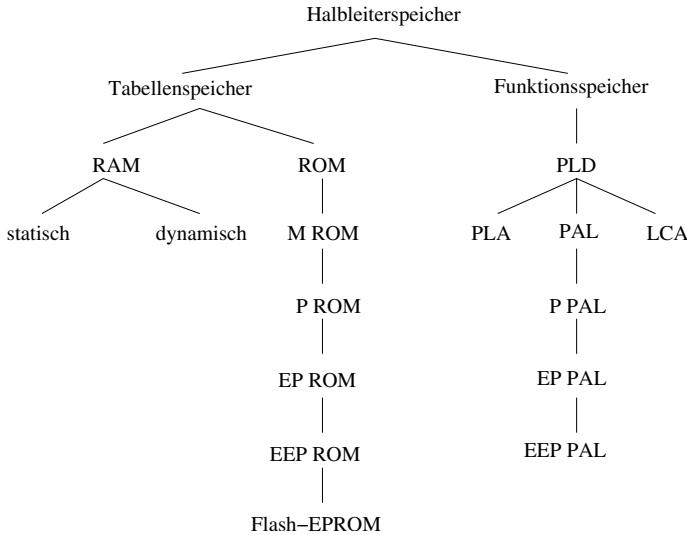

| 2.5 Halbleiterspeicher . . . . .                            | 57        |

| 2.5.1 Tabellenspeicher . . . . .                            | 57        |

| 2.5.2 Tristate Outputs . . . . .                            | 60        |

| 2.5.3 Open-Collector-Schaltungen . . . . .                  | 61        |

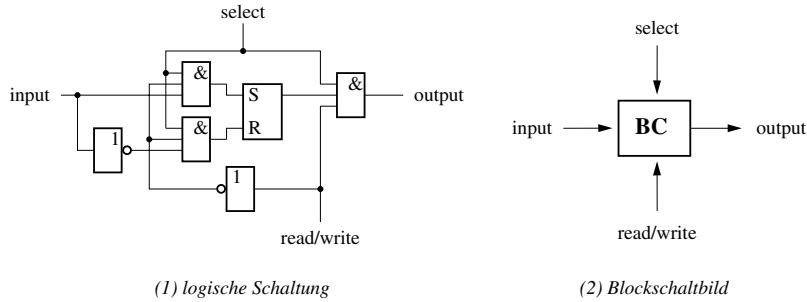

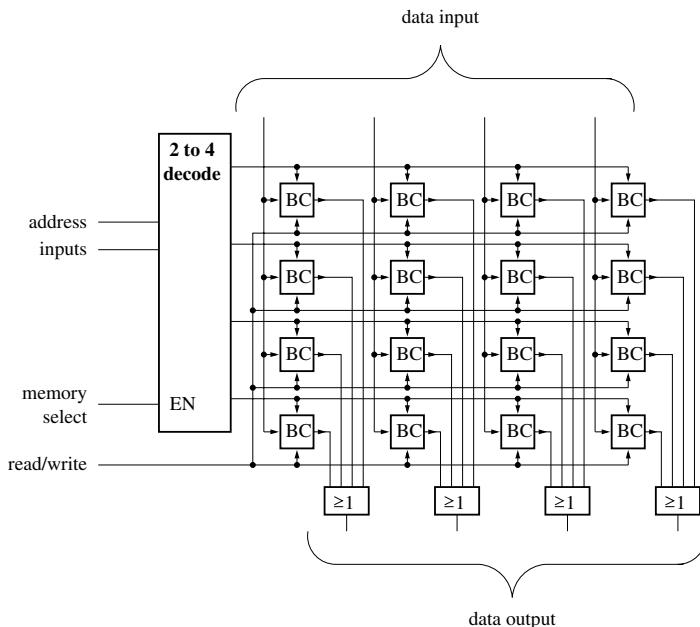

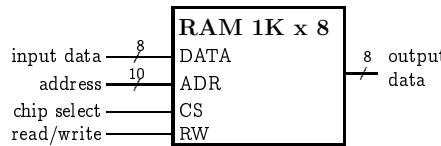

| 2.5.4 Speicherbausteine . . . . .                           | 62        |

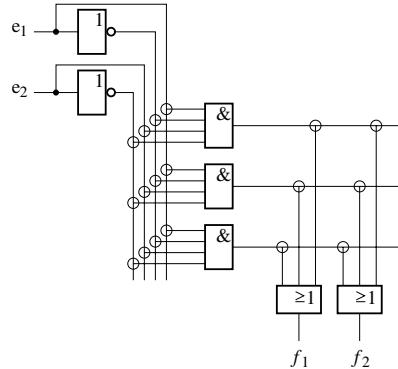

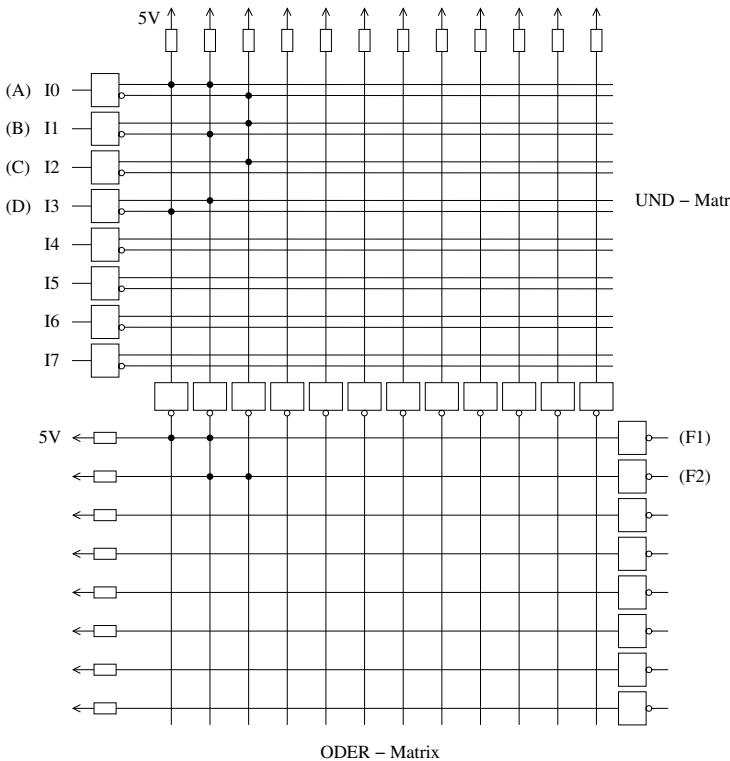

| 2.5.5 Funktionsspeicher (ASICs) . . . . .                   | 64        |

| <b>3 VHDL</b>                                               | <b>69</b> |

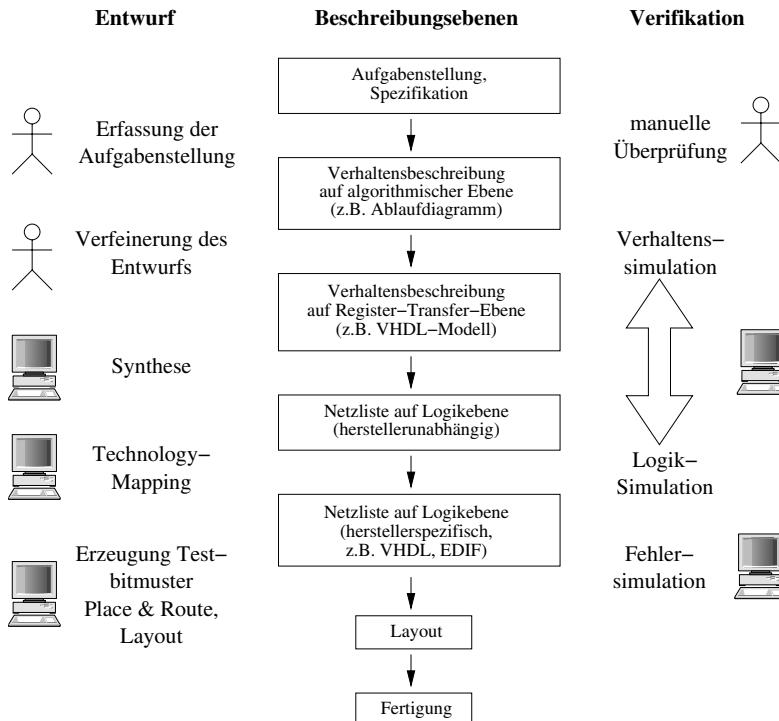

| 3.1 Entwurfssichten . . . . .                               | 69        |

| 3.2 Entwurfsebenen . . . . .                                | 71        |

| 3.2.1 Systemebene . . . . .                                 | 71        |

| 3.2.2 Algorithmische Ebene . . . . .                        | 71        |

| 3.2.3 Register-Transfer-Ebene . . . . .                     | 71        |

|          |                                                                         |            |

|----------|-------------------------------------------------------------------------|------------|

| 3.2.4    | Logikebene . . . . .                                                    | 71         |

| 3.2.5    | Schaltkreisebene . . . . .                                              | 72         |

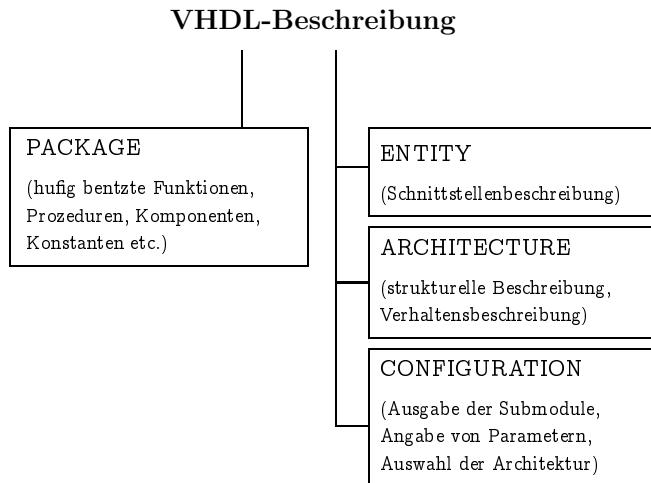

| 3.2.6    | Der Aufbau einer VHDL-Beschreibung . . . . .                            | 73         |

| 3.3      | Bestandteile einer VHDL-Beschreibung . . . . .                          | 74         |

| 3.3.1    | Entwurfssichten in VHDL . . . . .                                       | 74         |

| 3.3.2    | Entwurfsebenen in VHDL . . . . .                                        | 75         |

| 3.3.3    | Design-Methodik mit VHDL . . . . .                                      | 76         |

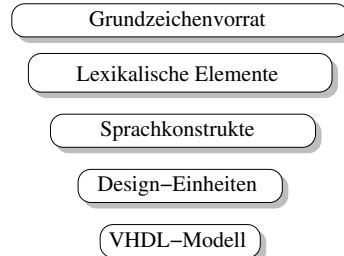

| 3.3.4    | Die Sprache VHDL . . . . .                                              | 77         |

| 3.3.5    | Der Aufbau eines VHDL-Modells . . . . .                                 | 77         |

| 3.4      | Beispiele . . . . .                                                     | 78         |

| 3.4.1    | (2-von-3) Voter . . . . .                                               | 78         |

| 3.4.2    | Siebensegment-Decoder . . . . .                                         | 79         |

| 3.4.3    | Input-Synchronisation . . . . .                                         | 80         |

| 3.4.4    | Tasten-Entpreller . . . . .                                             | 82         |

| 3.5      | Bewertung von VHDL . . . . .                                            | 84         |

| <b>4</b> | <b>Mikroprozessoren</b>                                                 | <b>87</b>  |

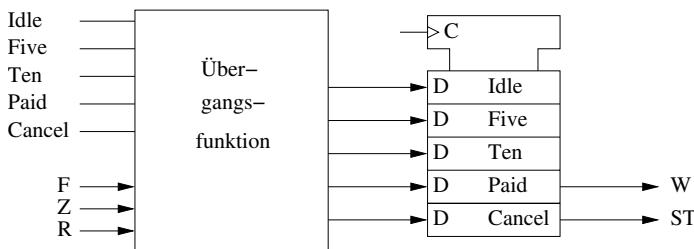

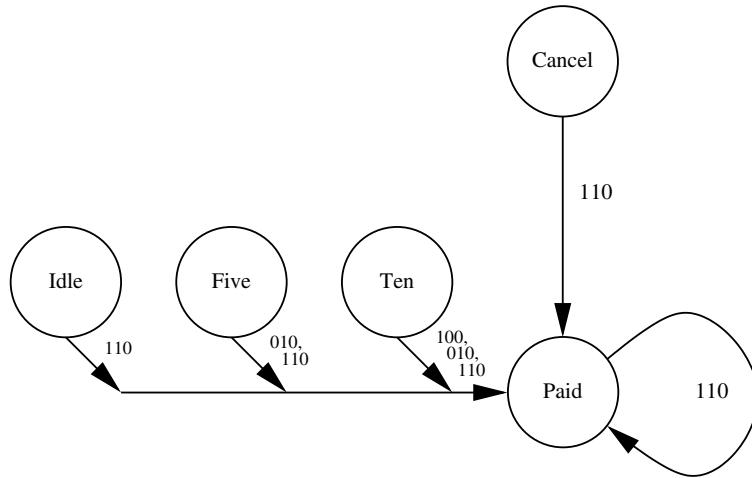

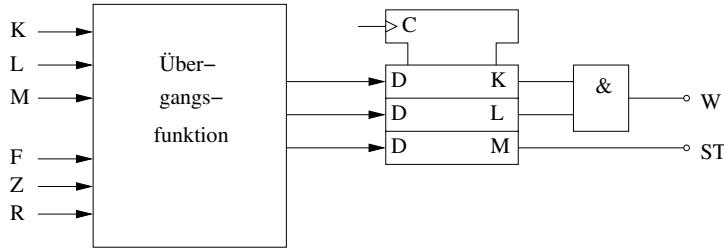

| 4.1      | Endliche Automaten . . . . .                                            | 87         |

| 4.2      | Das Moore-Schaltwerk . . . . .                                          | 92         |

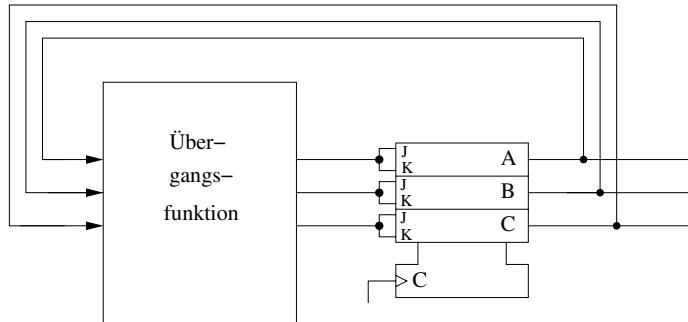

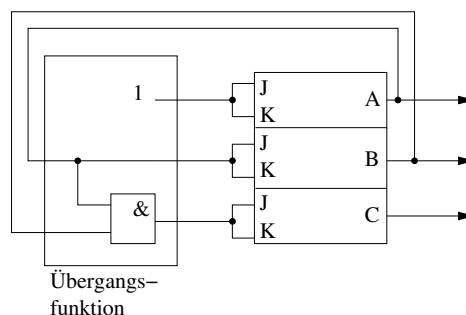

| 4.2.1    | Schaltwerk . . . . .                                                    | 93         |

| 4.2.2    | Die Grundschaltung des Moore-Schaltwerkes . . . . .                     | 93         |

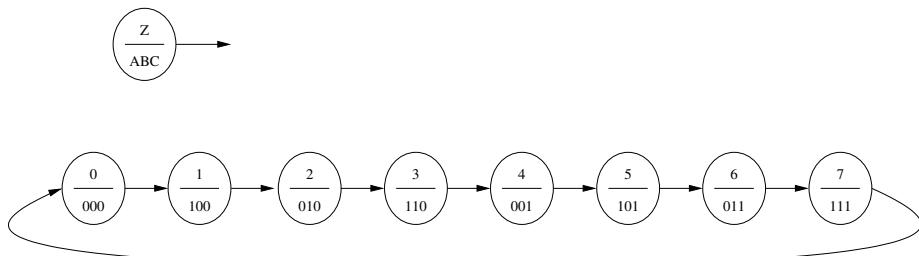

| 4.2.3    | Schaltwerksbeschreibung durch den Zustandsgraphen . . . . .             | 95         |

| 4.2.4    | Alternativen zum Zustandsgraph . . . . .                                | 98         |

| 4.2.5    | Realisierung mit „(1 aus n)“ und „dichter“ Zustandscodierung . . . . .  | 99         |

| 4.2.6    | Der zeitliche Ablauf im Moore-Schaltwerk . . . . .                      | 103        |

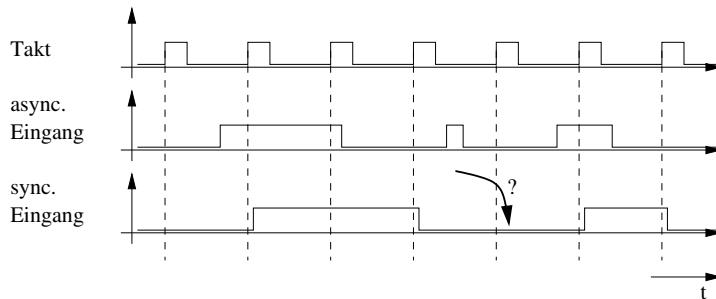

| 4.2.7    | Synchronisierung von asynchronen Eingangssignalen . . . . .             | 104        |

| 4.2.8    | Systematische Schaltwerksentwicklung . . . . .                          | 105        |

| 4.3      | Das Mealy-Schaltwerk . . . . .                                          | 116        |

| 4.3.1    | Die Schaltung eines Mealy-Schaltwerks . . . . .                         | 116        |

| 4.3.2    | Beschreibung des Mealy-Schaltwerkes durch den Zustandsgraphen . . . . . | 118        |

| 4.3.3    | Mealy-Moore-Transformation . . . . .                                    | 119        |

| 4.3.4    | Die maximale Taktfrequenz des Mealy-Schaltwerkes . . . . .              | 120        |

| 4.3.5    | Überwachung einer Einschaltreihenfolge . . . . .                        | 121        |

| 4.3.6    | Erkennen der Eingangsfolge 1011 . . . . .                               | 123        |

| 4.4      | Prozessoren . . . . .                                                   | 125        |

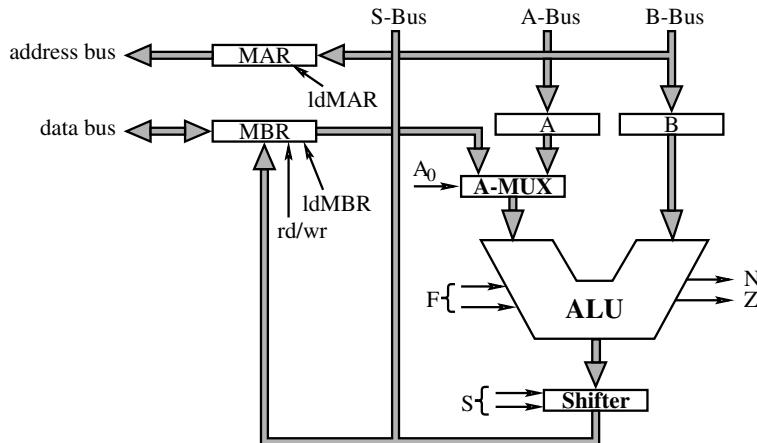

| 4.4.1    | Arithmetic Logic Unit . . . . .                                         | 126        |

| 4.4.2    | Register File und Busverbindungen . . . . .                             | 129        |

| 4.4.3    | Speicheranbindung . . . . .                                             | 132        |

| 4.4.4    | Control Unit . . . . .                                                  | 135        |

| 4.4.5    | Mikro-Programm . . . . .                                                | 139        |

| 4.4.6    | Very Large Scale Integration (VLSI) . . . . .                           | 142        |

| <b>5</b> | <b>Computersysteme</b>                                                  | <b>143</b> |

| 5.1      | Prozessoren . . . . .                                                   | 143        |

| 5.1.1    | Maschinen-Code . . . . .                                                | 143        |

| 5.1.2    | Adressierungsarten . . . . .                                            | 154        |

| 5.1.3    | Architekturen . . . . .                                                 | 158        |

| 5.1.4    | Parallelverarbeitung innerhalb eines Rechners . . . . .                 | 160        |

| 5.1.5    | CISC versus RISC . . . . .                                              | 165        |

| 5.2      | Speicher . . . . .                                                      | 166        |

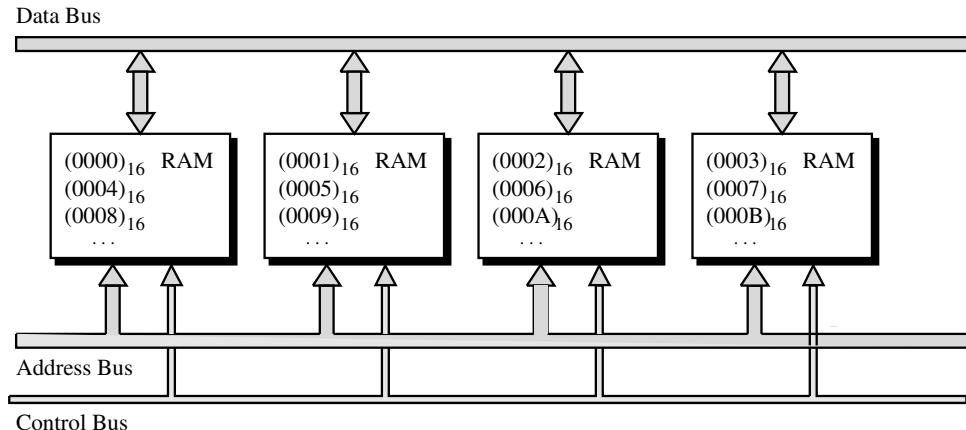

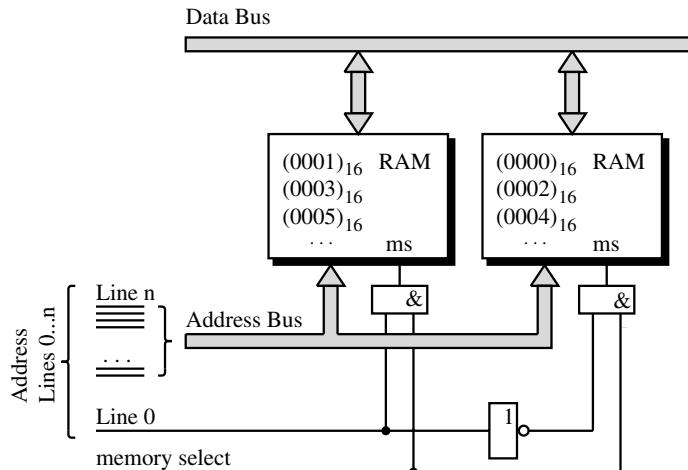

| 5.2.1    | Interleaved Memory . . . . .                                            | 167        |

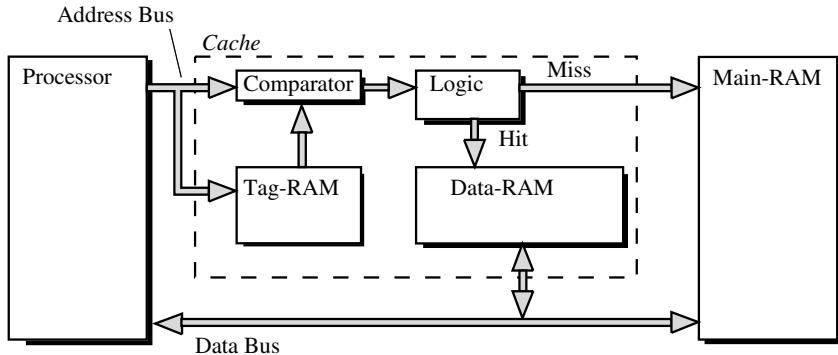

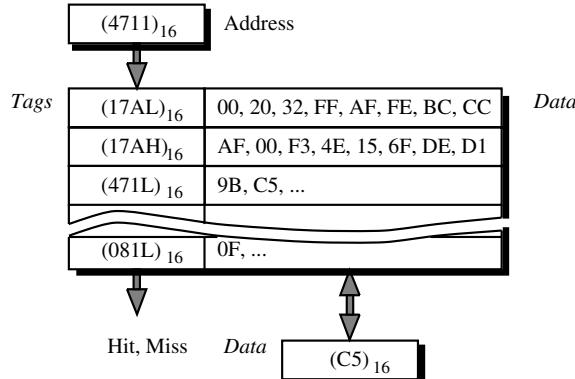

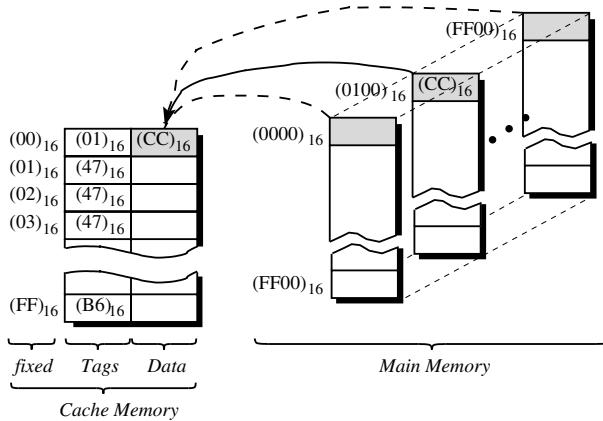

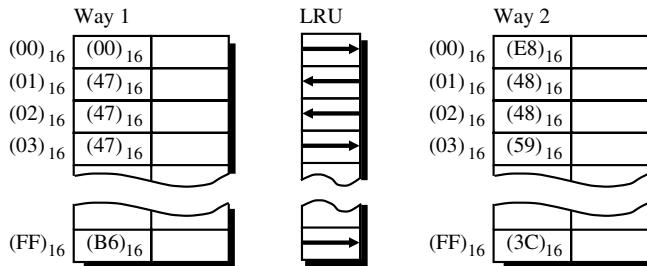

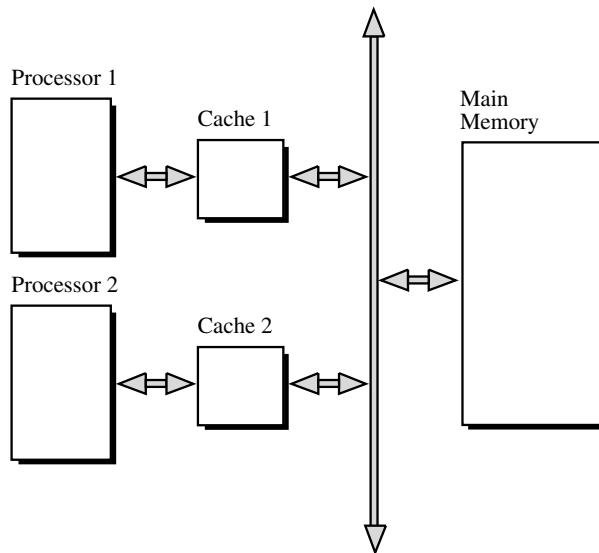

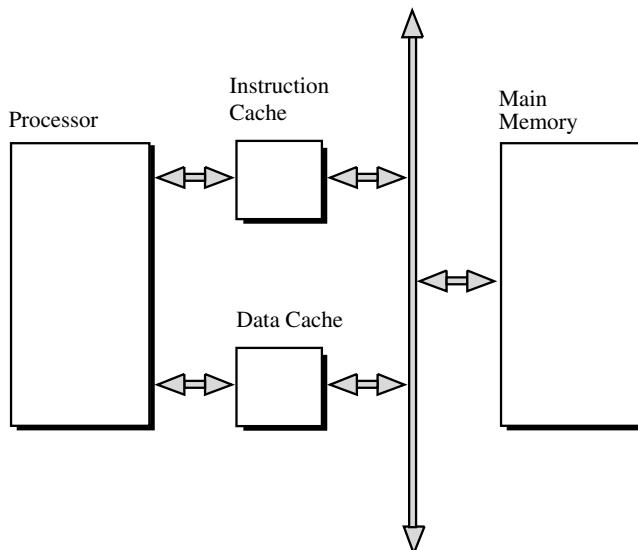

| 5.2.2    | Caches . . . . .                                                        | 169        |

| 5.2.3    | Direct Memory Access (DMA) . . . . .                                    | 174        |

---

|                                                                                |            |

|--------------------------------------------------------------------------------|------------|

| 5.2.4 Controller und Co-Prozessoren . . . . .                                  | 175        |

| 5.2.5 Interconnection . . . . .                                                | 177        |

| 5.3 Periphere Geräte . . . . .                                                 | 178        |

| 5.3.1 Externspeicher . . . . .                                                 | 179        |

| 5.3.2 Dialoggeräte . . . . .                                                   | 185        |

| 5.4 USB und FireWire® . . . . .                                                | 191        |

| 5.4.1 USB-Datenübertragung . . . . .                                           | 193        |

| 5.4.2 USB-Hardware-Architektur . . . . .                                       | 195        |

| 5.4.3 USB Kommunikation . . . . .                                              | 197        |

| 5.4.4 FireWire® . . . . .                                                      | 201        |

| <b>Netzwerke</b>                                                               | <b>205</b> |

| <b>6 Aufbau</b>                                                                | <b>207</b> |

| 6.1 Netzwerktypen . . . . .                                                    | 207        |

| 6.2 Circuit- und Packet-Switching . . . . .                                    | 208        |

| 6.3 Standardisierung . . . . .                                                 | 209        |

| <b>7 Architekturen</b>                                                         | <b>213</b> |

| 7.1 OSI Reference Model . . . . .                                              | 214        |

| 7.2 Kabel und Stecker . . . . .                                                | 218        |

| 7.2.1 BNC und Thin Ethernet . . . . .                                          | 218        |

| 7.2.2 Twisted Pair und RJ-45 . . . . .                                         | 218        |

| 7.3 LAN und WAN . . . . .                                                      | 219        |

| 7.3.1 ARPANET . . . . .                                                        | 219        |

| 7.3.2 Ethernet . . . . .                                                       | 220        |

| 7.3.3 Fast Ethernet . . . . .                                                  | 221        |

| 7.3.4 Token Ring . . . . .                                                     | 221        |

| 7.3.5 WaveLAN . . . . .                                                        | 223        |

| 7.4 Digital Subscriber Line (DSL) . . . . .                                    | 225        |

| 7.4.1 Funktionsweise . . . . .                                                 | 225        |

| 7.4.2 Bluetooth . . . . .                                                      | 226        |

| 7.4.3 ADSL und SDSL . . . . .                                                  | 227        |

| <b>8 Protokolle</b>                                                            | <b>229</b> |

| 8.1 Internet Protocol (IP) . . . . .                                           | 229        |

| 8.1.1 TCP . . . . .                                                            | 236        |

| 8.1.2 UDP . . . . .                                                            | 237        |

| 8.2 IPv6 . . . . .                                                             | 238        |

| <b>Betriebssysteme und Systemsoftware</b>                                      | <b>241</b> |

| <b>9 Übersicht</b>                                                             | <b>243</b> |

| 9.1 Ziele und Funktionen von Betriebssystemen . . . . .                        | 243        |

| 9.2 Betriebssystemschnittstelle zwischen Benutzer und Computersystem . . . . . | 244        |

| 9.3 Betriebssystemaufrufe . . . . .                                            | 245        |

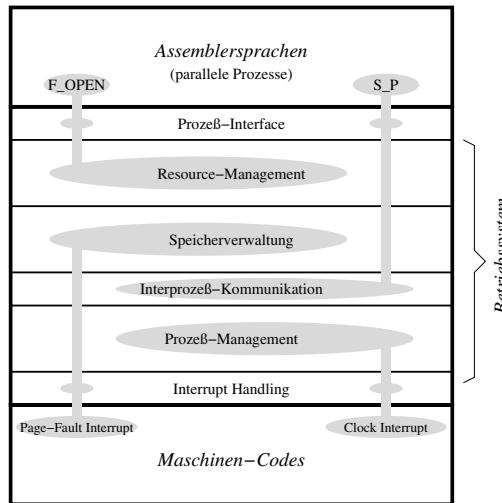

| 9.4 Betriebssystem-Struktur . . . . .                                          | 246        |

| 9.4.1 Konsistente Schichtung . . . . .                                         | 247        |

| 9.4.2 Quasikonsistente Schichtung . . . . .                                    | 247        |

| 9.4.3 Schichtenmodell . . . . .                                                | 247        |

| <b>10 Prozesse</b>                                                             | <b>251</b> |

|                                                       |            |

|-------------------------------------------------------|------------|

| 10.1 Parallelität . . . . .                           | 252        |

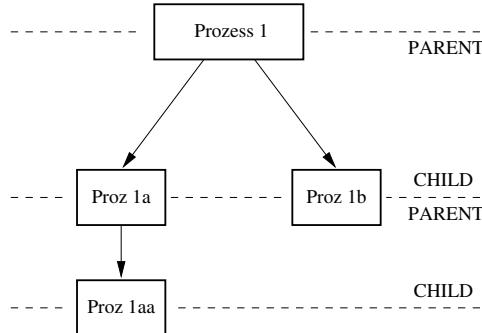

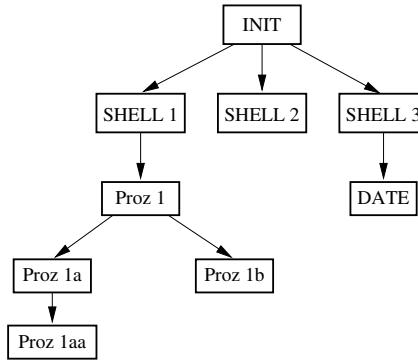

| 10.2 Prozesshierarchien . . . . .                     | 254        |

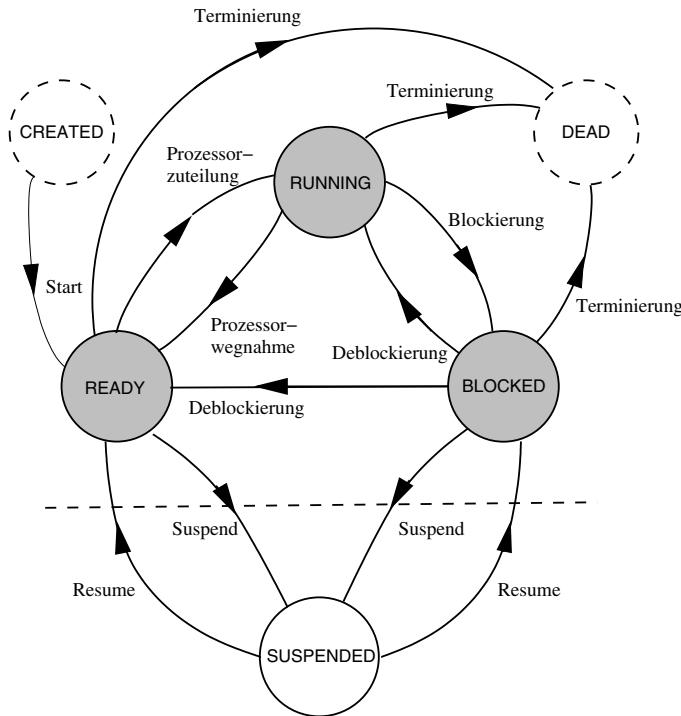

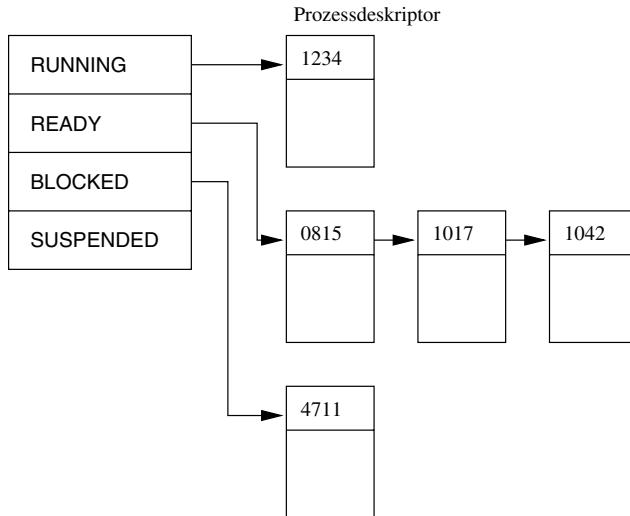

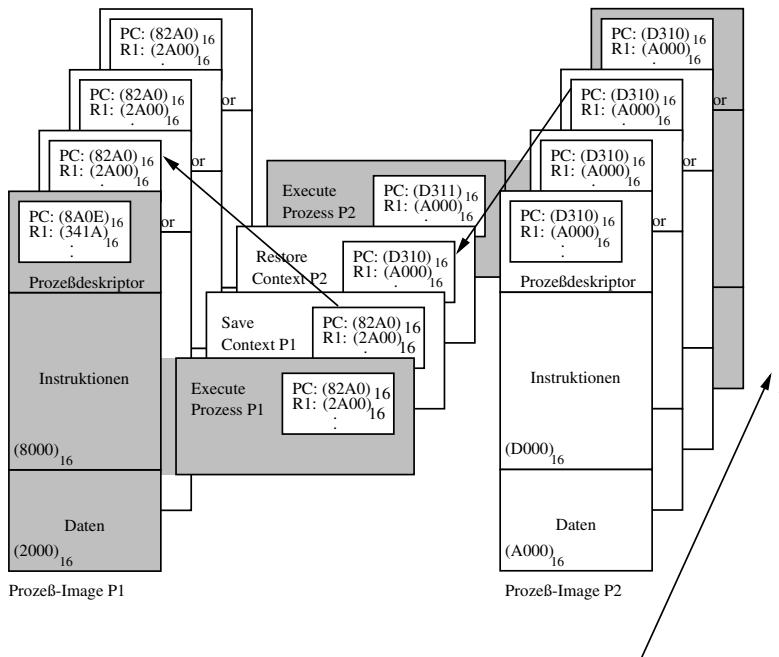

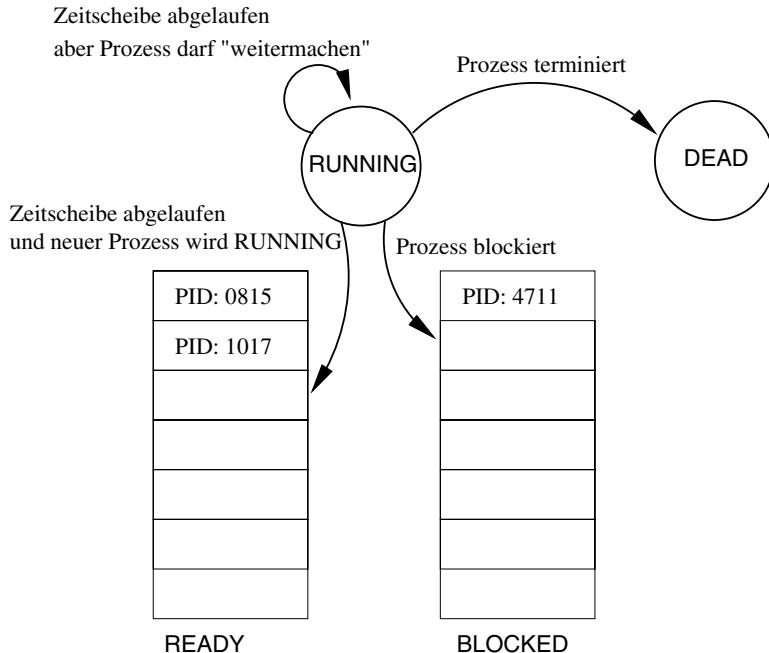

| 10.3 Prozesszustände . . . . .                        | 256        |

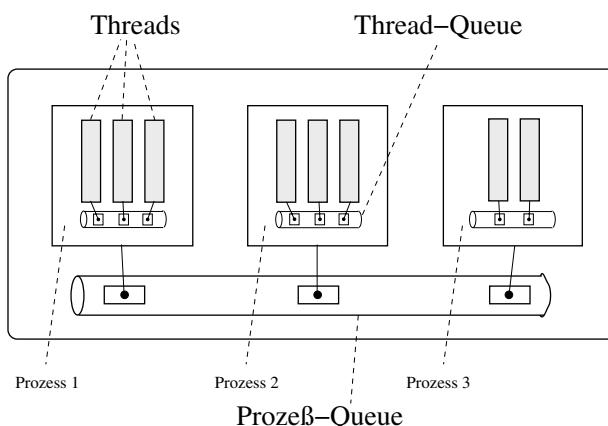

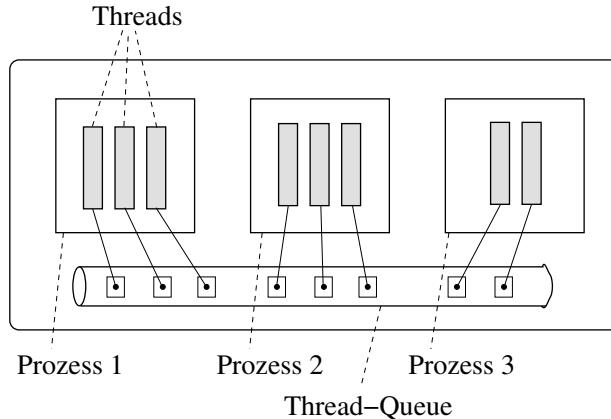

| 10.4 Threads . . . . .                                | 262        |

| 10.5 Scheduling . . . . .                             | 267        |

| 10.5.1 Prozess-Scheduling . . . . .                   | 268        |

| 10.5.2 Thread-Scheduling . . . . .                    | 271        |

| 10.5.3 Job-Scheduling . . . . .                       | 272        |

| <b>11 Interprozess-Kommunikation</b>                  | <b>275</b> |

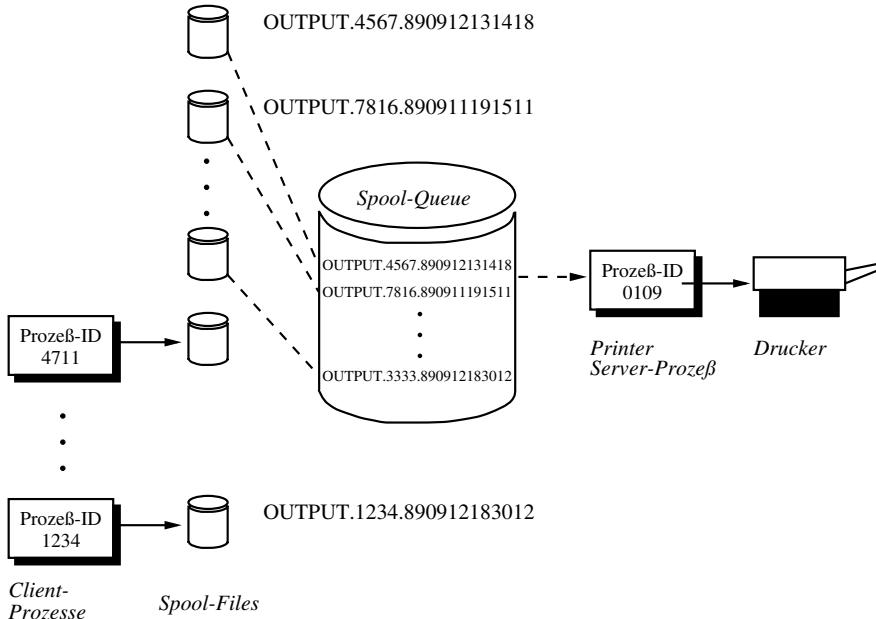

| 11.1 Server-Prozesse . . . . .                        | 275        |

| 11.2 Synchrone Methoden . . . . .                     | 279        |

| 11.2.1 Semaphore . . . . .                            | 280        |

| 11.2.2 Message Passing . . . . .                      | 284        |

| 11.2.3 Höhere Mechanismen . . . . .                   | 287        |

| 11.3 Asynchrone Methoden . . . . .                    | 287        |

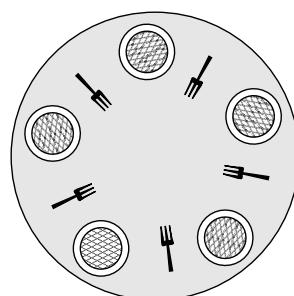

| 11.4 Deadlocks . . . . .                              | 288        |

| <b>12 Speicherverwaltung</b>                          | <b>293</b> |

| 12.1 Virtuelle Adresszuordnung . . . . .              | 295        |

| 12.2 Physikalische Adresszuordnung . . . . .          | 300        |

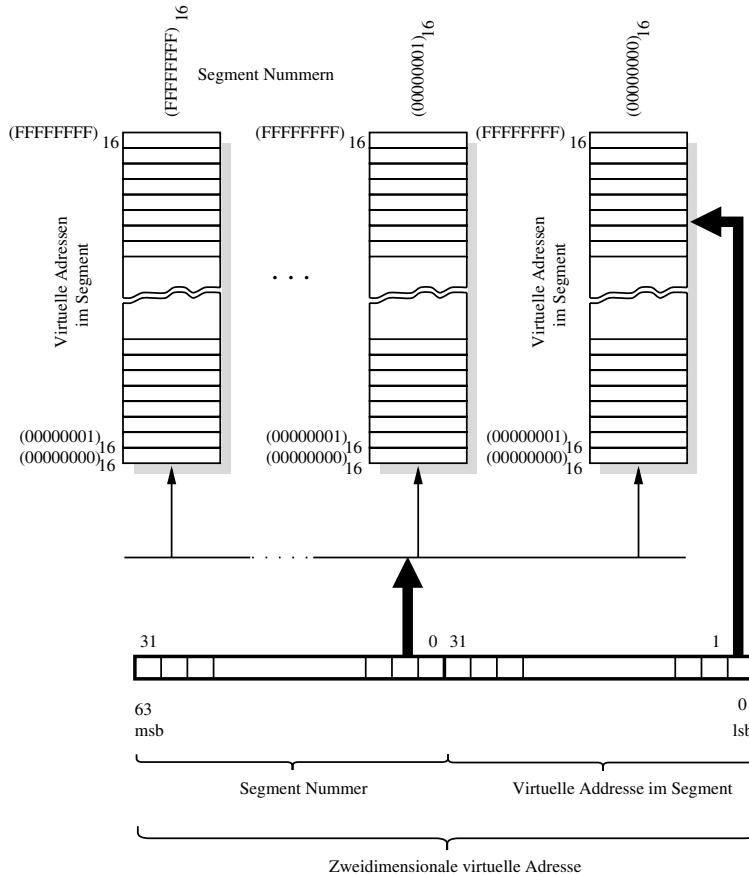

| 12.2.1 Swapping . . . . .                             | 300        |

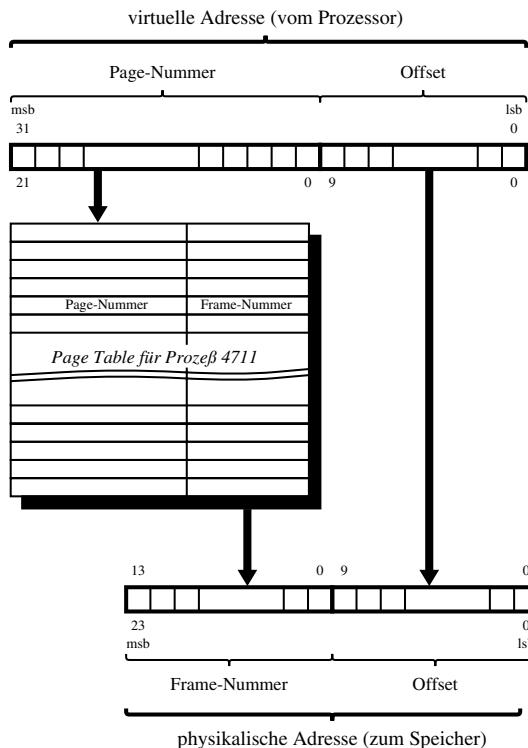

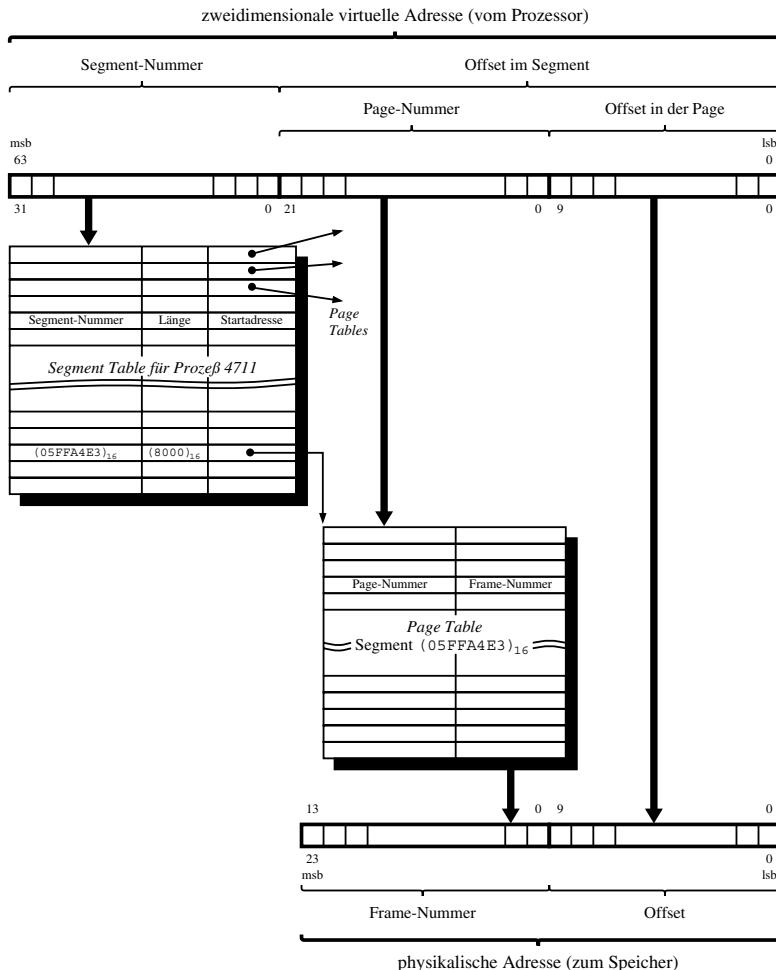

| 12.2.2 Paging . . . . .                               | 303        |

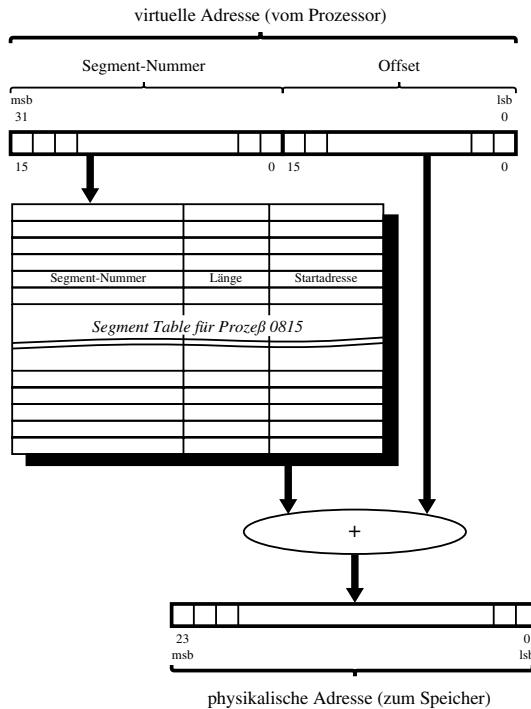

| 12.2.3 Segmentierung . . . . .                        | 307        |

| <b>13 Ressourcen-Management</b>                       | <b>311</b> |

| 13.1 Objektorientierung in Betriebssystemen . . . . . | 311        |

| 13.2 Device-Unabhängigkeit . . . . .                  | 312        |

| 13.3 File Management . . . . .                        | 314        |

| <b>14 Sicherheit</b>                                  | <b>329</b> |

| 14.1 Zugriffsschutz . . . . .                         | 331        |

| 14.2 Zugriffskontrolle . . . . .                      | 333        |

| 14.3 Design Prinzipien . . . . .                      | 336        |

| 14.4 Trusted Computing . . . . .                      | 336        |

| <b>15 Schlussbetrachtung</b>                          | <b>339</b> |

# 1 Einleitung

*Software und Hardware sind Menschenware.*

E.H. Bellermann,

Dichter und Bauingenieur,

aus „Mensch's Tierleben“

Das vorliegende Buch „Einführung in die Technische Informatik“ deckt im wesentlichen sowohl Computer-Hardware als auch Betriebssysteme und Systemsoftware ab. Im Abschnitt über Computer-Hardware werden wir zeigen, wie man elektronische Bauelemente einsetzt, um Rechnersysteme aufzubauen. Wir werden den Leser in die Lage versetzen, die technischen Möglichkeiten und Grenzen solcher Systeme zu verstehen und zu bewerten. Auf diese Weise können Leistungsmerkmale heutiger Rechnersysteme besser beurteilt werden. Der Stoff des vorliegenden Buches ist auf das Informatikstudium ausgerichtet und beschränkt sich auf grundlegende elektrotechnische Kenntnisse. Sofern weiterführende Kenntnisse erforderlich sind, werden sie kurz anwendungsbezogen eingeführt.

Weiter wollen wir davon ausgehen, dass die erforderlichen Kenntnisse aus dem Buch G.H. Schildt et al. „Informatik Grundlagen“ bereits vorliegen. Dort haben wir die Gesetze der Booleschen Algebra kennengelernt, die uns jetzt als Grundlage für den Aufbau logischer Schaltungen dienen sollen. Die Problemanalyse führt meist zu einer Wahrheitstabelle, die wir dann in eine logische Funktion umsetzen werden. Vielfach kann diese Funktion noch minimiert werden. Auch hierzu haben wir in dem vorangegangenen Buch „Gerhard H.Schildt et al. Informatik Grundlagen“ bereits die entsprechenden Verfahren wie den Algorithmus nach Quine McCluskey oder das KV-Diagramm nach Karnaugh und Veitch kennen gelernt.

Es sind aber noch andere Aspekte der Realisierung von logischen Funktionen nach der Booleschen Algebra von Bedeutung. Nehmen wir einmal an, wir würden versuchen, einen Volladdierer für Dualzahlen zu entwerfen. Nach einer genauen Problemanalyse haben wir nun Boolesche Ausdrücke für die Summen- und Übertragsbildung bestimmt. So können wir zwar die Funktionalität eines Volladdierers gut beschreiben (was wir im übrigen noch tun werden!), nicht aber konkrete Fragen beantworten wie z.B.

„Wie schnell kann man nun mit dieser Schaltung eine Addition ausführen?“ oder „Wie viele Eingänge können an den Ausgang für die Summenbildung angeschlossen werden, ohne das die Funktionalität beeinflusst wird?“

Hierfür muss man sich mit den konkreten technischen Eigenschaften der digitalen Bausteine auseinandersetzen. Wir werden versuchen, die folgenden Fragen zu beantworten:

- Wie wird aus einem analogen Bauteil ein digitales?

- Was bedeutet es, wenn man logisch 0 und logisch 1 vertauscht?

- Wie stark darf ein Ausgang belastet werden?

- Wie wird die Geschwindigkeit eines Gatters angegeben?

- Warum darf man normale Ausgänge für Busanwendungen nicht miteinander verbinden?

Für zahlreiche Aufgabenstellungen der Digitaltechnik sind logische Funktionen allein nicht ausreichend; vielmehr braucht man Schaltwerke, die *gedächtnisbehaftet* sind. Dadurch fällt es dem

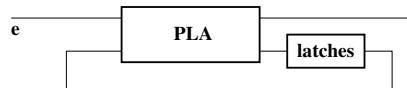

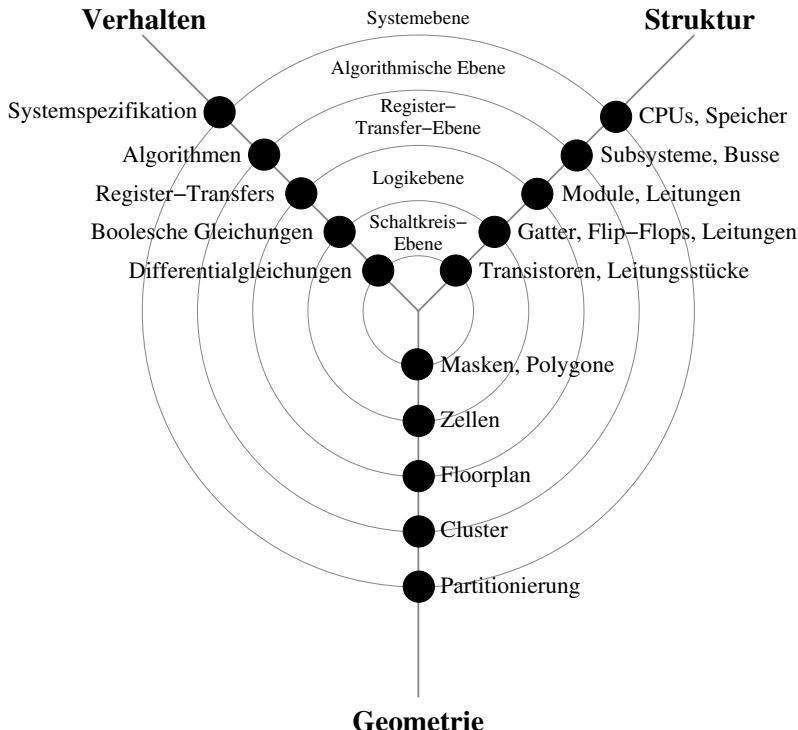

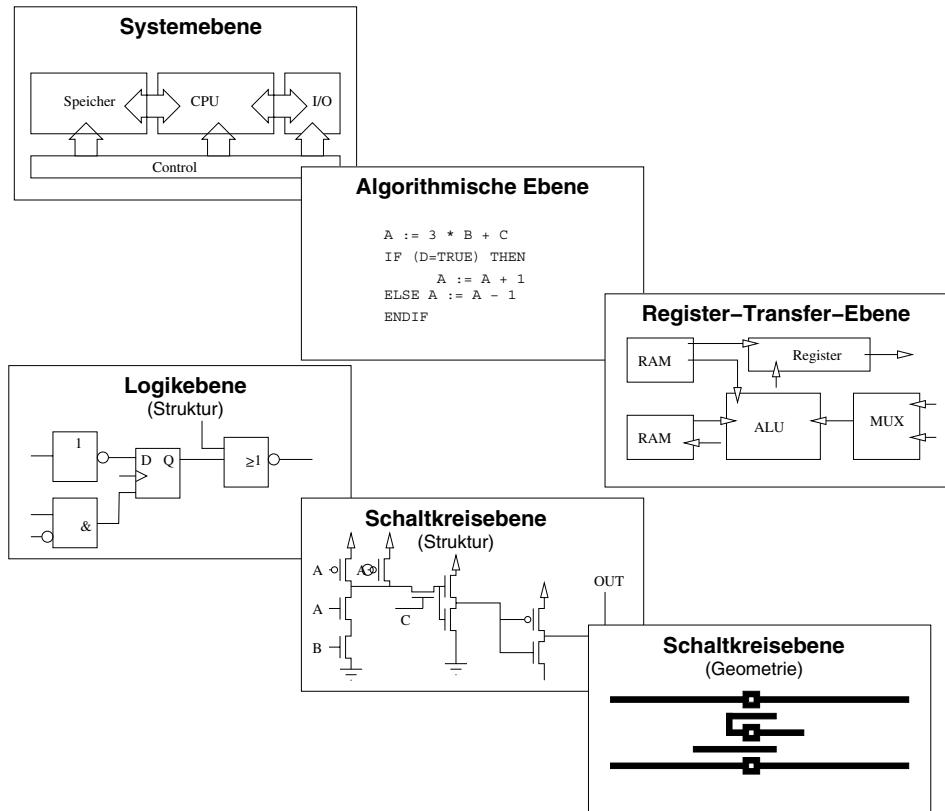

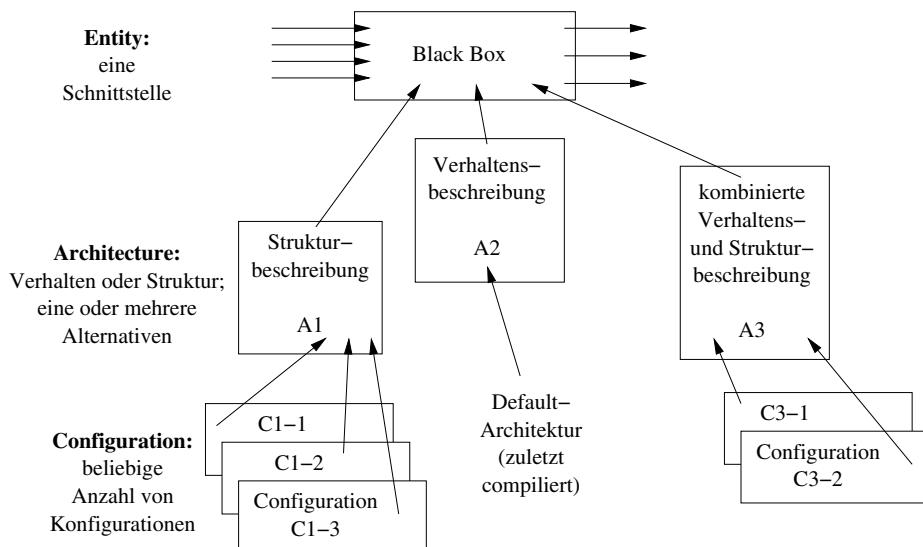

Entwickler nicht mehr so leicht, die Arbeitsweise eines Schaltwerks zu durchschauen. Dabei entstand die Idee, komplexe Schaltungsentwicklung mit Rechnerunterstützung zu betreiben. Deswegen werden wir die Entwurfssprache *VHDL* für Hardwaredesign behandeln. Die Abkürzung „*VHDL*“ bedeutet *Very High Speed Integrated Circuit Hardware Description Language*. Um mit Rechnerunterstützung elektronische Schaltungen entwickeln zu können, gehen wir von einem *Y-Diagramm* aus, das drei Entwurfssichten darstellt: Dies sind die folgenden Sichten: *Verhalten eines Systems* (von außen nach innen), die *Struktur* (CPUs, Speicher, Busse, Module, ...) sowie die *Geometrie* (die geometrische Unterteilung der Chipfläche, Cluster, Zellen, Masken, ...).

Um anschliessend die Funktion von Computersystemen verstehen zu können, machen wir zuvor aber noch einen Abstecher zu den *Endlichen Automaten*; dies sind solche, die eine endliche Anzahl von Zuständen besitzen und deren Zustandsübergänge deterministisch sind. Zur Einführung in die Arbeitsweise von Computersystemen werden wir *Mealy-* und *Moore-Schaltwerke* betrachten.

Betrachtet man Computersysteme konzeptuell, so können wir feststellen, dass sich in der Struktur der Computer in den letzten Jahrzehnten wenig geändert hat. Diese Struktur basiert immer noch auf den Ideen von *John von Neumann* und *Konrad Zuse*. Zur Laufzeit sind im Arbeitsspeicher sowohl die Daten als auch die Programme in binärer Form hinterlegt. Der Computer selbst kann nur Instruktionen ausführen. Durch den Einsatz unterschiedlicher Programme ist es damit möglich, verschiedene Probleme zu lösen.

Der nächste Teil geht auf die Thematik der Computernetzwerke ein, welche die Computerwelt in den letzten zehn Jahren revolutionär beeinflusst haben.

Wir werden den prinzipiellen Aufbau von Netzwerken betrachten und dann in die Welt der Standardisierungs-Organisationen eintauchen. Diese Organisationen haben einen nennenswerten Beitrag dazu geleistet, trotz der vielen Anbieter im Hard- und Software-Segment eine weltweit einheitliche Struktur im Netzwerkbereich zu erhalten. Als „krönenden Abschluss“ dieses Abschnitts betrachten wir praxisorientiert das „Netz der Netze“ – das Internet. Wir widmen uns dem Internet Protocol IPv4 und seinem Nachfahren IPv6 sowie den darauf aufbauenden Transportprotokollen TCP und UDP.

Im dritten Teil des vorliegenden Buches betrachten wir *Betriebssysteme und Systemsoftware*. Wir werden versuchen, einen groben Überblick über die verschiedenen Mechanismen eines Betriebssystems zu geben, ohne uns dabei auf ein spezielles Betriebssystem zu konzentrieren. Vielmehr wollen wir die allen Betriebssystemen gemeinsamen Features herausarbeiten, so dass man sich später in nahezu jedem Betriebssystem wieder zurechtfindet, weil man die grundlegenden Mechanismen wiedererkennt.

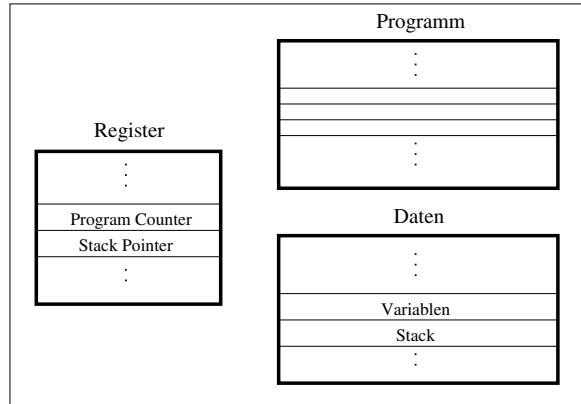

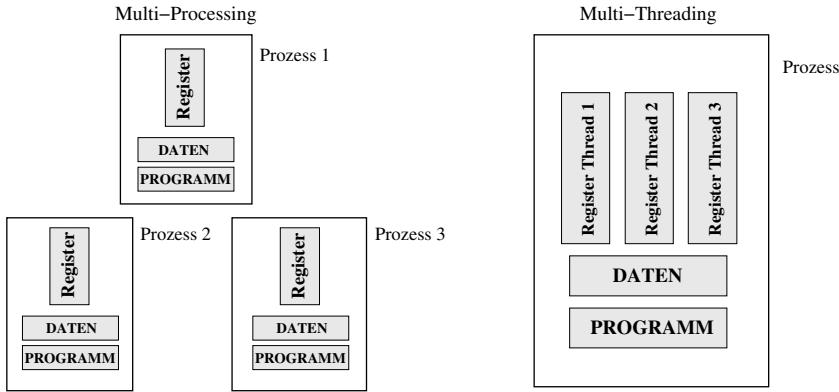

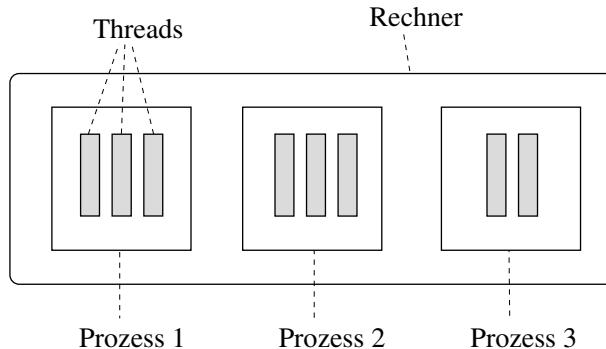

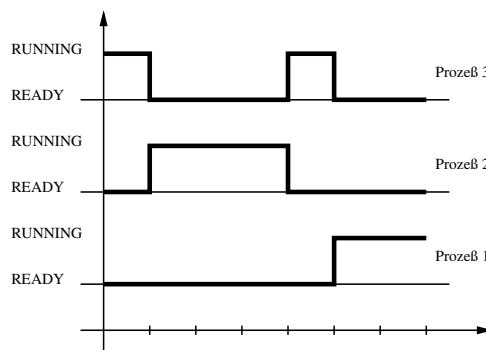

Wir werden *Prozesse* als primäre „*Klienten*“ eines Betriebssystems kennenlernen, welche die verschiedensten Betriebssystemfunktionen hauptsächlich über Betriebssystemaufrufe (engl. *System Calls*, auch *Supervisory Calls* oder *Service Calls*, abgekürzt SVCs oder SCs) nutzen können. Im Rahmen des Themas *Prozesse* werden wir auch die *Threads*, *Objekte*, Fragen der *Parallelität von Programmprozessen*, *Prozesshierarchien*, *Prozesszustände* sowie das *Scheduling* von Programmprozessen betrachten.

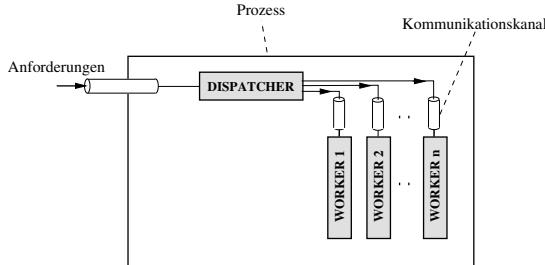

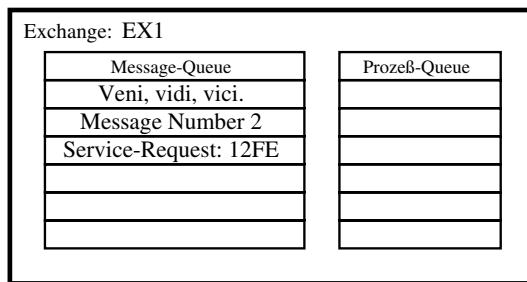

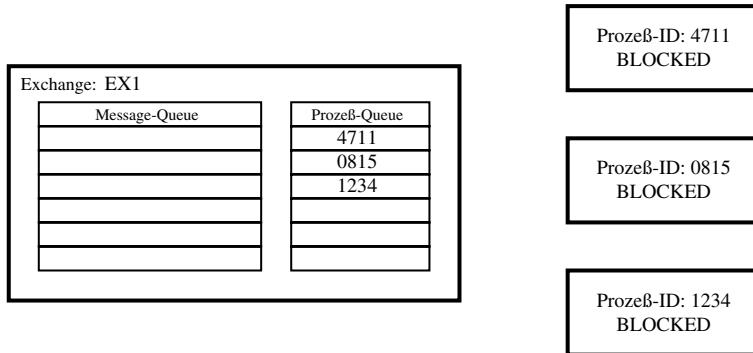

Der nächste Abschnitt ist der *Interprozess-Kommunikation* gewidmet, also dem Austausch von Nachrichten zwischen einem Sender- und einem oder mehreren Empfängerprozessen. Hier werden wir zwischen Mechanismen der Kommunikation und Synchronisation von Prozessen unterscheiden und in diesem Rahmen *synchrone* und *asynchrone Methoden* betrachten.

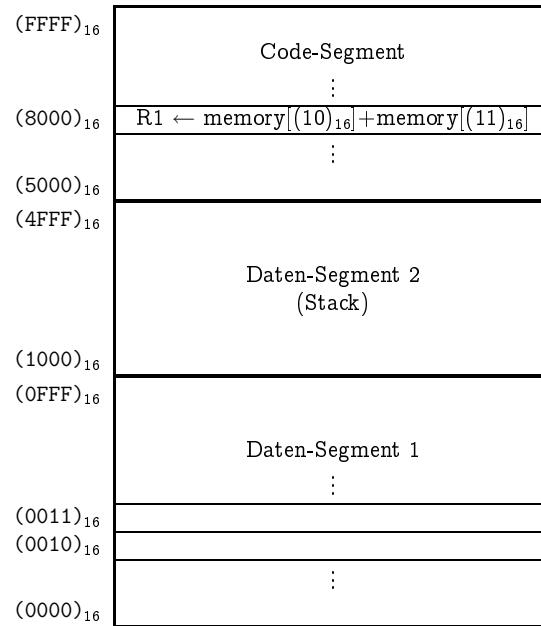

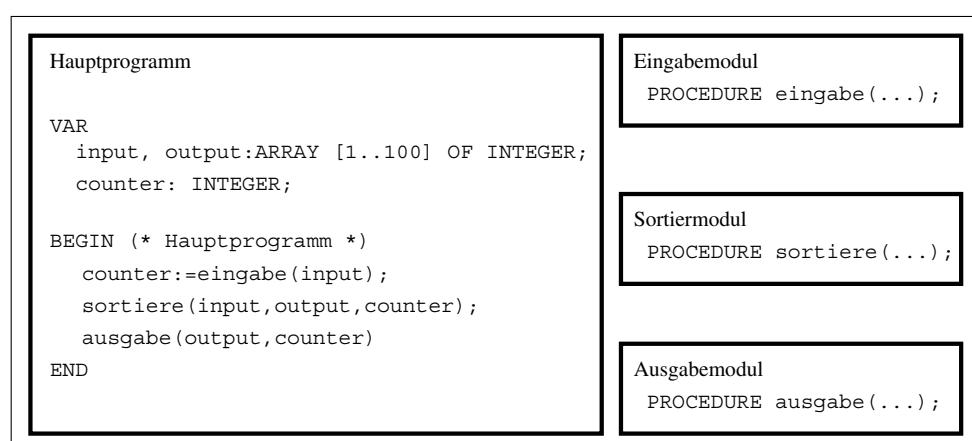

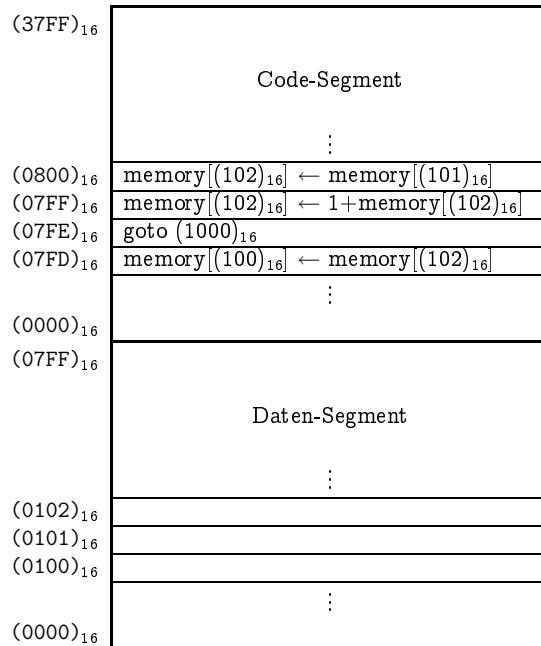

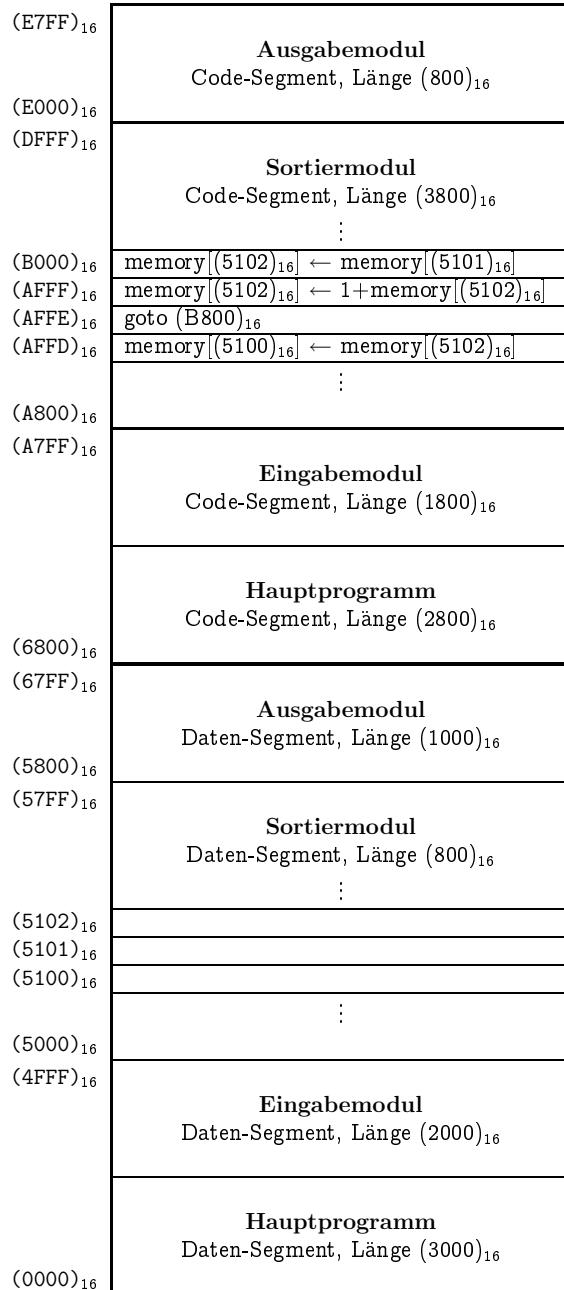

Ein nächster Schwerpunkt bei der Behandlung von Betriebssystemen ist die *Speicherverwaltung*; d.h., wie soll für einen Programmprozess der notwendige Speicherplatz reserviert werden, und zwar nicht nur für die ausführbaren Instruktionen (den *Code*), sondern auch für die verwendeten Daten (*Variablen*) sowie die erforderliche Datenstruktur (*Prozessdeskriptor*) zur Verwaltung des Programmprozesses durch das Betriebssystem. Dazu gehören Verfahren der physikalischen Adresszuordnung wie das *Swapping*, *Paging* und die *Segmentierung*.

Der Bereich der Betriebssysteme wird abgerundet durch Abschnitte über Geräte-Treiber-Software (*Device Driver*) und das *Ressourcen-Management*. Außerdem wollen wir noch eine Einführung in einen Bereich geben, der vor allem in den letzten Jahren sehr an Bedeutung gewonnen hat, nämlich der *Sicherheit* von Computersystemen. Nachdem dieses Gebiet sehr weit gefächert ist, beschränken wir uns allerdings auf eine Beschreibung der grundlegenden Konzepte und jener Sicherheitsmechanismen, die Betriebssysteme üblicherweise zur Verfügung stellen.

Abschließend möchten die Verfasser der Hoffnung Ausdruck verleihen, dass es dem Leser nicht allzu schwer fällt, unser Buch zu verstehen und dieses später auch einmal als geeignetes Nachschlagewerk zu nutzen.

# Hardware

In der Struktur der Computer hat sich in den letzten Jahrzehnten relativ wenig geändert. Sie basiert immer noch auf den Konzepten des ungarischen Mathematikers *John von Neumann* und des deutschen Bauingenieurs *Konrad Zuse*. Zur Laufzeit befinden sich im Arbeitsspeicher des Rechners sowohl die Daten als auch die Programme. Der Computer kann selbst nur Befehle ausführen. Durch den Einsatz unterschiedlicher Programme ist es daher möglich, verschiedene Aufgabenstellungen zu bearbeiten.

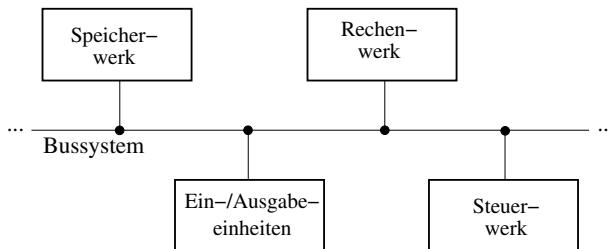

Ein Computer setzt sich aus folgenden Komponenten zusammen:

**Rechenwerk:** Hier erfolgt die eigentliche Verarbeitung der Daten sowie auch ihr Transfer.

**Speicherwerk:** Diese Komponente dient der Speicherung der Daten und Programme.

**Steuerwerk:** Die Aufgabe des Steuerwerks besteht in der Koordination der einzelnen Komponenten.

**Ein-/Ausgabeeinheiten:** Über diese Komponenten lassen sich Informationen mit den Peripheriegeräten (Ein-/Ausbabegeräte und Hintergrundspeicher) austauschen.

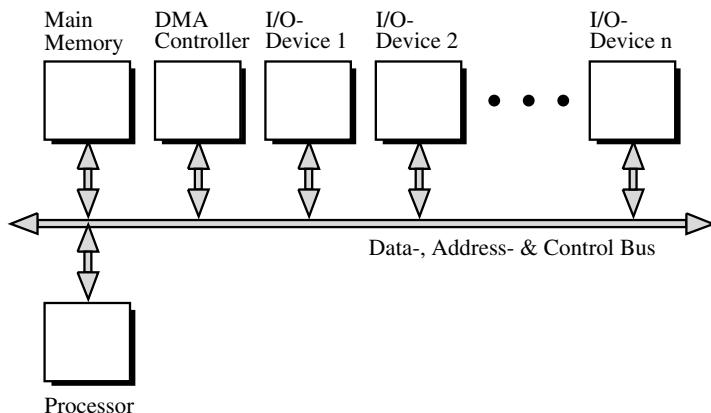

**Bussystem:** Über das Bussystem können Daten zwischen den oben erwähnten Teilen ausgetauscht werden.

Abbildung 1.1: Computerkomponenten

Alle diese Teile sind mit *logischen* Schaltungen aufgebaut. Daher wollen wir im ersten Schritt diese Bauteile behandeln. Im nächsten Abschnitt *Mikroprozessoren* wird aus diesen Bestandteilen die Hardwarestruktur einer *Central Processing Unit (CPU)*, die das zentrale Rechen- und Steuerwerk darstellt, aufgebaut und ihre Funktionsweise erklärt. Die verschiedenen Operationen, welche die Prozessoren ausführen können, ihre Qualitätsmerkmale sowie die restlichen Bestandteile eines Computers werden im Teil *Systemsoftware* näher betrachtet. Am Ende dieses Abschnittes werden wir einen vollständigen Computer entwickelt haben, der *Maschinen-Code* - das sind binär-codierte Befehle - verarbeiten kann. Diese Maschinenbefehle werden von der CPU gelesen und abgearbeitet.

Die Programmierung eines Computersystems in Maschinenbefehlen ist recht umständlich und von einem Menschen allein kaum zu bewältigen. Deshalb wird eine neue Sprache eingeführt, die sich auf die Maschinen-Codes abbilden lässt. Zur Konvertierung der Sprachen setzt man wiederum einen Computer ein. Dazu bestehen zwei Lösungswege:

**Übersetzung:** Vor der Ausführung des Programms wird zu einem beliebigen Zeitpunkt jeder Befehl des in der neuen Sprache geschriebenen *Source-Codes* von einem *Compiler*-Programm

in eine äquivalente Folge von Maschinen-Instruktionen übersetzt. Das Ergebnis ist ein Programm in Maschinensprache, das auf einem Computer exekutiert werden kann. Der Source-Code ist anschließend nicht mehr erforderlich. Es ergibt sich damit eine Trennung von Übersetzungs- und Ausführungsphase.

**Interpretation:** Der Interpreter liest zur Laufzeit ein erstelltes Programm in der neuen Sprache Zeile für Zeile ein und exekutiert *online* die entsprechende Folge von Maschinenbefehlen. Es wird damit eine direkte Ausführung der neuen Sprache simuliert.

# 2 Logische Schaltungen

*Wer sie nicht kennte,

die Elemente,

ihre Kraft

und Eigenschaft,

wäre kein Meister

über die Geister.*

Faust.

Johann Wolfgang von Goethe,

„Faust“. Der Tragödie erster Teil.

## 2.1 Grundbegriffe

In dem Buch G.H. Schildt et al. „Informatik Grundlagen“, Springer Verlag (2002) wurden die theoretischen Grundlagen der Informatik dargestellt. In dem vorliegenden Buch „Einführung in die Technische Informatik“ soll nun eine Brücke geschlagen werden, um die erworbenen Kenntnisse auf den Entwurf digitaler Schaltungen anwenden zu können.

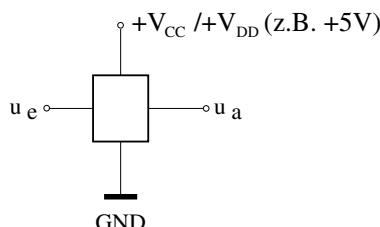

Zum Betreiben einer elektronischen Schaltung wird eine Versorgungsspannung erforderlich, die üblicherweise +5 V oder +12 V beträgt. Diese Versorgungsspannung wird mit VDD oder VCC bezeichnet. Der 0 V-Anschluss wird Ground (Masse) genannt und meistens mit GND bezeichnet. Die Spannungen, die am Eingang mit  $u_e$  und am Ausgang mit  $u_a$  bezeichnet werden, liegen stets zwischen 0 V und der Versorgungsspannung.

Abbildung 2.1: Versorgungsspannungsanschlüsse an einem elektronischen Bauelement mit  $+V_{CC}$  /  $+V_{DD}$  und Ground (GND, Masse)

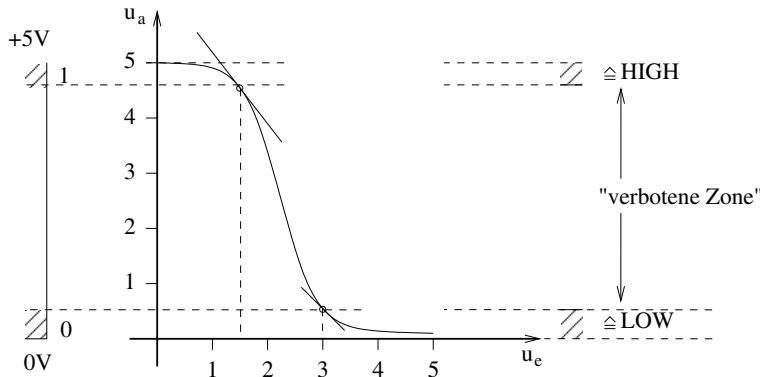

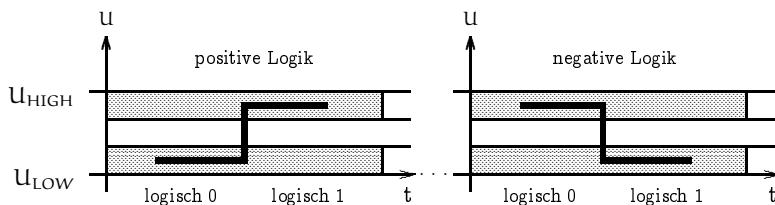

Es muss definiert werden, wie die Zustände logisch 0 und logisch 1 darzustellen sind. Bei digitalen Schaltungen werden die Zustände durch zwei Spannungswerte repräsentiert, wobei der Spannungswert  $U_{LOW}$  der logische Zustand 0 und der hohen Spannungswert  $U_{HIGH}$  der logische Zustand 1 zugeordnet wird (positive Logik). Bei realen Schaltkreisen werden Toleranzbreiten um diese Spannungswerte zugelassen. Die kleinere Spannung  $U_{LOW}$  muss daher nicht notwendigerweise null sein. Ordnet man die Spannungswerte umgekehrt zu,  $U_{LOW}$  dem Zustand logisch 1 und  $U_{HIGH}$  dem Zustand logisch 0, dann bezeichnet man diese Zuordnung als negative Logik, wie die folgende Abbildung zeigt.

Abbildung 2.2: Übertragungskennlinie  $u_a = f(u_e)$  eines Inverters

Die Spannungsintervalle für 0 und 1 werden so gewählt, dass man für 0 und 1 in den flachen Teilen der Übertragungskennlinie des Inverters nach Abbildung 2.2 bleibt. Dies sind die Bereiche, in denen die Kennliniensteigung dem Betrage nach kleiner als 1 ist. Damit soll gewährleistet werden, dass die Logiksignale stets eindeutig 0 und 1 sind.

Dazwischen befindet sich ein Bereich, der „verbotene Zone“ genannt wird; Spannungswerte in diesem Bereich sind nicht zulässig, somit darf es auch keine Spannungswerte geben, die zwischen 0 und 1 liegen.

Abbildung 2.3: Wechsel von logisch 0 auf 1 bei positiver und negativer Logik

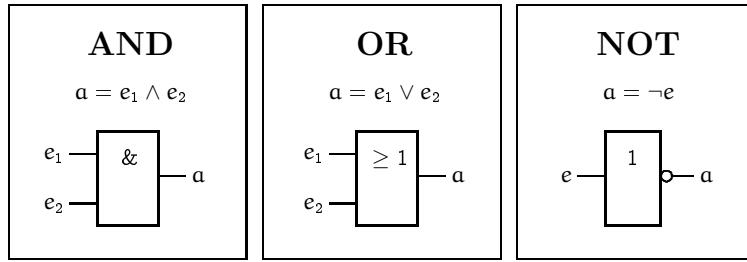

Bei dem Aufbau von elektronischen Schaltungen werden Bauteile verwendet, welche die mathematischen Operatoren  $\wedge$  (UND),  $\vee$  (ODER) und  $\neg$  (NOT) realisieren. Die Methode zur mathematischen Herleitung eines Schaltungsaufbaues wird *Schaltalgebra* genannt. In den Schaltplänen werden anstatt der logischen Operatoren und Operanden Schaltsymbole verwendet. Diese wurden von der *International Electrotechnical Comission (IEC)* genormt und von vielen nationalen Normungsinstituten übernommen und werden auch in diesem Buch verwendet.

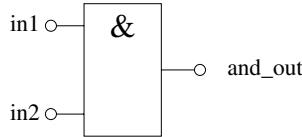

Elektronische Bausteine, welche die logischen Funktionen umsetzen, werden *Gatterschaltungen* oder auch in der Kurzform Gatter (engl. *gate*) genannt. Gatter zur Realisierung der logischen Funktionen UND, ODER und NICHT werden Grundgatter genannt und sind in der folgenden Abbildung dargestellt.

Abbildung 2.4: Grundgatter

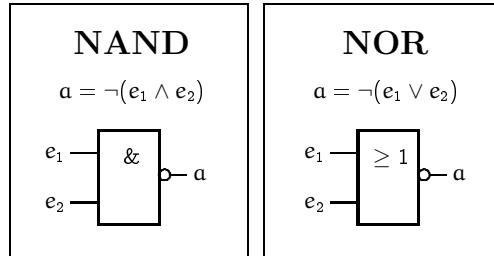

Zwei weitere Gatter, die in der Praxis häufig Verwendung finden, sind das NAND (Not AND)- und das NOR ( Not OR )-Gatter.

Abbildung 2.5: NAND- und NOR- Gatter

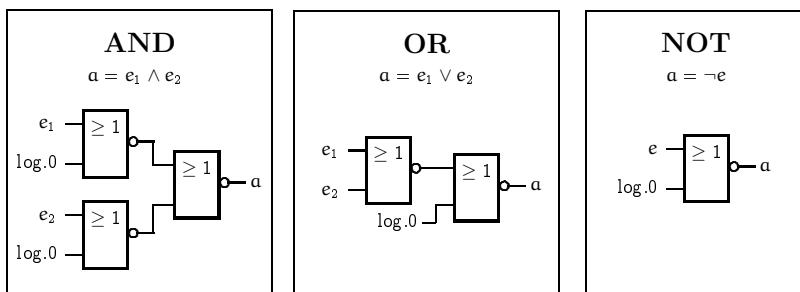

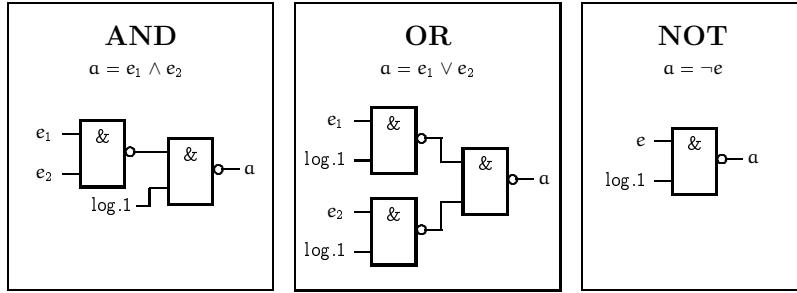

Man nennt diese Gatter auch *universelle Gatter*, da es mit jedem dieser zwei Gatter möglich ist, die drei booleschen Grundfunktionen nachzubilden. Diese Umsetzung zeigen die beiden folgenden Abbildungen.

Abbildung 2.6: Boolesche Operatoren aus NOR-Gattern aufgebaut

Abbildung 2.7: Boolesche Operatoren aus NAND-Gattern aufgebaut

Mit Hilfe der Booleschen Algebra und den *de Morganschen Gesetzen* kann man die Korrektheit der dargestellten Gatterschaltungen nachvollziehen.

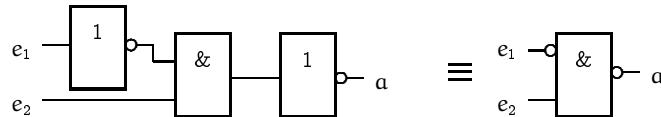

Man kann die Darstellung von Gatterschaltungen noch dahingehend vereinfachen, dass man vor einen Eingang geschaltete NOT-Gatter durch einen eingangsseitigen Negationskreis darstellt bzw. ein an einen Ausgang geschaltetes NOT-Gatter durch einen Negationskreis ausgangsseitig in der Schaltung darstellt.

Abbildung 2.8: Vereinfachte Darstellung von  $a = \neg(\neg e_1 \wedge e_2)$

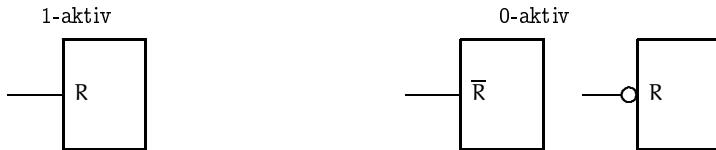

Bei manchen Eingängen unterscheidet man zwischen 0-aktiven und 1-aktiven Eingängen, wie zum Beispiel bei Setz- und Rücksetzeingängen. Von einem 1-aktiven Eingang spricht man, wenn dieser beim Anlegen einer 1 aktiv wird, der Ruhezustand liegt dann bei logisch 0; umgekehrt wird der Eingang mit logisch 0 aktiv (Ruhezustand logisch 1). Im Schaltsymbol zeichnet man bei einem 0-aktiven Eingang einen Negationskreis oder negiert den betreffenden Buchstaben. Es ist zu beachten, dass der Negationskreis den 0-aktiven Eingang kennzeichnet. Die folgende Abbildung zeigt einige Beispiele:

Abbildung 2.9: 1-aktive und 0-aktive Eingänge

Es gibt verschiedene Schaltungstechniken für die Realisierung der einzelnen Gatter; man nennt diese *Schaltkreisfamilien*. Die Schaltkreisfamilien werden nach folgenden Kriterien klassifiziert:

**Power dissipation:** Darunter versteht man die Verlustleistung eines Gatters, die in W, mW oder W angegeben wird.

**Propagation delay:** Das ist die Zeit, die vergeht, bis nach dem Anlegen der Eingangssignale das Ausgangssignal am Ausgang eines Bausteins im „eingeschwungenen Zustand“ anliegt.

**Fan out:** Dieser Wert gibt an, wie viele Eingänge man an einen Ausgang anschließen kann, ohne die Funktionalität zu beeinträchtigen. Dies gilt nur, wenn Bausteine der gleichen Schaltkreisfamilie verwendet werden (auch *Ausgangsfächer* genannt)

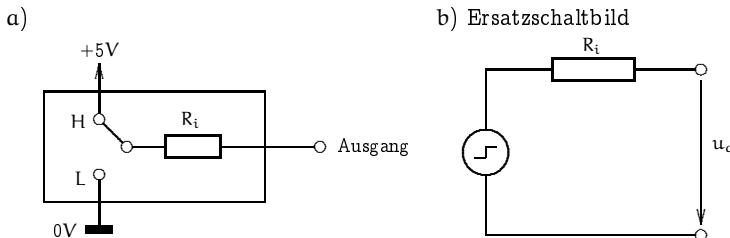

### 2.1.1 Fan Out

Für den Ausgang eines Digitalbausteins verwenden wir folgendes einfache Modell (siehe folgende Abbildung): Abhängig vom Logikzustand wird der Ausgang über einen Schalter mit 0 V oder +5 V verbunden (Schalterstellungen L für LOW und H für HIGH). In Wirklichkeit handelt es sich nicht um einen mechanischen, sondern um einen elektronischen Transistorschalter. Der Restwiderstand, den die durchgeschalteten Transistoren noch haben, wird durch den Innenwiderstand  $R_i$  dargestellt. Der Ausgang stellt daher eine Spannungsquelle mit der Leerlaufspannung 0 V oder +5 V (je nach Logikzustand) und dem Innenwiderstand  $R_i$  dar. Dieses Modell ist jedoch eine grobe Näherung, die für unsere Zwecke aber ausreicht.

Abbildung 2.10: Modell eines Digitalbausteins und das zugehörige Ersatzschaltbild (ESB)

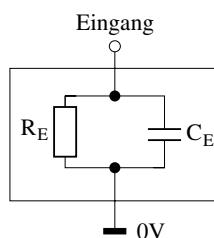

Für den Eingang eines Digitalbaustein sehen wir als Modell einen Widerstand und eine Kapazität vor. Diese Kapazität ist in realen Schaltungen unvermeidlich (parasitär): Schon durch die geometrischen Abmessungen der Halbleiterschaltung stellt jeder Eingang eine kapazitive Belastung dar. Durch den Widerstand fließt beim Anlegen einer Spannung ein Strom in den Eingang hinein. Dieses Modell ist ebenso sehr vereinfacht: Halbleiterschaltungen haben meistens eine nichtlineare Charakteristik, die sich durch einen ohmschen Widerstand nicht wiedergegeben werden kann. Für unsere Betrachtungen wollen wir es aber bei diesem einfachen Modell, bestehend aus der Parallelschaltung von Eingangswiderstand  $R_E$  und der wirksamen Kapazität  $C_E$  am Eingang, belassen.

Abbildung 2.11: Ersatzschaltbild Eingang

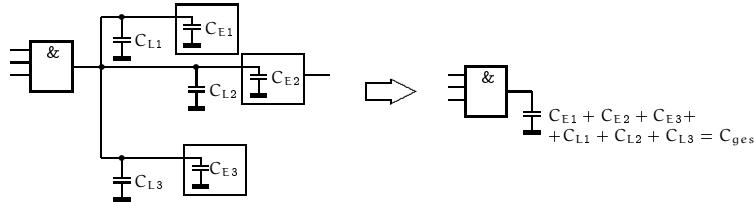

Werden mehrere Eingänge an einen Ausgang angeschlossen, wird dieser Ausgang durch die Eingänge belastet, wobei hierbei die kapazitive Belastung von besonderer Bedeutung ist. Werden mehrere Kapazitäten parallel geschaltet, so addieren sich diese zu einer Gesamtkapazität.

Die parallelen Kapazitäten der einzelnen Eingänge  $C_{E1}$  bis  $C_{E3}$  addieren sich somit zu einer Gesamtkapazität. Hinzu kommt noch die kapazitive Belastung durch die Zuleitungen. Längere Leitungen stellen ebenso nennenswerte Kapazitäten  $C_{L1}$  bis  $C_{L3}$  dar. Der Ausgang wird daher mit der Summe dieser Kapazitäten belastet, wie die folgende Abbildung zeigt:

Abbildung 2.12: Kapazitive Belastung

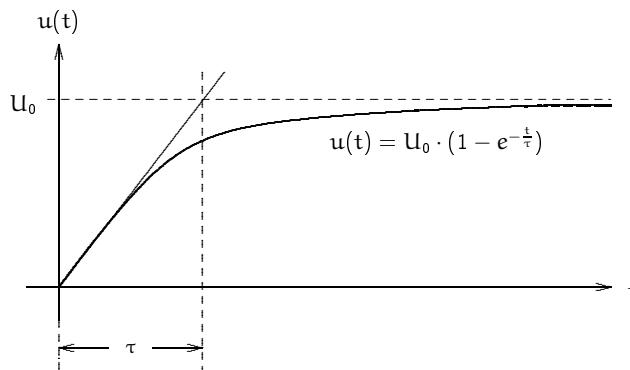

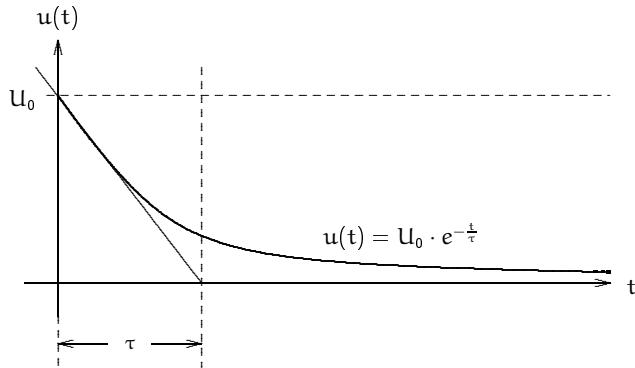

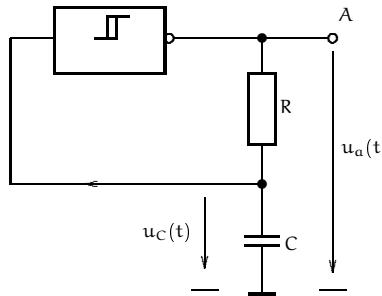

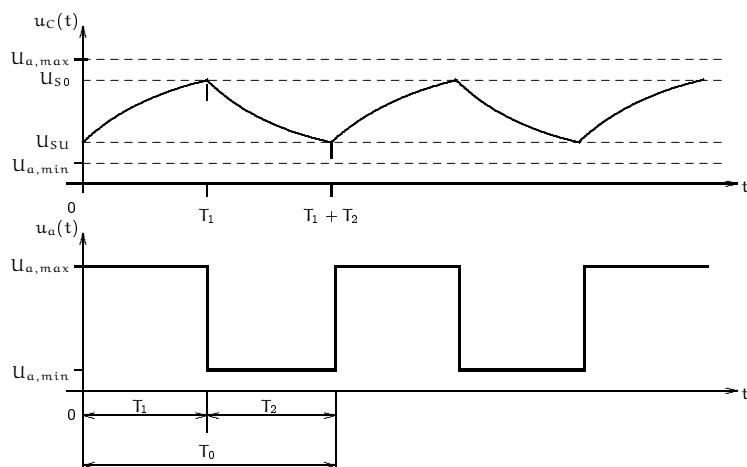

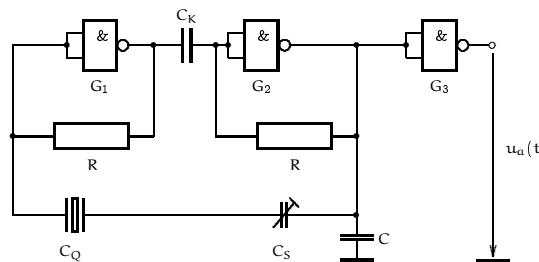

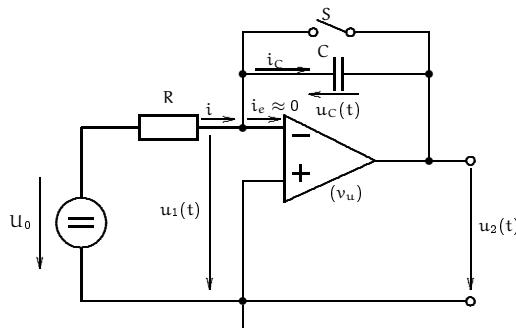

Die gesamt wirksame Kapazität muss bei jedem Umschaltvorgang über den Innenwiderstand des Ausganges auf- bzw. entladen werden. Die Spannungsverläufe für die Spannung an der gesamt wirksamen Kapazität  $u_C(t)$  bei einem solchen Auflade- und Entladenvorgang verlaufen exponentiell und können wie folgt beschrieben werden:

$$\text{Aufladevorgang: } u_C(t) = U_0 \cdot \left(1 - e^{-\frac{t}{\tau}}\right)$$

$U_0 \dots \text{asymptotischer Endwert}$

$$\text{Entladenvorgang: } u_C(t) = U_0 \cdot e^{-\frac{t}{\tau}}$$

$U_0 \dots \text{Anfangswert}$

mit der Zeitkonstante  $\tau = R \cdot C_{\text{ges}}$ . Man kann leicht nachrechnen, dass nach  $(4 \dots 5)\tau$  der Endwert praktisch erreicht wird (nach  $4 \cdot \tau$  etwa 98% bzw. nach  $5 \cdot \tau$  circa 99% des Endwertes).

Abbildung 2.13: Spannungsverläufe bei kapazitiver Belastung (Aufladevorgang)

Wenn wir zum Beispiel als Zahlenwerte einen Innenwiderstand  $R_i$  von  $200 \Omega$  und eine Gesamtlastkapazität von  $25 \text{ pF}$  annehmen, ergibt sich eine Zeitkonstante  $\tau = R \cdot C$  von  $5 \text{ ns}$  (Nanosekunden).

Abbildung 2.14: Spannungsverläufe bei kapazitiver Belastung (Entladevorgang)

Je grösser die Lastkapazität ist, umso länger dauert das Umladen der gesamt wirksamen Kapazität, und die Signalfanken werden immer flacher. Diese Auf- und Entladevorgänge beeinflussen entscheidend die obere Grenzfrequenz, mit der integrierte Schaltkreise betrieben werden können. Deshalb darf die kapazitive Last nicht beliebig gross sein und die Anzahl der Eingänge, die an einen Ausgang angeschlossen werden darf, wird dadurch beschränkt. Man nennt die maximal mögliche Anzahl der anschließbaren Eingänge an einen Ausgang den *Fan out* (Ausgangsfächer). Ist der Fan-Out z.B. 10, so dürfen an einen Ausgang maximal zehn Eingänge angeschlossen werden. Wird diese Belastungsgrenze überschritten, sind Funktionsstörungen möglich. Wenn man den Fan-Out durch eine Zahl angibt, so setzt man dabei natürlich voraus, dass alle Eingänge und Ausgänge der gleichen Schaltkreisfamilie angehören. Innerhalb einer Schaltkreisfamilie ist das normalerweise der Fall. Besondere Eingänge wie zum Beispiel Takt- und Rücksetzeingänge, die im Inneren des Bausteins an mehrere Gatter führen, stellen eine grössere Last als ein Standardeingang dar.

## 2.1.2 Schaltkreisfamilien

Zu den wichtigsten Familien gehören:

**TTL (Transistor-Transistor Logic):** Diese Gruppe hat einen großen *Fan out*, wird allerdings wegen der relativen grossen Gatterlaufzeit (Propagation delay) heute kaum noch verwendet. Ihre Weiterentwicklung, (z.B. durch den Einsatz von Schottky-Dioden) arbeitet schneller und befindet sich deshalb auch heute noch im Einsatz.

**ECL (Emitter Coupled Logic):** Den Vorteilen – geringste Gatterlaufzeiten (propagation delay) bei hoher Störsicherheit – stehen nachteilig große Verlustleistungen der Gatterschaltungen und hohe Kosten gegenüber.

**MOS (Metal-Oxid Semiconductor):** Bei einfachen Gattern wird diese Technik selten eingesetzt; sie wird jedoch bei hoch integrierten Schaltungen angewandt.

**CMOS (Complementary MOS):** Diese Familie ist durch die geringste Leistungsaufnahme und einen großen Betriebsspannungsbereich gekennzeichnet und wird deshalb vor allem

bei batteriebetriebenen Geräten eingesetzt. Diese Technik ist Standard im PC-Bereich. Sie besitzt einen hohen statischen Störabstand, der etwa 55% der Versorgungsspannung beträgt.

In den Standard-Bauteilfamilien TTL und CMOS haben die Bauteile nur eine kleine Integrationsdichte.

Auf weitere Betrachtungen im Rahmen dieses Buches wollen wir hier verzichten, da uns vor allem die Funktionalität der integrierten Schaltungen interessieren soll.

### 2.1.3 Signalnamen und Signalverbindungen

Oft ist es nötig, Signalen einen Namen zu geben. Außerdem kann man sich durch die Benennung von Signalen verwirrende Verbindungen ersparen. Gleichnamige Signale sind auch logisch gleich.

Abbildung 2.15: Signalnamen

Die Versorgungsspannung zeichnet man jedoch nur ein, wenn das aus besonderen Gründen notwendig ist. Für gewöhnlich werden nur die logischen Verbindungen gezeichnet.

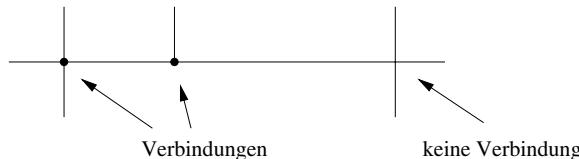

Die *Verbindung von zwei Signalleitungen* zeigt man durch einen Verzweigungspunkt an. Ist dieser nicht vorhanden, besteht keine Verbindung:

Abbildung 2.16: Verbindung von Signalleitungen

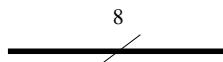

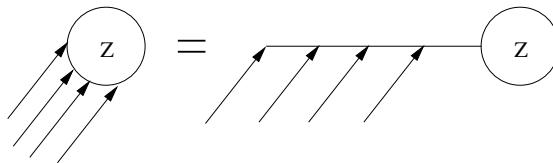

Oft treten Busleitungen als Leitungsvielfach (z.B. Flachbandkabel). Zur Vereinfachung fasst man solche Leitungen in einem Strich zusammen (der unter Umständen dicker gezeichnet wird als die Einzelleitungen) und schreibt die Anzahl der zusammengefassten Leitungen an:

Abbildung 2.17: Signalbündel

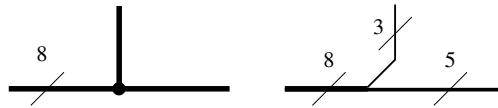

Solche Leitungsbündel kann man wie andere Leitungen verzweigen oder in zwei oder mehr Bündel aufteilen:

Abbildung 2.18: Verzweigungen und Aufteilungen von Signalbündeln

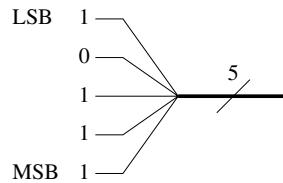

Möchte man an ein solches Bündel ein Bitmuster anlegen, so kann man es „auffasern“. Es ist dabei oft notwendig, durch die Bezeichnung *Least Significant Bit* und *Most Significant Bit* (*LSB* und *MSB*) die Ordnung der Leitungen anzugeben.

Abbildung 2.19: Signalbündel mit LSB und MSB

## 2.2 Realisierung von Funktionen

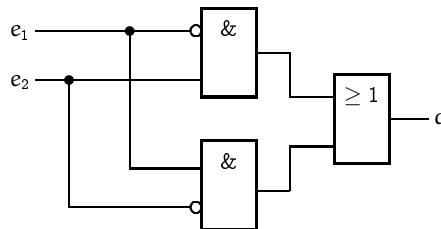

Im nächsten Schritt wollen wir zeigen, wie logische Funktionen in Gatterschaltungen umzusetzen sind. Als Beispiel wird die Antivalenzfunktion

$$\text{XOR} = e_1 \oplus e_2$$

aus den Grundgattern AND, OR und NOT entsprechend der Funktion

$$(\neg e_1 \wedge e_2) \vee (e_1 \wedge \neg e_2) = e_1 \oplus e_2 = a$$

aufgebaut.

Abbildung 2.20: Antivalenz

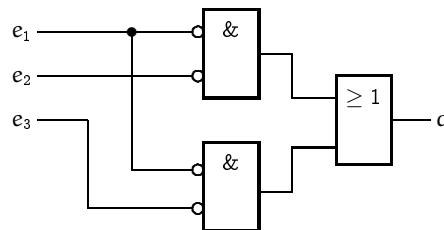

Als nächstes soll eine Schaltung realisiert werden, die drei Eingänge  $e_1$ ,  $e_2$  und  $e_3$  besitzt, die als Bits einer binären Zahl interpretiert werden. Sie gibt am Ausgang dann logisch 1 aus, wenn

die binäre Zahl an den Eingängen kleiner als 3 ist, wobei der Eingang  $e_1$  das höchstwertige Bit (engl. *msb = Most Significant Bit*) und der Eingang  $e_3$  das niederwertigste Bit (engl. *lsb = Least Significant Bit*) repräsentieren. Zuerst stellen wir die Wahrheitstabelle auf.

| dez | binär | $e_1$ | $e_2$ | $e_3$ | a |

|-----|-------|-------|-------|-------|---|

| 0   | 000   | 0     | 0     | 0     | 1 |

| 1   | 001   | 0     | 0     | 1     | 1 |

| 2   | 010   | 0     | 1     | 0     | 1 |

| 3   | 011   | 0     | 1     | 1     | 0 |

| 4   | 100   | 1     | 0     | 0     | 0 |

| 5   | 101   | 1     | 0     | 1     | 0 |

| 6   | 110   | 1     | 1     | 0     | 0 |

| 7   | 111   | 1     | 1     | 1     | 0 |

Aus der Wahrheitstabelle erhält man die disjunktive Normalform:

$$a = f(e_1, e_2, e_3) = (\neg e_1 \wedge \neg e_2 \wedge \neg e_3) \vee (\neg e_1 \wedge \neg e_2 \wedge e_3) \vee (\neg e_1 \wedge e_2 \wedge \neg e_3)$$

Durch die Verwendung des KV-Diagramms oder des Algorithmus nach Quine und McCluskey erhalten wir die reduzierte Form

$$a = f(e_1, e_2, e_3) = (\neg e_1 \wedge \neg e_2) \vee (\neg e_1 \wedge \neg e_3)$$

Die Abbildung 2.21 zeigt die Realisierung dieser Funktion mit Hilfe von Gattern.

Abbildung 2.21: Realisierung mit Hilfe von Gattern

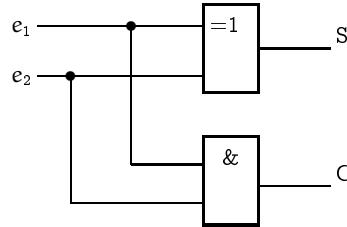

## 2.2.1 Halbaddierer

Addierer sind logische Schaltungen, die zwei Binärzahlen miteinander addieren. Die einfachste Form – der *Halbaddierer* – zählt zwei einstellige Binärzahlen zusammen (der Name „Halbaddierer“ kommt daher, dass mögliche Überträge aus Vorstellen im Gegensatz zum Volladdierer nicht berücksichtigt werden). Wir beginnen mit der Untersuchung aller möglichen Fälle und stellen dabei folgende Wahrheitstabelle auf:

| $e_1$ | $e_2$ | $e_1 + e_2$ |

|-------|-------|-------------|

| 0     | 0     | 00          |

| 0     | 1     | 01          |

| 1     | 0     | 01          |

| 1     | 1     | 10          |

Im Fall, dass  $e_1$  und  $e_2$  gleich eins sind, entsteht ein Übertrag in die nächsthöhere Stelle. Die Schaltung benötigt daher zwei Ausgänge. Deswegen muss man eine Funktion für die *Summe*  $S$  (engl. *sum*) und eine für den *Übertrag*  $C$  (engl. *Carry*) herleiten. Durch das Aufstellen der disjunktiven Normalform erhalten wir die booleschen Funktionen  $S = e_1 \oplus e_2$  und  $C = e_1 \wedge e_2$ . Der Übertrag stellt daher eine UND-Verknüpfung und die Summe eine *Antivalenz*-Verknüpfung dar (sie wird durch das Symbol  $=1$  in den Abbildungen dargestellt). Die Schaltung ist in der folgenden Abbildung dargestellt.

Abbildung 2.22: Halbaddierer

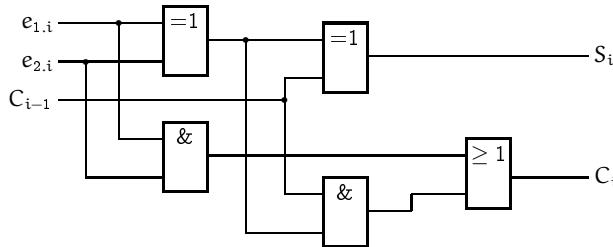

### 2.2.2 Volladdierer

Möchte man zwei Binärzahlen mit  $n$  Stellen addieren – wobei die Stellen der ersten Zahl mit  $(e_{1,i})$  und die der zweiten mit  $(e_{2,i})$  für  $i = 1, 2, \dots, n$  bezeichnet werden – kann man den Halbaddierer nur für das niederwertigste Bit ( $i = 1$ ) (lsb) verwenden. Bei allen anderen Stellen muss man nicht nur die Bits der Zahlen, sondern auch den Übertrag der nächstniedrigeren Stelle dazu addieren. Der Übertrag für die  $i$ -te Stelle wird allgemein als  $C_{i-1}$  ( $i = 2, 3, \dots, n$ ) angeschrieben.

Mit Hilfe der folgenden Wahrheitstabelle können wir die Funktionen für die Summe  $S_i$  und den Übertrag  $C_i$  der  $i$ -ten Stufe berechnen.

| $e_{1,i}$ | $e_{2,i}$ | $C_{i-1}$ | $C_i$ | $S_i$ |

|-----------|-----------|-----------|-------|-------|

| 0         | 0         | 0         | 0     | 0     |

| 0         | 0         | 1         | 0     | 1     |

| 0         | 1         | 0         | 0     | 1     |

| 0         | 1         | 1         | 1     | 0     |

| 1         | 0         | 0         | 0     | 1     |

| 1         | 0         | 1         | 1     | 0     |

| 1         | 1         | 0         | 1     | 0     |

| 1         | 1         | 1         | 1     | 1     |

Die disjunktiven Normalformen dieser Funktionen sind damit

$$\begin{aligned} S_i = & (\neg e_{1,i} \wedge \neg e_{2,i} \wedge C_{i-1}) \vee (\neg e_{1,i} \wedge e_{2,i} \wedge \neg C_{i-1}) \vee \\ & \vee (e_{1,i} \wedge \neg e_{2,i} \wedge \neg C_{i-1}) \vee (e_{1,i} \wedge e_{2,i} \wedge C_{i-1}) \end{aligned}$$

und

$$\begin{aligned} C_i = & (\neg e_{1,i} \wedge e_{2,i} \wedge C_{i-1}) \vee (e_{1,i} \wedge \neg e_{2,i} \wedge C_{i-1}) \vee \\ & \vee (e_{1,i} \wedge e_{2,i} \wedge \neg C_{i-1}) \vee (e_{1,i} \wedge e_{2,i} \wedge C_{i-1}). \end{aligned}$$

Wir könnten auf diese Ausdrücke den Algorithmus von Quine und McCluskey anwenden, um sie zu vereinfachen. Hier können wir die vereinfachte Form allerdings direkt aus der Wahrheitstabelle ablesen. Für  $S_i$  lässt sich die reduzierte Form daraus ableiten, dass  $S_i$  immer dann den Wert 1 annimmt, wenn die Anzahl der Eingänge, die logisch 1 sind, ungerade ist. Dies wird durch die Funktion

$$S_i = e_{1,i} \oplus e_{2,i} \oplus C_{i-1}$$

realisiert. Der Übertrag ist nicht so einfach ermittelbar. Eine für unsere Schaltung optimierte Funktion ist

$$C_i = (e_{1,i} \wedge e_{2,i}) \vee (C_{i-1} \wedge (e_{1,i} \oplus e_{2,i})).$$

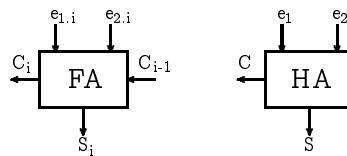

Die Realisierung der Schaltung, genannt *Volladdierer* (engl. *Full Adder*, *FA*), ist aus Abbildung 2.23 ersichtlich.

Abbildung 2.23: Volladdierer

Aus Abbildung 2.23 ist erkennbar, dass eine Funktion, die eigentlich aus drei Variablen besteht, kann auch mit Hilfe von Gattern, die nur zwei Eingänge besitzen, nachgebildet werden. Dies ist unter Anwendung des Assoziativgesetzes in Abbildung ?? durchgeführt. Auf diese Weise realisiert man an Stelle von  $e_{1,i} \oplus e_{2,i} \oplus C_{i-1}$  entweder  $e_{1,i} \wedge e_{2,i} \oplus C_{i-1}$  (wie oben) oder  $e_{1,i} \oplus e_{2,i} \oplus C_{i-1}$ . Zur Vereinfachung setzen wir voraus, dass im folgenden die Gatter die benötigte Anzahl von Eingängen besitzen.

Zur Erhöhung der Übersichtlichkeit werden die hergeleiteten Schaltungen nicht mit ihrem vollständigen Schaltbild wiedergegeben, sondern durch ein *Blockschaltbild*, das nur die Eingänge, Ausgänge und Funktionen ausweist. Da somit nur die *Funktionalität*, nicht aber die *Struktur*, dargestellt wird, spricht man auch von einer Darstellung als *Black Box*, die wir nun auf beide Addierer anwenden.

Abbildung 2.24: Volladdierer (full adder) – Halbaddierer (half adder)

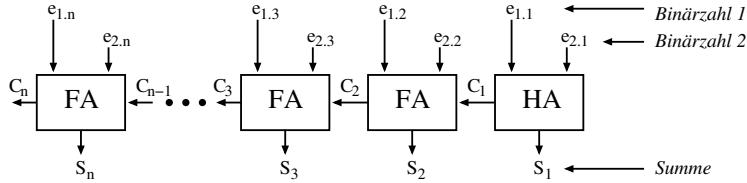

Diese *Module* lassen sich nun wie folgt zusammensetzen (siehe Abbildung 2.25).

Abbildung 2.25: Paralleladdierer

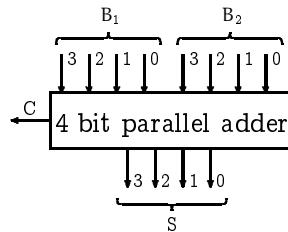

Diese so entstandene Schaltung des *Paralleladdierers* kann wieder als neue Einheit aufgefasst und als einzelnes Schaltelement dargestellt werden. Dabei wenden wir die in der Informatik gängige Vereinbarung an, dass Ein- und Ausgänge bei 0 beginnend bis  $n - 1$  nummeriert werden. Die Summe ist dann  $S = B_1 + B_2$ , wobei  $B_1$  und  $B_2$  mit den beiden Binärzahlen 1 und 2 aus Abbildung 2.25 übereinstimmen und exemplarisch die Wortbreite  $n = 4$  gewählt wurde.

Abbildung 2.26: Blockschaltbild des 4-bit-Paralleladdierers

Durch die Verwendung des Einer- oder Zweierkomplements lässt sich die Subtraktion auf eine Addition zurückführen, so dass man die ersten einfachen Rechenaufgaben von einer Maschine durchführen lassen kann. Bei Paralleladdierern werden meistens auch für die niedrigsten Stellen Volladdierer verwendet, um die Schaltung beliebig erweitern zu können.

Die bisher dargestellten Funktionen sind als *integrierte Schaltungen* (engl. *Integrated Circuits, ICs*) auf einem Baustein *Chip* erhältlich. Ihre Art der Beschaltung (*Pinbelegung*) entnimmt man so genannten *Datenblättern* bzw. *Datenbüchern*.

### 2.2.3 Codierer

*Nomen est omen!*

Plautus, „Der Perser“.

Die Schaltung eines Codierers besitzt bei  $n$  Eingängen, die mit  $e_i$  ( $i = 0, 1, \dots, n - 1$ ) bezeichnet werden, genau  $m = \lceil \log_2(n) \rceil$  Ausgänge, welche die Bezeichnung  $a_j$  ( $j = 0, 1, \dots, m - 1$ ) erhalten. Unter der Bedingung, dass immer nur einer der  $n$  Eingänge aktiv (d.h., logisch 1) sein kann, wandelt der Codierer die Bitfolge, die an den Eingängen  $e_i$  anliegt, in eine Binärzahl an den Ausgängen  $a_j$  um.

In der folgenden Wahrheitstabelle sind die Werte für einen Codierer mit  $n = 8$  Eingängen und dementsprechend  $m = 3$  Ausgängen aufgeschlüsselt.

| $e_7$ | $e_6$ | $e_5$ | $e_4$ | $e_3$ | $e_2$ | $e_1$ | $e_0$ | $a_2$ | $a_1$ | $a_0$ |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 1     |

| 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 1     | 0     |

| 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 1     | 1     |

| 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 1     | 0     | 0     |

| 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 1     |

| 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 0     |

| 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     |

Damit ergeben sich die drei Gleichungen für die Ausgänge zu

$$\begin{aligned} a_0 &= e_1 \vee e_3 \vee e_5 \vee e_7 \\ a_1 &= e_2 \vee e_3 \vee e_6 \vee e_7 \\ a_2 &= e_4 \vee e_5 \vee e_6 \vee e_7 \end{aligned}$$

Um diese Schaltung zu realisieren, brauchen wir nur drei ODER-Gatter mit je vier Eingängen. Es ergeben sich allerdings Probleme, wenn mehrere Eingänge logisch 1 sind. Im Fall von  $e_3 = e_6 = 1$  führt dies zum Ergebnis  $(a_2 a_1 a_0) = (111)_2$ , das aber weder  $(3)_{10}$  noch  $(6)_{10}$  entspricht. Ein weiteres falsches Resultat liefert der Fall, dass *kein* Eingang logisch 1 ist, da dann auch alle Ausgänge logisch 0 sind. Dies ist jedoch identisch mit dem Ergebnis für „Eingang  $e_0$  ist logisch 1“.

Bei Verwendung eines *prioritätsgesteuerten Codierers* treten diese Probleme nicht auf, da diese Schaltung nur jenen Eingang beachtet, dessen Index am größten ist. Bei unserem Beispiel ( $e_3$  und  $e_6$  sind aktiv) wird nur daher nur  $e_6$  codiert. Ein weiterer Ausgang V zeigt zusätzlich an, ob mindestens ein Eingang logisch 1, das Ergebnis also *gültig* (engl. *valid*) ist.

Ein „X“ anstelle der logischen Werte 0 oder 1 in der Wahrheitstabelle bedeutet, dass das Ergebnis nicht abhängig vom Wert ist, den der jeweilige Eingang annimmt („X“ = *don't care*).

| $e_3$ | $e_2$ | $e_1$ | $e_0$ | $a_1$ | $a_0$ | V |

|-------|-------|-------|-------|-------|-------|---|

| 0     | 0     | 0     | 0     | 0     | 0     | 0 |

| 0     | 0     | 0     | 1     | 0     | 0     | 1 |

| 0     | 0     | 1     | X     | 0     | 1     | 1 |

| 0     | 1     | X     | X     | 1     | 0     | 1 |

| 1     | X     | X     | X     | 1     | 1     | 1 |

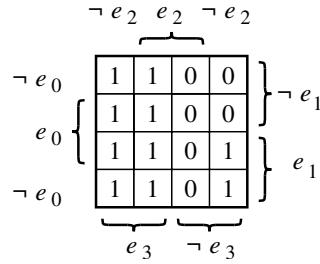

Möchte man eine solche Funktion vereinfachen, muss man im KV-Diagramm für jede *Don't-Care-Variable* den negierten und den nicht negierten Zustand mit dem entsprechenden Eintrag in der Ergebnisspalte ausfüllen. Es gibt selbstverständlich auch *Eingangskombinationen*, die ausgeschlossen werden können oder das Ergebnis nicht beeinflussen. In den entsprechenden Zeilen der Wahrheitstabelle kann man in der Ausgangsspalte eine *Don't-Care-Bedingung* – ebenfalls ein „X“ – eintragen. Im KV-Diagramm wird dann das Feld beliebig als 0 oder 1 interpretiert. Man setzt jedoch den Wert ein, der die bessere Vereinfachung der Funktion bewirkt. In unserem Fall ergibt sich daher für den Ausgang  $a_0$  folgendes KV-Diagramm.

Abbildung 2.27: KV Diagramm mit vier Eingangsvariablen

Ähnlich verfahren wir mit den anderen Ausgängen und erhalten so ihre Funktionen:

$$\begin{aligned} a_0 &= (e_1 \wedge \neg e_2) \vee e_3 \\ a_1 &= e_2 \vee e_3 \\ V &= e_0 \vee e_1 \vee e_2 \vee e_3 \end{aligned}$$

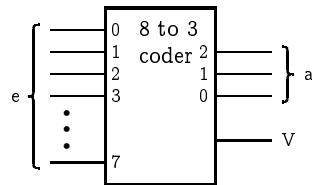

Das Schaltsymbol für einen Codierer beinhaltet als Beschriftung die Relation von Eingängen zu Ausgängen, d. h., für einen Codierer mit 8 Eingängen und 3 Ausgängen schreibt man *8 zu 3* (oder engl. *8 to 3*).

Abbildung 2.28: Blockschaubild eines (8 zu 3)-Codierers

## 2.2.4 Decodierer

Ein *Decodierer* – das Gegenstück zum Codierer – ist eine Schaltung mit  $n$  Ausgängen, die mit  $a_i$  ( $i = 0, 1, \dots, n - 1$ ) bezeichnet werden, und genau  $\lceil \log_2(n) \rceil$  Eingängen. Ein Ausgang geht genau dann auf logisch 1, wenn die Binärzahl, die am Eingang anliegt, gleich seiner Nummer  $i$  ist. Für einen *(3 zu 8)-Decodierer* ergibt sich damit folgende Wahrheitstabelle:

| $e_2$ | $e_1$ | $e_0$ | $a_7$ | $a_6$ | $a_5$ | $a_4$ | $a_3$ | $a_2$ | $a_1$ | $a_0$ |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     |

| 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     |

| 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     |

| 0     | 1     | 1     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     |

| 1     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     |

| 1     | 0     | 1     | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0     |

| 1     | 1     | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     |

| 1     | 1     | 1     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Eine verbesserte Kontrolle über die Schaltung gestattet ein Kontrollsignal, das den Zeitpunkt bestimmt, zu dem die an den Eingängen anliegende Information decodiert werden soll. Die Wahrheitstabelle eines (2 zu 4)-Decodierers ist aus folgender Tabelle ersichtlich, in welcher der neue Eingang mit E bezeichnet wurde (engl. enable). Wenn  $E = 0$  ist, sind alle Ausgänge logisch 0.

| E | e <sub>1</sub> | e <sub>0</sub> | a <sub>3</sub> | a <sub>2</sub> | a <sub>1</sub> | a <sub>0</sub> |

|---|----------------|----------------|----------------|----------------|----------------|----------------|

| 0 | X              | X              | 0              | 0              | 0              | 0              |

| 1 | 0              | 0              | 0              | 0              | 0              | 1              |

| 1 | 0              | 1              | 0              | 0              | 1              | 0              |

| 1 | 1              | 0              | 0              | 1              | 0              | 0              |

| 1 | 1              | 1              | 1              | 0              | 0              | 0              |

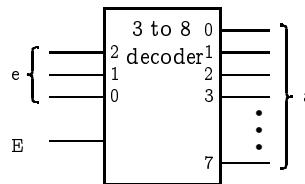

Abbildung 2.29 zeigt das allgemeine Blockschaltbild eines (3 zu 8)-Decodierers.

Abbildung 2.29: Blockschaltbild eines (3 zu 8)-Decodierers

## 2.2.5 Multiplexer

*So let it out and let it in.*

John Lennon, Paul McCartney,

„Hey Jude“.

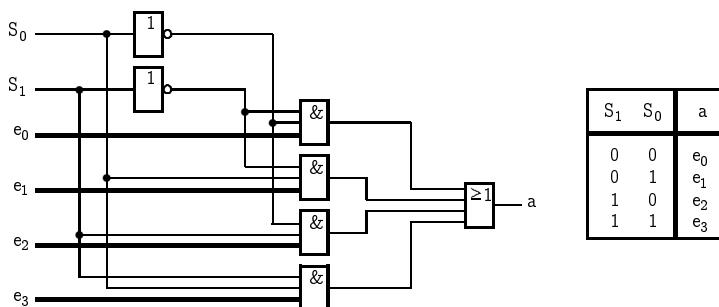

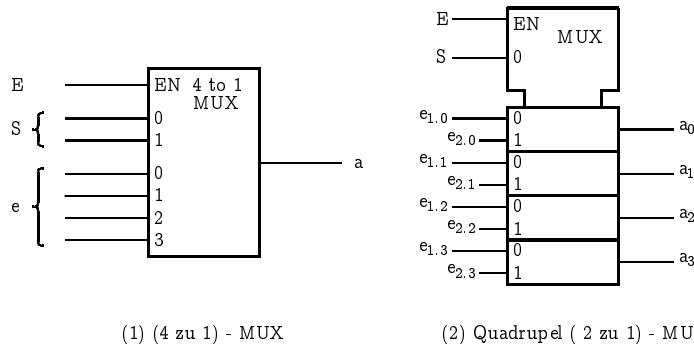

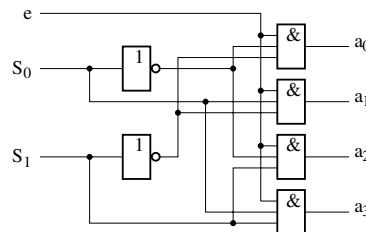

Der Multiplexer ist eine Erweiterung des Codierers. Er wählt aus m binären Eingängen  $e_i$  ( $i = 0, 1, \dots, m - 1$ ) jenen aus, dessen Nummer mit der Zahl  $(S_{n-1} \dots S_1 S_0)_2$  übereinstimmt, die an den Steuervariablen  $S_j$  ( $j = 0, 1, \dots, n - 1$ ) anliegt, und schaltet dessen Information unverändert an den Ausgang durch. Als Beispiel geben wir die Wahrheitstabelle und die Schaltung für einen (4 zu 1)-Multiplexer (engl. 4 to 1 line multiplexer, Abkürzung: 4 to 1 MUX) an.

Abbildung 2.30: (4 zu 1)-Multiplexer

Wir nehmen an, dass die Steuerleitungen den Zustand  $(S_1 S_0) = (10)_2$  haben. Auf diese Weise sperren die Steuerleitungen alle AND-Gatter ausser dem zweituntersten. Der Ausgang des Gatters hängt nur vom Eingang  $e_2$  ab. Das nachgeschaltete OR-Gatter leitet die Information an den Ausgang der Schaltung weiter. Zum besseren Verständnis wurden die Leitungen der Eingänge  $e_i$  ( $i = 0, 1, 2, 3$ ) bis zum ersten Gatter dicker gezeichnet.

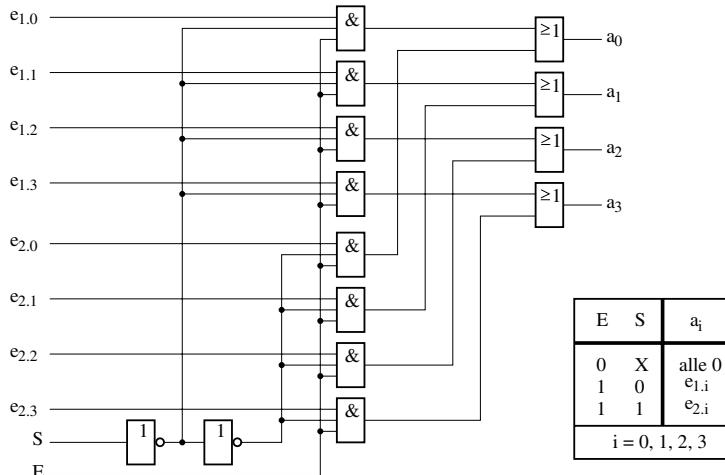

Ohne Belegung der Eingänge soll immer die Information des Eingangs  $e_0$  am Ausgang anliegen. Die Schaltung zeigt jedoch das gleiche Verhalten auch bei der Eingangskombination  $(S_1 S_0) = (00)$ . Um Fehlinterpretationen zu verhindern, führt man eine *Enable*-Leitung (E) ein, die darüber entscheidet, zu welchem Zeitpunkt der ausgewählte Eingang durchgeschaltet wird. Ist E logisch 0, dann nimmt auch der Ausgang den Wert 0 an. Bei der so verbesserten Schaltung soll es außerdem möglich sein, vier Eingänge an vier Ausgänge durchzuschalten, um ein ganzes Codewort (mehrere zusammengehörende binäre Informationen) anzuwählen und an den entsprechenden Ausgängen ausgeben zu können. Bei einem *Quadrupel 2 zu 1 MUX* (vierfach 2 zu 1 MUX) steuert der Selektionseingang S, welches der beiden Wörter  $e_{1,i}$  oder  $e_{2,i}$  an die Ausgänge  $a_i$  ( $i = 0, 1, 2, 3$ ) durchgeschaltet wird. Hinsichtlich des Selektionseingang S kann festgestellt werden, dass logisch gesehen ein erster Inverter – wie in der Graphik dargestellt – eigentlich nicht notwendig ist. Dieser gilt vielmehr der Entkopplung zwischen dem Multiplexer und der treibenden Schaltung am S-Eingang.

Abbildung 2.31: Quadrupel (2 zu 1)-Multiplexer

Die Abbildung 2.31 zeigt die Wahrheitstabelle und die Schaltung eines vierfachen (2 zu 1)-Multiplexers.

Rein aus logischer Sicht würde in der Schaltung der Abbildung 2.31 beim S-Eingang eine Negationsstufe allein genügen, um getrennt je 4 UND-Gatter ansteuern zu können. Um jedoch zu der vorgesetzten, treibenden Stufe eine Entkopplung herzustellen, wird ein zusätzlicher Inverter vorgesehen. Laufzeitmäßig ist dies allerdings entsprechend zu berücksichtigen.

Zuletzt seien die zugehörigen Blockschaltbilder in Abbildung 2.32 angegeben. Beim Quadrupel (2 zu 1)-Multiplexer beeinflussen sowohl der Steuereingang S als auch die *Enable*-Leitung alle Ein- bzw. Ausgänge. Dieser Umstand wird dadurch verdeutlicht, dass sie in einem eigenen, übergeordneten Kontrollblock abgebildet werden. Zuleitungen, die in einem solchen Block gesammelt werden, steuern alle darunter liegenden Bereiche.

Abbildung 2.32: Blockschaltbild eines (4 zu 1)- und eines Quadrupel (2 zu 1)-Multiplexers

## 2.2.6 Demultiplexer

Beim Demultiplexer bestimmen als Gegenstück zum Multiplexer die Steuereingänge  $S_i (i = 0, 1, \dots, n-1)$ , auf welchen Ausgang  $a_j (j = 0, 1, \dots, 2^n - 1)$  die Information des Eingangs e durchgeschaltet werden. Eine Realisierung eines (1 zu 4)-Demultiplexers stellt die Abbildung 2.33 dar.

Ein Enable Eingang könnte hier auch dazugeschaltet werden, um das Problem zu beseitigen, dass im Ruhezustand ( $S_1 S_0 = (00)$ ) das Signal vom Eingang e an den Ausgang  $a_0$  durchgeschaltet wird, zu lösen;

Das Blockschaltbild eines Demultiplexers ist analog zu dem eines Multiplexers aufgebaut.

Abbildung 2.33: (1 zu 4)-Demultiplexer

## 2.3 Sequenzielle Logik

Bei den bisher entworfenen Schaltungen hing das Ergebnis zu jeder Zeit direkt von den Eingängen ab. Bei einer Änderung, stellten sich auch die Ausgänge entsprechend den logischen Zusammenhängen folgend sofort bzw. nach Ablauf der Gatterlaufzeiten (engl. *propagation delay*) auf die neuen Werte ein. Praktisch ist es jedoch von Vorteil, Informationen eine bestimmte Zeit speichern zu können, da nicht immer alle nötigen Daten zur selben Zeit gleich lang zur Verfügung stehen. Dafür benötigt man *Speicherelemente*. Die in einer Schaltung gespeicherten Daten, die unter

anderem die nächsten Ausgangskombinationen mitbestimmen, legen den *Zustand* des Systems fest.

Schaltungen, die *Speicherelemente* enthalten, heißen *sequenzielle Schaltungen*. Deren Ausgänge hängen vom Zustand der Eingänge und des Systems ab. Wir unterscheiden hierbei zwei Haupttypen sequenzieller Logik, nämlich *synchrone* und *asynchrone*. Synchrone Schaltungen sind dadurch gekennzeichnet, dass Zustandswechsel nur zu bestimmten diskreten Zeitpunkten geschehen können, während der Zustand von asynchronen Schaltungen zu jedem beliebigen Zeitpunkt variieren kann. Wegen des deterministischen Verhaltens werden in der Praxis synchrone Schaltungen bevorzugt.

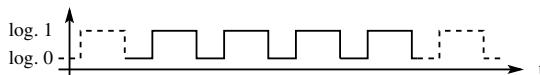

Bei synchronen Schaltungen bewirkt ein *Taktgeber* (engl. *clock pulse generator*) die diskreten Zustandsübergänge. Schaltungen, die eine definierte periodische Pulsfolge ausgeben, werden *Oszillatoren* genannt. Das Taktsignal wird als *Clock Pulse* bezeichnet. Daher werden synchrone sequenzielle Schaltungen auch *Clocked Sequential Circuits* genannt. Deren Pulsfolge zeigt Abbildung 2.34. Die strichlierten Impulse zeigen an, dass es sich um ein periodisches Signal handelt.

Abbildung 2.34: Clock-Pulse-Signal

### 2.3.1 Latches

*Computer sind die Papierkörbe

fürs Gedächtnis.*

Erhard Blank

(\*1942), Schriftsteller und Maler

Ein Schaltelement, das in der Lage ist, binäre Information zu speichern, nennt man *Latch*. Eine Form von Latches sind *Flip Flops*; in der Literatur, die zwischen „Flip-Flops“ und „Latches“ unterscheidet, werden flankengetriggerte Speicher für binäre Informationen als Flip-Flops, alle übrigen als Latches bezeichnet. In diesem Buch verwenden wir die beiden Ausdrücke einfachhaber als Synonyme. In einem Latch kann man – solange die Stromversorgung vorhanden ist – eine binäre Information auf unbestimmte Zeit speichern, abfragen und verändern.

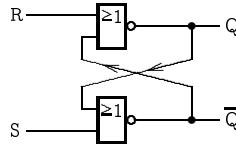

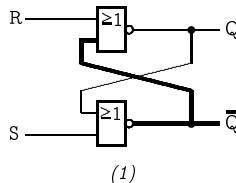

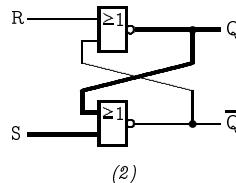

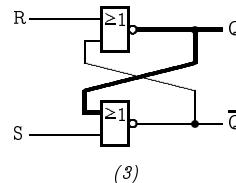

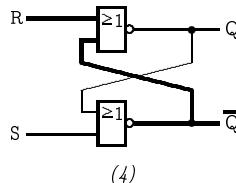

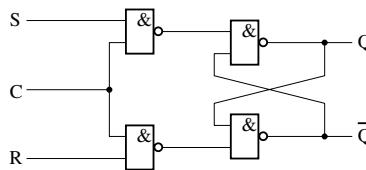

Die einfachste Form ist das *RS-Latch*. Die Abkürzungen R und S stehen für *Reset* und *Set* oder übersetzt *Löschen* und *Setzen*. Sie verkörpern die einfachsten binären Speicherfunktionen, nämlich das Setzen des Ausgangs auf logisch 0 (*Reset*) oder logisch 1 (*Set*). Das ist gleichbedeutend mit dem Speichern von 0 oder 1. Das RS-Latch kann etwa aus NOR-Gattern aufgebaut werden und besitzt neben den Eingängen R und S die Ausgänge Q und  $\overline{Q}$ . An Q kann die gespeicherte und an  $\overline{Q}$  die negierte Information abgelesen werden. In Schaltplänen werden für gewöhnlich die negierten Ein- oder Ausgänge durch Überstreichungen gekennzeichnet, da dies meist deutlicher als ein Operatorsymbol ist und außerdem nur die Anschlüsse, nicht jedoch die ganze Funktion, betroffen ist. In Abbildung 2.35 ist die Schaltung eines RS-Latch angegeben, die aus zwei rückgekoppelten NOR-Gattern besteht.

Abbildung 2.35: RS-Latch

Die Informationspfade, die logisch 1 sind, werden in den nächsten vier Abbildungen durch stärker gezogene Linien gekennzeichnet. Im Startzustand sei die gespeicherte Information logisch 0, d.h.,  $Q$  liefert 0 und  $\bar{Q}$  den Wert 1 (siehe Teilbild 1). Da die Ausgänge an die Gatter zurückgeführt werden (rückgekoppelt sind), bleibt die Information erhalten, solange die Eingänge sich in ihrem Ruhezustand (logisch 0) befinden. Dies wird dadurch bewirkt, dass  $\bar{Q}$  mit Hilfe des oberen NOR-Gatters den Ausgang  $Q$  auf 0 hält und die beiden logischen Nullen auf den Eingängen des unteren NOR-Gatters  $\bar{Q}$  weiterhin mit dem Wert 1 versorgen.

(1)

Bei der Eingangskombination  $R = 1$  und  $S = 0$  bleibt der Zustand des Latch unverändert. Im Fall  $R = 0$  und  $S = 1$  wird der Ausgang  $Q$  logisch 1. Da auch neue Werte am Eingang des NOR-Gatters vorliegen, gilt nun  $\bar{Q} = 0$  (siehe Teilbild 2). Auf diese Weise kann die Information (logisch 1) im Latch gespeichert werden. Kehrt der Eingang  $S$  in seinen Ruhezustand zurück, erhält man  $S = 0$  und  $R = 0$ . Dabei bleibt der Zustand des Latches ebenfalls unverändert, da durch die Rückkopplung von  $Q$  der Setzvorgang praktisch „eingefroren“ ist (Teilbild 3).

(2)

(3)

Erst bei der Eingangskombination von  $S = 0$  und  $R = 1$  wechselt der Zustand des Latch. Am Ausgang ergeben sich damit folgende Werte:  $Q = 0$ ,  $\bar{Q} = 1$  (Teilbild 4). Wir sind damit wieder im Ausgangszustand (Teilbild 1).

(4)

Der Fall, dass beide Eingänge R und S gleichzeitig den Wert logisch 1 einnehmen, ist bei einem RS-Latch nicht definiert, da dies nämlich bedeuten würde, dass Q und  $\bar{Q}$  logisch 0 wären. Abschließend wird noch die Wahrheitstabelle angegeben.

| S | R | Q | $\neg Q$ |                      |

|---|---|---|----------|----------------------|

| 1 | 0 | 1 | 0        | <i>Set</i> -Status   |

| 0 | 0 | 1 | 0        |                      |

| 0 | 1 | 0 | 1        | <i>Reset</i> -Status |

| 0 | 0 | 0 | 1        |                      |

| 1 | 1 | 0 | 0        | nicht definiert      |

Diese Schaltung erlaubt es, Information beliebig lange zu speichern. Sie gehört jedoch zu den asynchronen Schaltungen, da ein Zustandswechsel zu jeder Zeit erfolgen kann. Deshalb fügen wir einen Kontrolleingang C (engl. *control*) hinzu, der es ermöglicht, den Zeitpunkt zu steuern, an dem der Zustandsübergang erfolgt bzw. an dem die Information von den Eingängen in den Speicher und somit auf die Ausgänge übernommen wird (siehe Abbildung 2.36). Weiter haben wir diesmal das Latch mit NAND- statt mit NOR-Gattern aufgebaut und im Vorbereich des Latches eine Gatterlogik mit einem Kontrolleingang C hinzugefügt.

Abbildung 2.36: RS-Latch mit Kontrolleingang C

Aus der Schaltung ist erkennbar, dass bei Anliegen von logisch 0 am Kontrolleingang C unabhängig von den Eingängen R und S kein Zustandswechsel erfolgen kann. Bei C = 1 übernimmt das Latch die Information von R und S. Wendet man die *de Morganschen Gesetze* an, erkennt man, dass die Specherschaltung die gleichen Eigenschaften wie das RS-Latch besitzt, da die Eingänge R und S negiert durchgeschaltet werden. Die Wahrheitstabelle hat daher die folgende Gestalt:

| C | S | R | Nächster Zustand von Q       |

|---|---|---|------------------------------|

| 0 | X | X | Keine Änderungen             |

| 1 | 0 | 0 | Keine Änderungen             |

| 1 | 0 | 1 | $Q=0$ ; <i>Reset</i> -Status |

| 1 | 1 | 0 | $Q=1$ ; <i>Set</i> -Status   |

| 1 | 1 | 1 | Nicht definiert              |

Nachdem der Kontrolleingang den Zeitpunkt bestimmt, an dem die Information in den Speicher übernommen wird, und sich somit die Zustände nur zu diskreten Zeitpunkten ändern, liegt eine *synchrone Schaltung* vor.

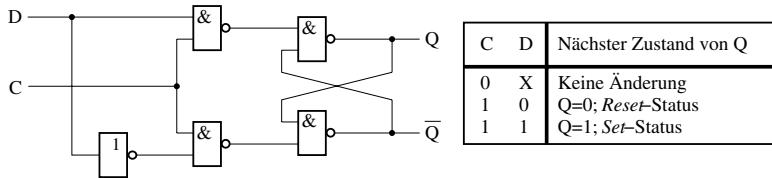

Zuletzt wollen wir noch den nicht definierten Fall  $R = S = 1$  behandeln. Dabei geht man davon aus, dass der Wert eines logischen binären Wert D gespeichert werden soll. Daraus leitet sich der Name *D-Latch* ab. Das zusätzliche NAND-Gatter am Eingang der Schaltung erzwingt, dass die ehemaligen R- und S-Eingänge jetzt stets zueinander invertiert sind. Auf diese Weise wird

der undefinierte Zustand abgefangen. Der Kontrolleingang C bestimmt ausserdem den Zeitpunkt der Übernahme der anliegenden Information D in den Speicher.

Abbildung 2.37: D-Latch

Abbildung 2.38: Triggern eines Eingangs

Betrachtet man obige Wahrheitstabelle, erkennt man, dass sich der Zustand eines beliebigen Ausgangs nur ändern kann, solange C logisch 1 ist. Während dieser Zeit verhält sich das *D-Latch* wie eine asynchrone Schaltung, falls der Eingang D seinen Wert wechselt. Eine Lösung dafür stellen Schaltelemente dar, die auf den Zustandswechsel (entweder von 0 auf 1 oder von 1 auf 0) reagieren.

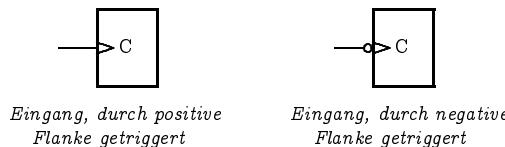

Ein Bauteil mit einem Triggereingang schaltet Informationen nur bei einem Zustandswechsel durch. Bei einem Wechsel von 0 auf 1 liegt eine *positiven*/ und bei einem Sprung von 1 auf 0 eine *negative Flanke* vor (Abbildung 2.38). Durch diese Flankentriggerung kann ein Zustandswechsel wirklich nur zu diskreten Zeitpunkten erfolgen.

Steuereingänge, die nur auf Zustandswechsel reagieren, werden in den Blockschaltbildern durch besondere Symbole dargestellt. Beispiele dafür finden sich in der Abbildung 2.38.

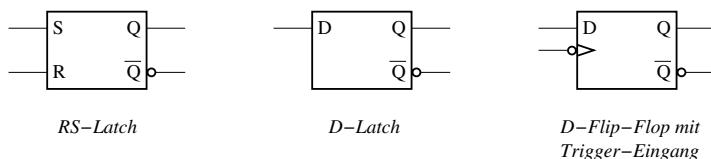

Wie wir gesehen haben, gibt es verschiedene Ausführungen von Latches. Einige wichtige Schaltsymbole sind in der folgenden Abbildung abgebildet (so besitzt die rechte Schaltung einen Triggereingang, der auf die negative Flanke reagiert).

Abbildung 2.39: Blockschaltbilder einiger Latches

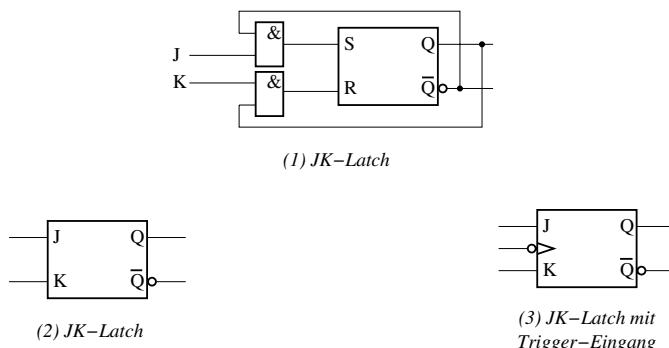

Weiter ist noch das *JK-Latch* zu erwähnen. Da die nicht definierte Situation  $R = S = 1$  des RS-Latch hier anders als beim D-Latch bewältigt wird, besitzt es sowohl den *Set*-Eingang als auch den *Reset*-Eingang.

Die folgenden Überlegungen führen zum Aufbau eines JK-Latch:

- Es ist nicht erforderlich, ein Speicherelement, das bereits den Wert 1 enthält, nochmals zu setzen.

- Ein zurückgesetztes Latch muss nicht erneut gelöscht werden.

Das RS-Flip-Flop löst also nur dann die Set-Funktion aus, falls  $\bar{Q}$  logisch 1 ist, und löscht nur, wenn Q den Wert 1 hat. Dies kann dadurch bewirkt werden, dass man die entsprechenden Ausgänge eines RS-Latches zurückkoppelt und jeweils über ein AND-Gatter mit den Eingängen verbindet.

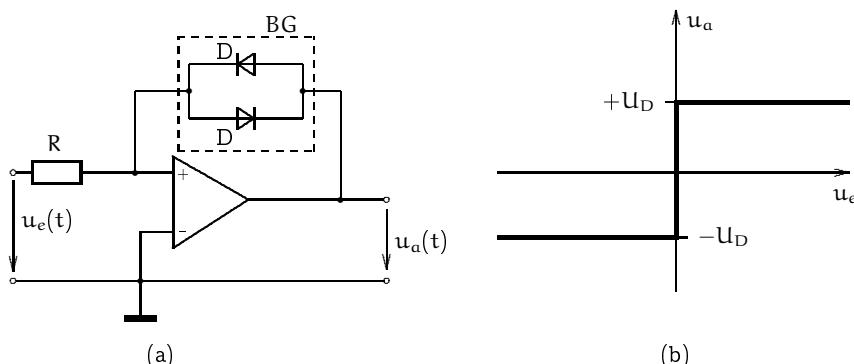

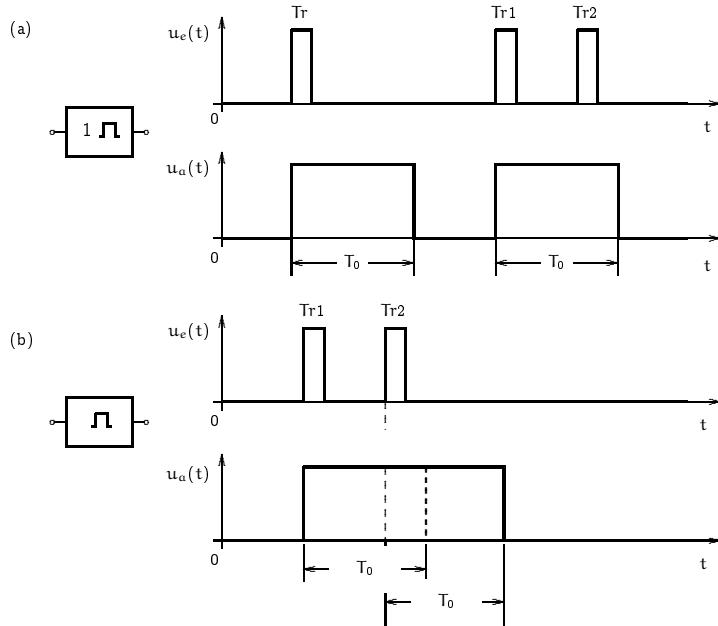

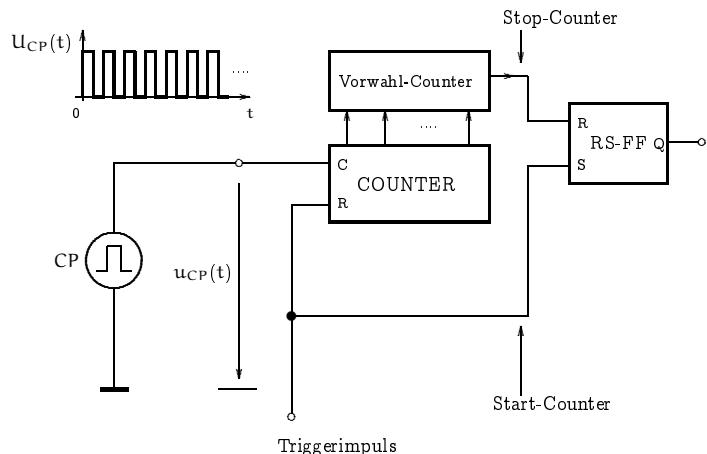

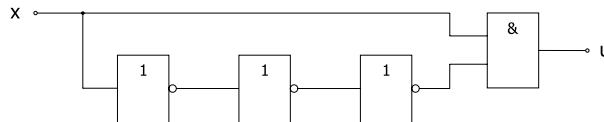

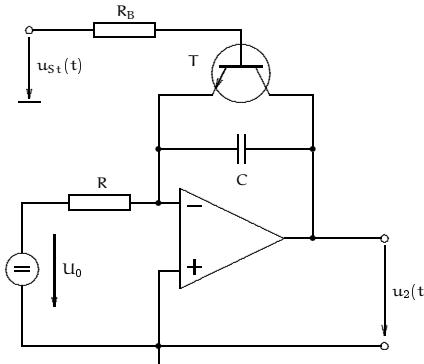

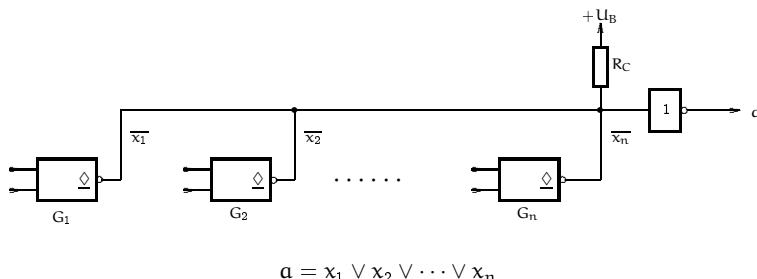

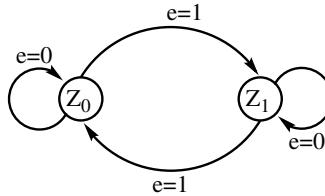

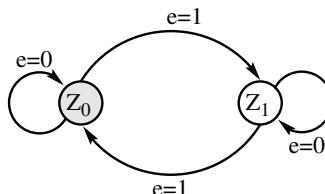

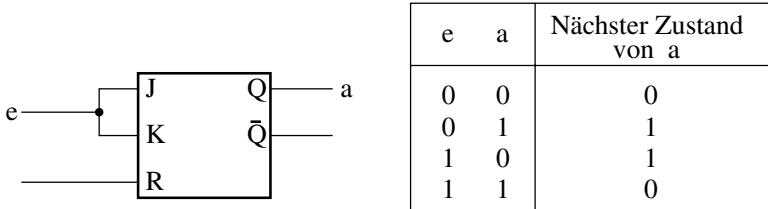

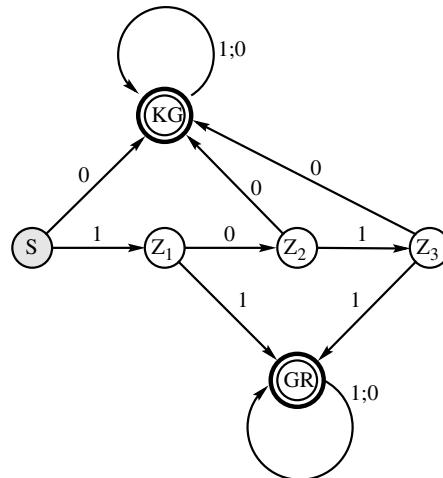

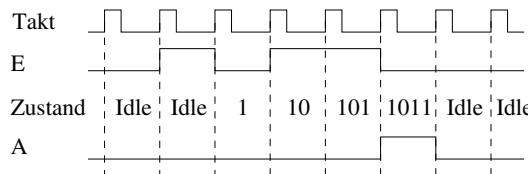

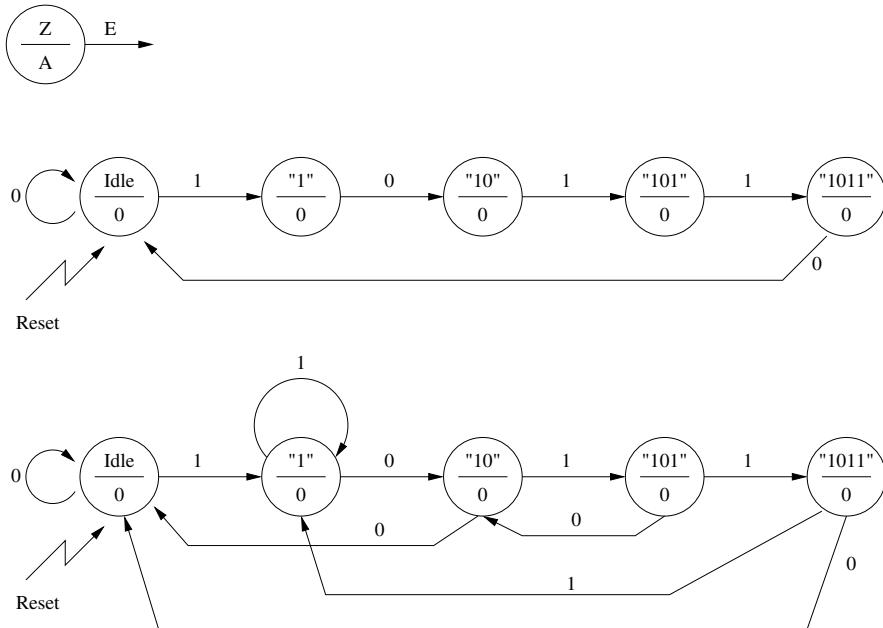

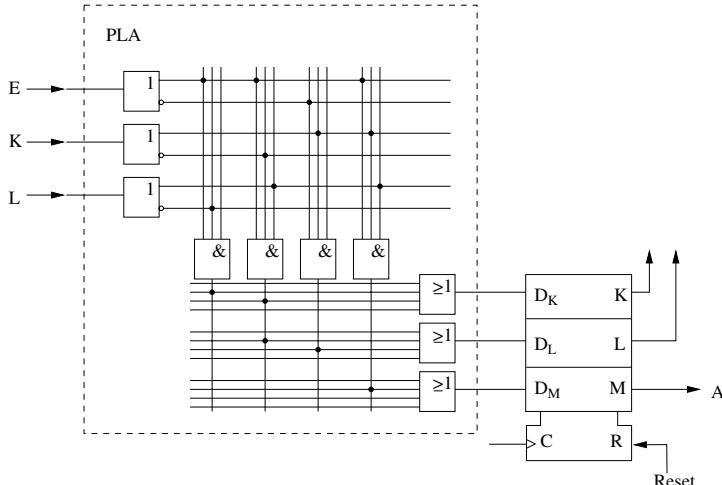

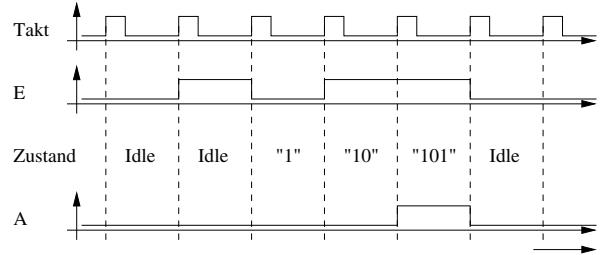

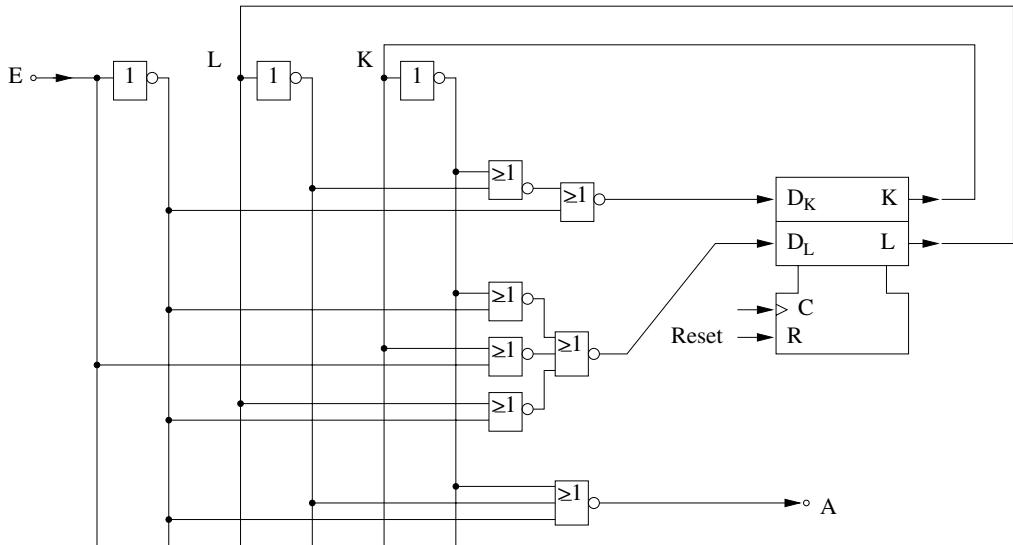

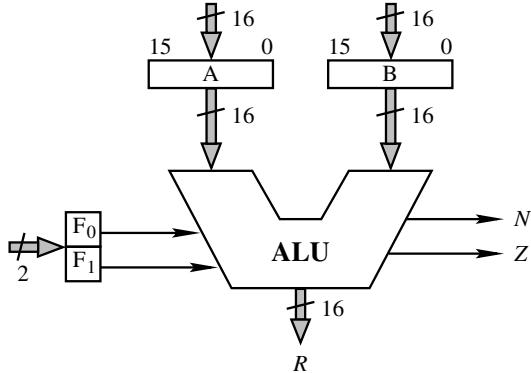

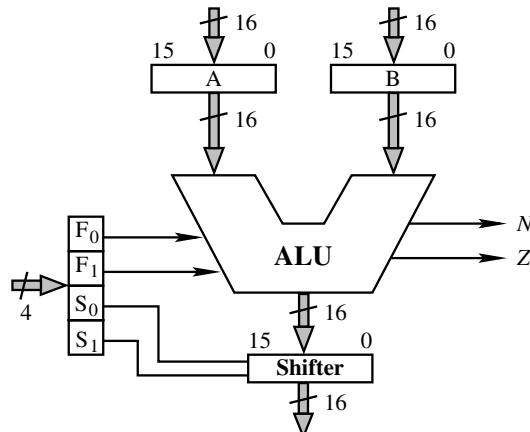

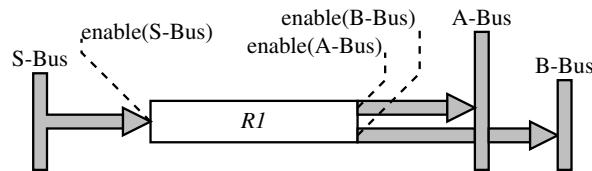

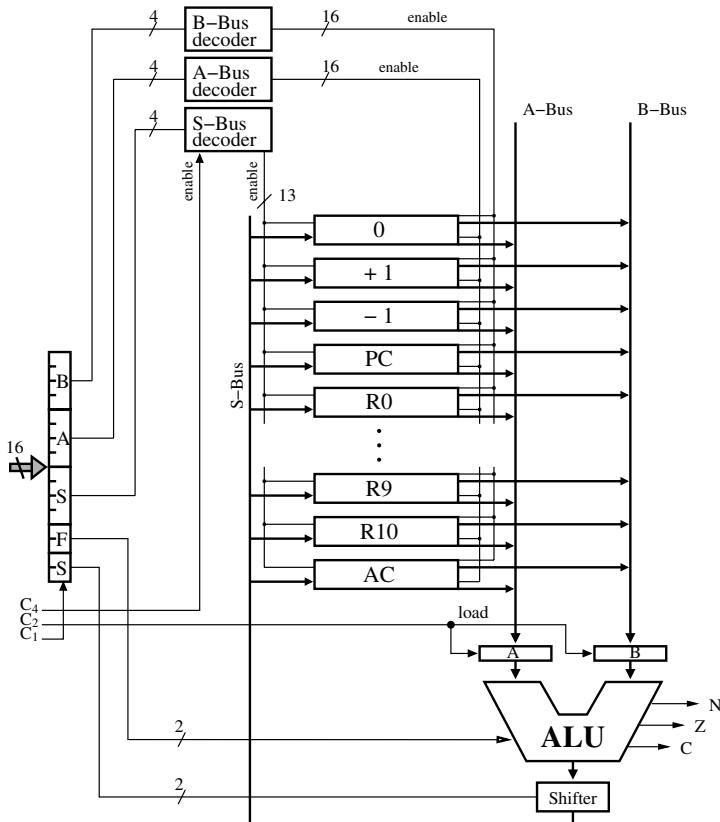

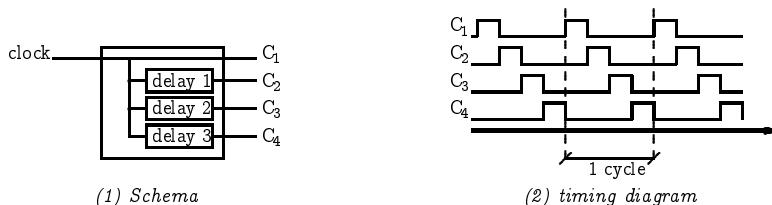

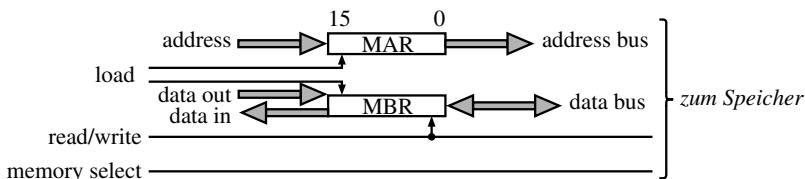

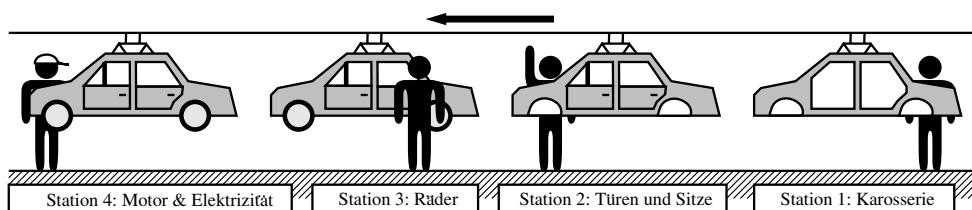

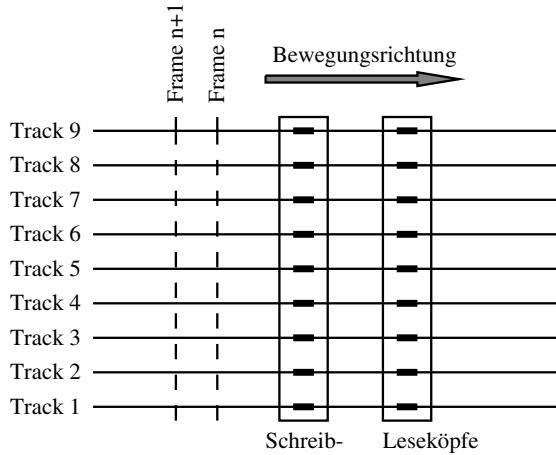

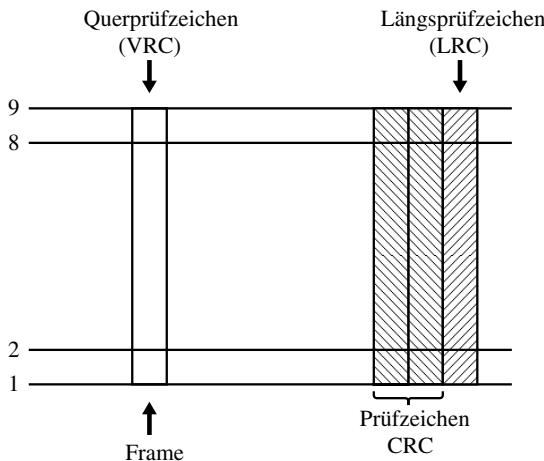

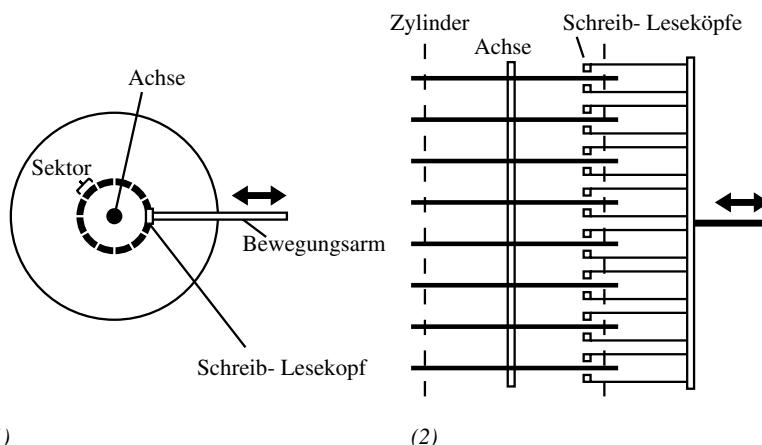

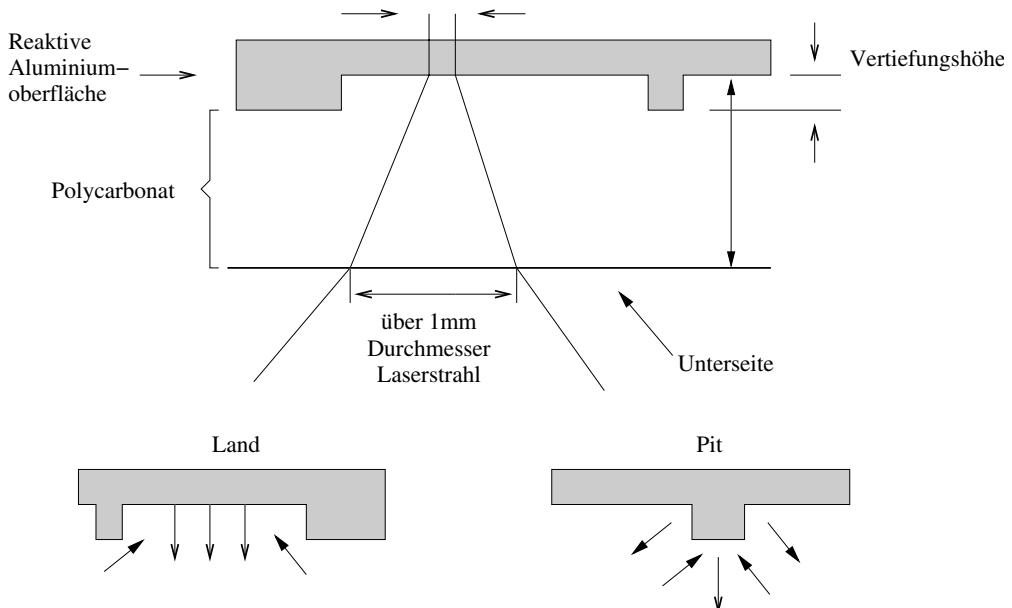

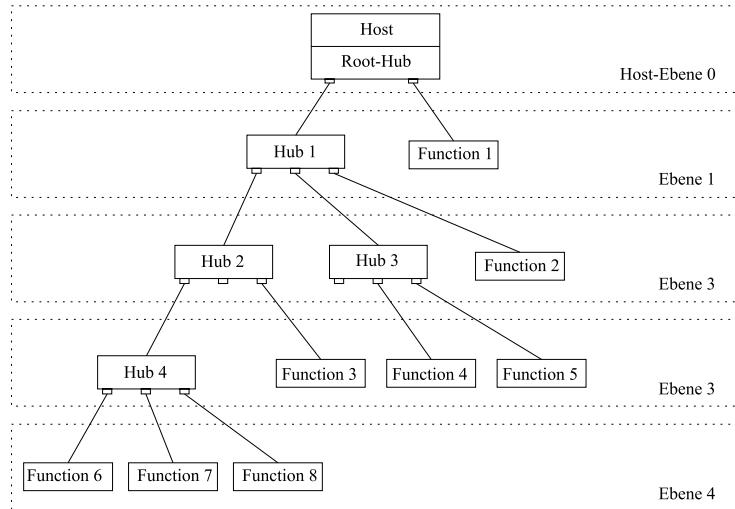

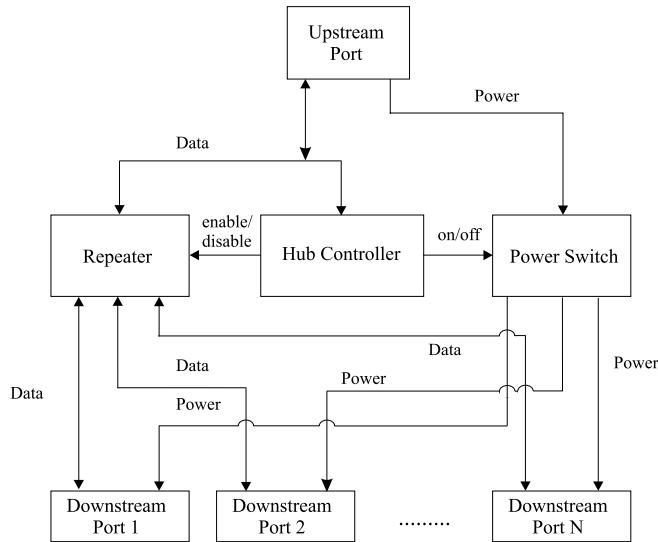

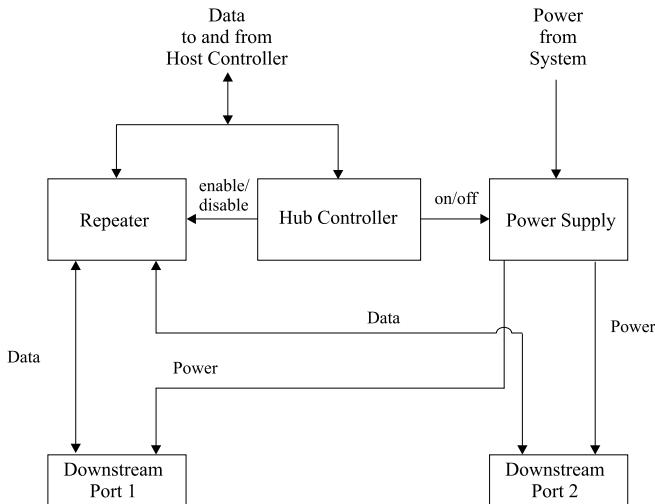

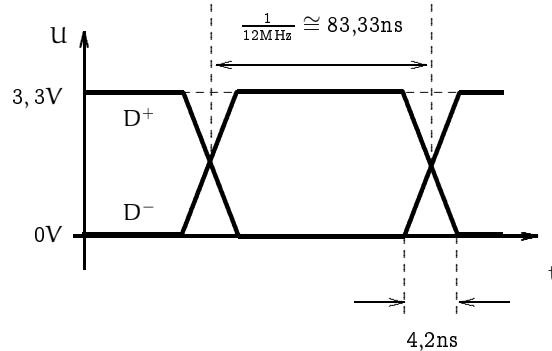

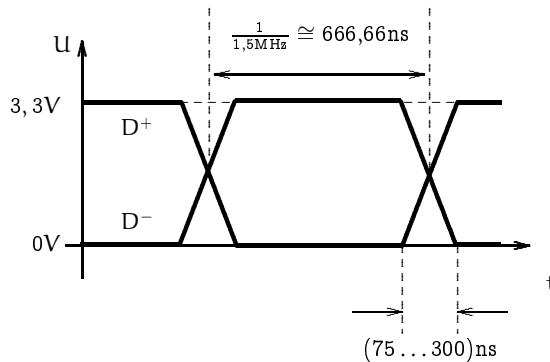

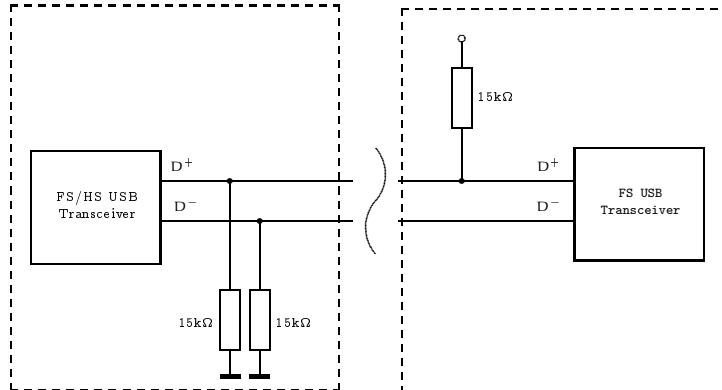

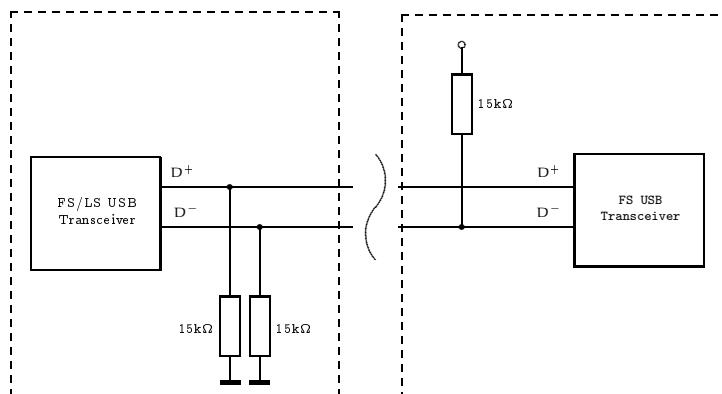

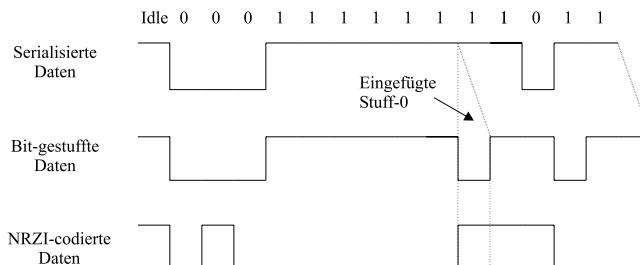

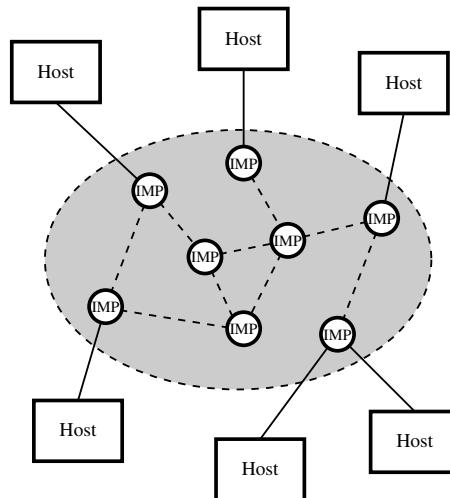

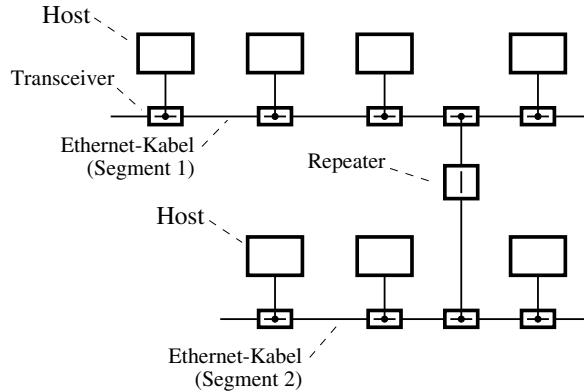

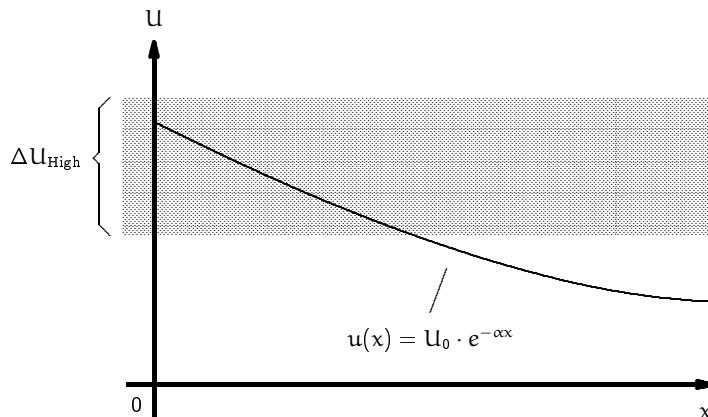

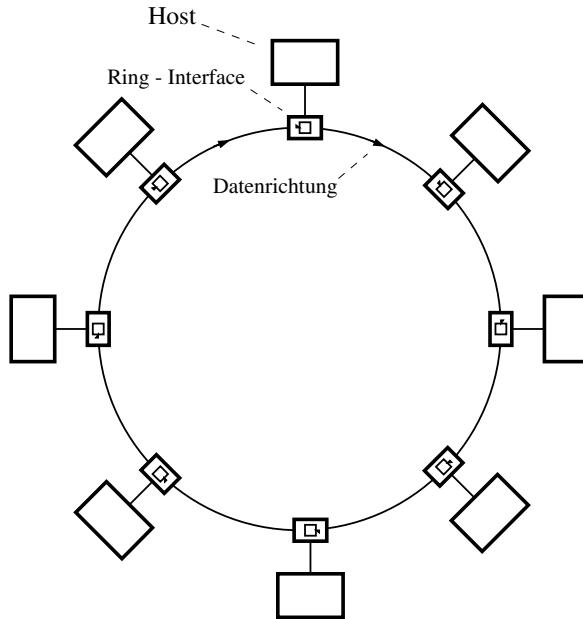

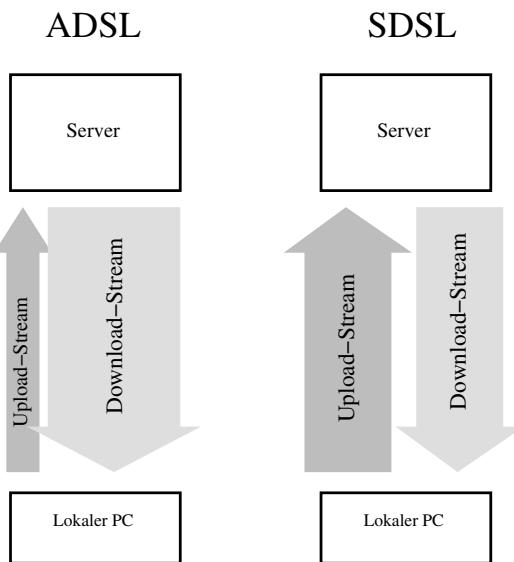

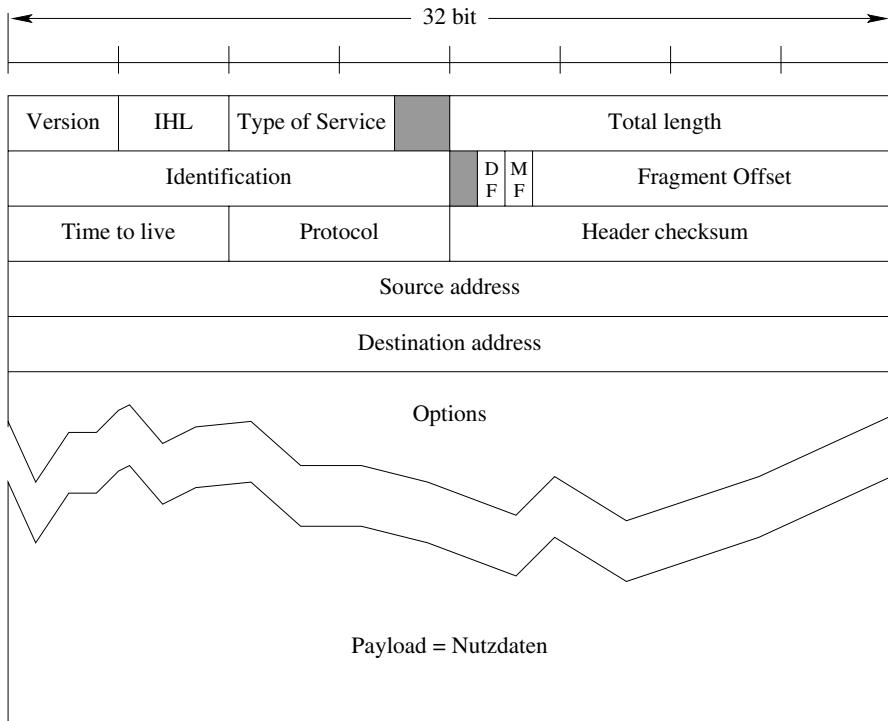

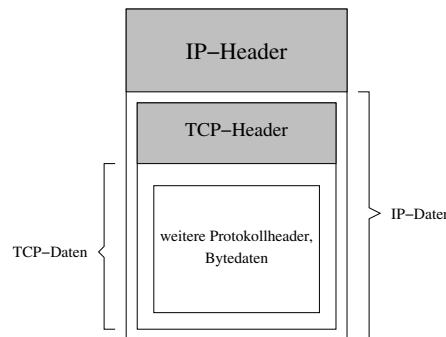

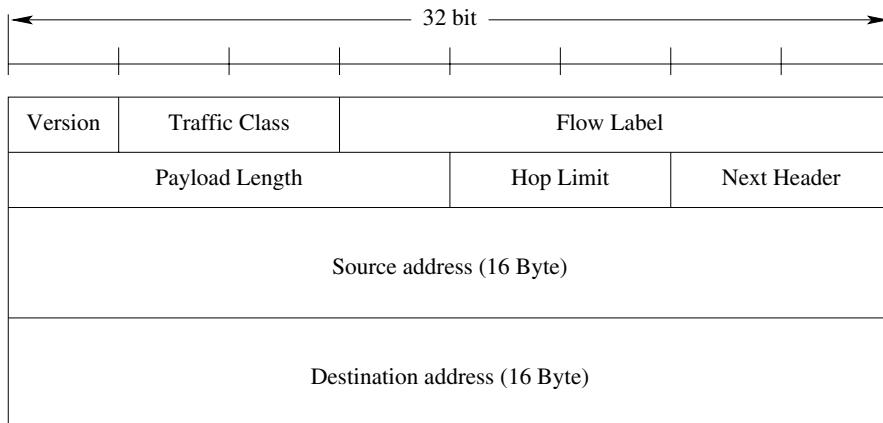

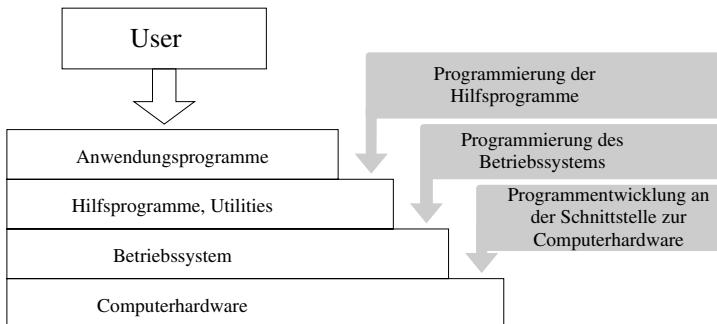

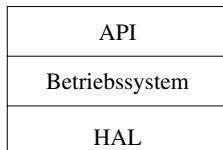

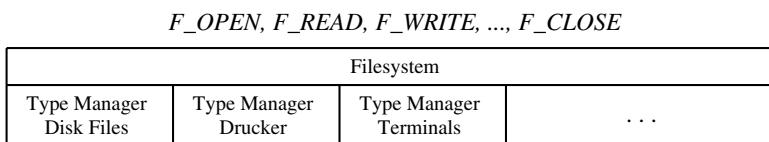

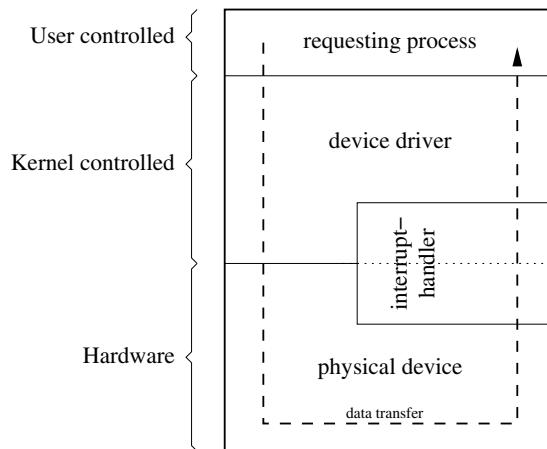

Abbildung 2.40: JK-Latch