# Digital Design

WS 2019

# Vorbesprechung:

HO: 10<sup>15</sup> - 12<sup>00</sup> HS 13

Folien in Towel

FR: 11<sup>15</sup> - 13<sup>00</sup> EI 10

Prüfung: Potentielle Prüfungsfragen in rot.

## Inhalt:

- 1 Grundlagen → chips

- 2 ASIC-Fertigung

- 3 CMOS-Logik

- 4 Design-Flow

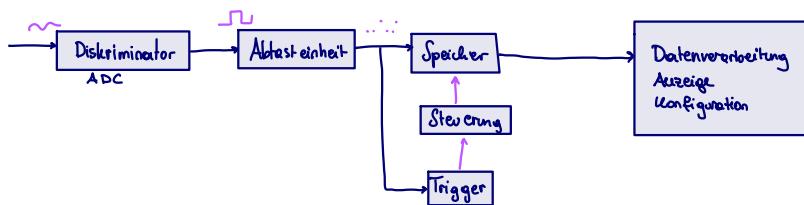

- 5 Speichertechnologien

- 6 ASIC-Zieltechnologien → VHDL

- 7 Temperatur & Verlustleistung

- 8 Datenblatt-Angaben

- 9 Synchrones Design & Metastabilität

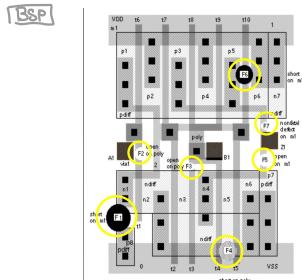

- 10 Defekte

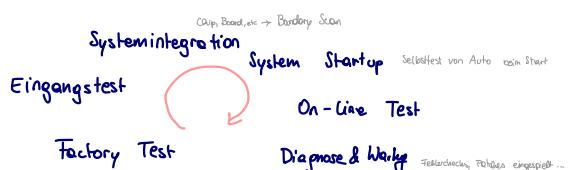

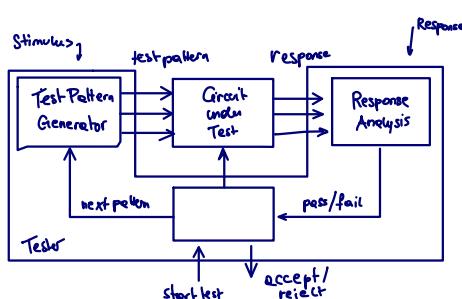

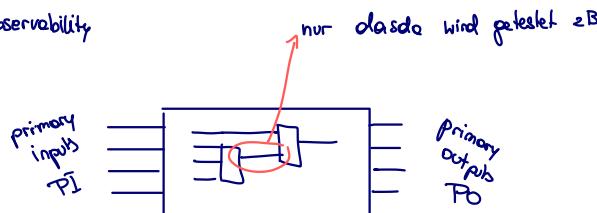

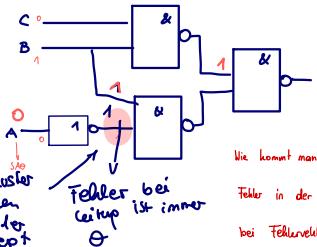

- 11 Test

- 12 Logikanalysator

Taschenrechner (nicht programmierbar)

Beispiele können sich WTH

mind. 49 < 48 ist negativ

Pro Theorie 4-8 Punkte

KV Diagramme kommt fast immer + AOI / OAI 1,5 h

Beispielfragen

(1 Wo für FR max!)

(Stoff erklären nicht)

## Literatur:

- Digital Design - Principles & Practices

- Buch 2

## Allgemeine Erkenntnisse

laufzeit

Reaktivität (mehr als High/Low)

Temperatur

parallele Prozesse → nicht alles nötig der Reihenfolge

Modellierung v. Algorithmen

Hierarchien

Fehlermodelle

Dies sind alles Modellierungen

konzepte, die sie aus R, C etc.

aufbauen

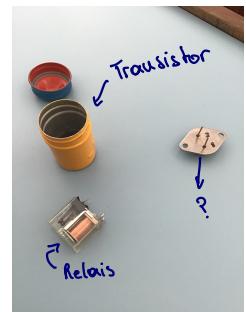

# Grundlagen

Physik - elektromagnetisches Feld, Thermodynamik

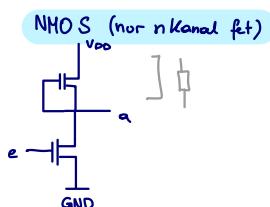

Transistoren - Schwellspannung, Ausgangstrom

Schalter - Steuerg

} Diode

Gatter - logische Regel / Verknüpfung

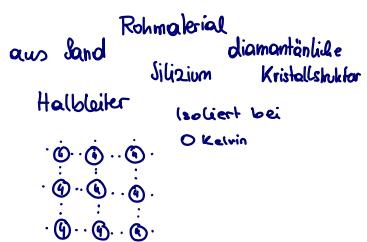

Transistor: (Halbleiter)

= Halbleiterbauelement

= steuerbarer Widerstand

ALU: arithmetic logic unit

Assembler: übersetzt Assembler in Maschinensprache

Registerausfert RTL (Abstraktionsebene von integrierten Schaltkreisen) High level Darstellungen, ALU

Assembler - Registerfile, Befehl, Sprung

Hochsprache Datentyp, Zuweisung

Algorithmen Reiter, Signalverarbeitung

| Bezeichnung | Schaltsymbol nach IEC 60617      | ANSI Schaltsymbol       | Boolescher Ausdruck         | Wahrheitstabelle                                                                                                                                                                                                                                                                                            |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

|-------------|----------------------------------|-------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|-------------------------|---|---|---|---|---|---|---|---|---|---|---|---|

| AND         | a ————— & ————— b ————— y        | a ————— b ————— y       | $y = a \& b$                | <table border="1"> <thead> <tr> <th>b</th><th>a</th><th><math>a \&amp; b</math></th></tr> </thead> <tbody> <tr> <td>0</td><td>0</td><td>0</td></tr> <tr> <td>0</td><td>1</td><td>0</td></tr> <tr> <td>1</td><td>0</td><td>0</td></tr> <tr> <td>1</td><td>1</td><td>1</td></tr> </tbody> </table>            | b | a              | $a \& b$                | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 |

| b           | a                                | $a \& b$                |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 0           | 0                                | 0                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 0           | 1                                | 0                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 1           | 0                                | 0                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 1           | 1                                | 1                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| OR          | a ————— $\geq 1$ ————— b ————— y | a ————— b ————— y       | $y = a \vee b$              | <table border="1"> <thead> <tr> <th>b</th><th>a</th><th><math>a \vee b</math></th></tr> </thead> <tbody> <tr> <td>0</td><td>0</td><td>0</td></tr> <tr> <td>0</td><td>1</td><td>1</td></tr> <tr> <td>1</td><td>0</td><td>1</td></tr> <tr> <td>1</td><td>1</td><td>1</td></tr> </tbody> </table>              | b | a              | $a \vee b$              | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| b           | a                                | $a \vee b$              |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 0           | 0                                | 0                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 0           | 1                                | 1                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 1           | 0                                | 1                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 1           | 1                                | 1                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| NOT         | a ————— 1 ————— o-y              | a ————— o-y             | $y = \overline{a}$          | <table border="1"> <thead> <tr> <th>a</th><th><math>\overline{a}</math></th></tr> </thead> <tbody> <tr> <td>0</td><td>1</td></tr> <tr> <td>1</td><td>0</td></tr> </tbody> </table>                                                                                                                          | a | $\overline{a}$ | 0                       | 1 | 1 | 0 |   |   |   |   |   |   |   |   |   |

| a           | $\overline{a}$                   |                         |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 0           | 1                                |                         |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 1           | 0                                |                         |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| NAND        | a ————— & ————— o-y              | a ————— b ————— o-y     | $y = \overline{a \& b}$     | <table border="1"> <thead> <tr> <th>b</th><th>a</th><th><math>\overline{a \&amp; b}</math></th></tr> </thead> <tbody> <tr> <td>0</td><td>0</td><td>1</td></tr> <tr> <td>0</td><td>1</td><td>1</td></tr> <tr> <td>1</td><td>0</td><td>1</td></tr> <tr> <td>1</td><td>1</td><td>0</td></tr> </tbody> </table> | b | a              | $\overline{a \& b}$     | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 |

| b           | a                                | $\overline{a \& b}$     |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 0           | 0                                | 1                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 0           | 1                                | 1                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 1           | 0                                | 1                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 1           | 1                                | 0                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| NOR         | a ————— $\geq 1$ ————— o-y       | a ————— b ————— o-y     | $y = \overline{a \vee b}$   | <table border="1"> <thead> <tr> <th>b</th><th>a</th><th><math>\overline{a \vee b}</math></th></tr> </thead> <tbody> <tr> <td>0</td><td>0</td><td>1</td></tr> <tr> <td>0</td><td>1</td><td>0</td></tr> <tr> <td>1</td><td>0</td><td>0</td></tr> <tr> <td>1</td><td>1</td><td>0</td></tr> </tbody> </table>   | b | a              | $\overline{a \vee b}$   | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 |

| b           | a                                | $\overline{a \vee b}$   |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 0           | 0                                | 1                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 0           | 1                                | 0                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 1           | 0                                | 0                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 1           | 1                                | 0                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| XOR         | a ————— $\neq 1$ ————— b ————— y | a ————— b ————— o-y     | $y = a \oplus b$            | <table border="1"> <thead> <tr> <th>b</th><th>a</th><th><math>a \oplus b</math></th></tr> </thead> <tbody> <tr> <td>0</td><td>0</td><td>0</td></tr> <tr> <td>0</td><td>1</td><td>1</td></tr> <tr> <td>1</td><td>0</td><td>1</td></tr> <tr> <td>1</td><td>1</td><td>0</td></tr> </tbody> </table>            | b | a              | $a \oplus b$            | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 |

| b           | a                                | $a \oplus b$            |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 0           | 0                                | 0                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 0           | 1                                | 1                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 1           | 0                                | 1                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 1           | 1                                | 0                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| XNOR        | a ————— $\neq 1$ ————— o-y       | a ————— b ————— o-y     | $y = \overline{a \oplus b}$ | <table border="1"> <thead> <tr> <th>b</th><th>a</th><th><math>\overline{a \oplus b}</math></th></tr> </thead> <tbody> <tr> <td>0</td><td>0</td><td>1</td></tr> <tr> <td>0</td><td>1</td><td>0</td></tr> <tr> <td>1</td><td>0</td><td>0</td></tr> <tr> <td>1</td><td>1</td><td>1</td></tr> </tbody> </table> | b | a              | $\overline{a \oplus b}$ | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 |

| b           | a                                | $\overline{a \oplus b}$ |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 0           | 0                                | 1                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 0           | 1                                | 0                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 1           | 0                                | 0                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

| 1           | 1                                | 1                       |                             |                                                                                                                                                                                                                                                                                                             |   |                |                         |   |   |   |   |   |   |   |   |   |   |   |   |

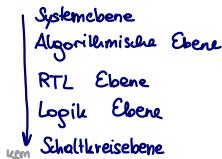

verschiedene Abstraktionsebenen

VO: Gatter, Schalter und ihre Optimierungen

CAC?

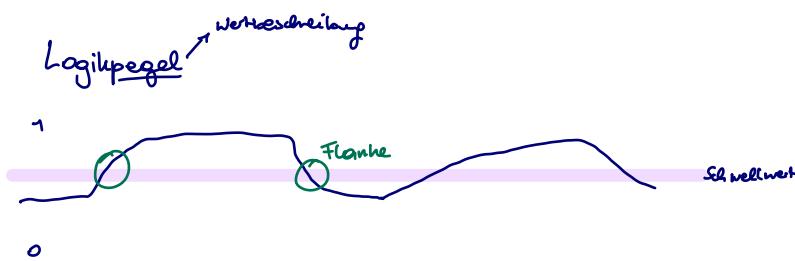

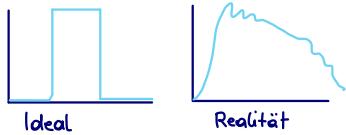

analog: alle Punkte /spannungspegel interessant

digital: Unterscheidung high / low

Spannungen: analoges Signal mit digitalen Logikpegeln

"Jetzt neu: digital"

↳ einfacher zu bedienen

↳ reproduzierbar (wieder)

↳ billiger (Trend)

↳ weniger Fehleranfälligkeit

Warum digital?

- Störfester (wenn Fehler dann markant)

- Speichern (analogsignal speichern ist schwieriger) Computer ohne Speiermöglichkeit

- Reproduzierbar

- Programmierbar

- Einfache Schaltung (Fertigung)

Zusammensetzung

... aber IRL ist Analog! → Digitale Behandlung erlaubt höheren Abstraktionsgrad

Temperatur, Spannungssignale ...

Flanke:

Zeitpunkt ↑

stiegend  $0 \rightarrow 1$

fallend  $1 \rightarrow 0$

Boolesche Algebra

⇒ AND

• const → Ausgang ist immer 0

• BUF nur 1 signal bearbeitet

• OR

• X-OR

• INV (kopiert)

• NAND (not and)

• NOR

• NINV = BUF

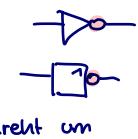

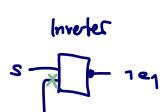

Inverter (NOT)

AND

OR

Maschieren

• Sperrt Einpäpl

• Dinge zusammenführen

INV(Eingang & Ausgang) → und zu oder

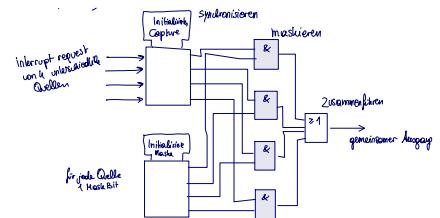

Interrupt - Mask

# Kombinatorische Logik

hängt nur von Eingang ab

Inverter (NOT)

AND

OR

NAND

NOR

XOR

XNOR

dreht um

$$1 \wedge 1 = 1$$

$$0 \vee 0 = 0$$

$$\neg(1 \wedge 1)$$

$$\neg(1 \vee 1)$$

alle Funktionen darstellbar

(wegen demorgan!)

Antivalenz

Äquivalenz

Bei passivem Inversion (Trojaner)

Addierer, Halbaddierer, Parity

Einung Ausung

Maskieren: AND 0  $\Rightarrow$  0 erzwingt Sperrung der Eingänge (nur 1)

OR 1  $\Rightarrow$  1 erzwingt Sperrung der Eingänge (nicht beide)

Einung Ausung

Zusammenführen: AND 0  $\Rightarrow$  0

OR 1  $\Rightarrow$  1

Wenn man die Eingänge und Ausgänge invertiert, wird  $\text{AND} \leftrightarrow \text{OR}$

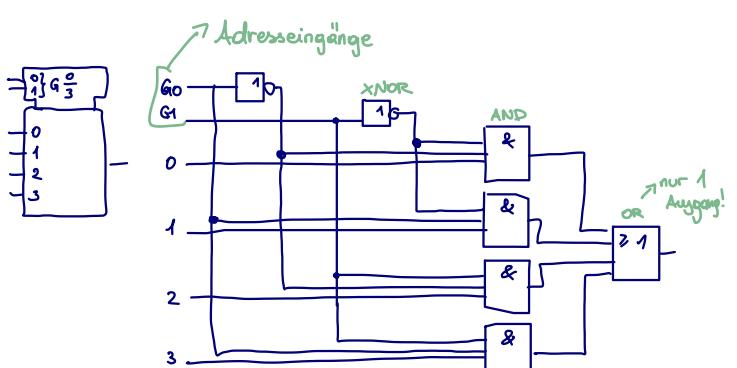

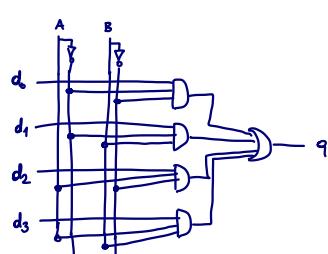

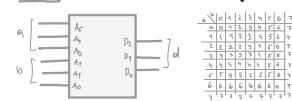

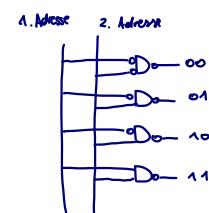

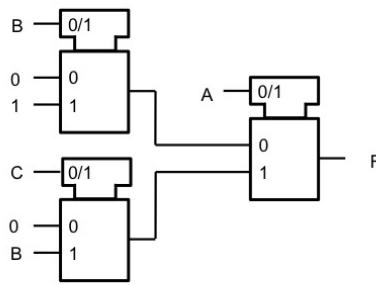

Multiplexer

Auswahl aus mehreren Signalen

$n$  Dateneingänge  $\rightarrow \log_2 n$  Adresseingänge

Threshold Gate

bei  $>k$  Eingängen geht Schaltung auf 1.

Parity

XOR even parity

XNOR odd parity

## Anwendung:

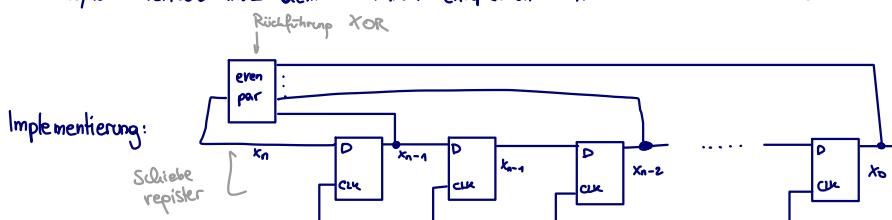

Register, Schieberegister, Serielle Paralleler Konverter, CRC Generator, FSM ...

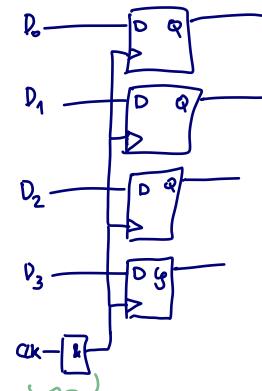

# Sequentielle Logik

hängt von Eingang und Zustand ab

enthält explizite Speicherelemente / speichert durch Rückkopplung  $s_j \Rightarrow$  hat inneren Zustand

(wird bestätigt und so gehalten)

Zustand durch Vergangenheit bestimmt (Fernsehlaufstärke)

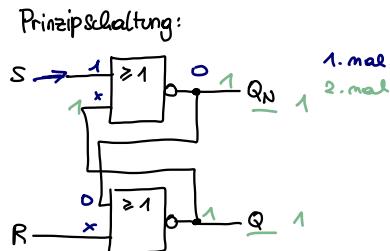

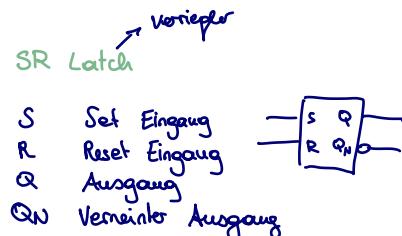

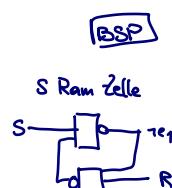

Setzen:  $S \rightarrow Q = 1$

Löschen:  $R \rightarrow Q = 0$

Halten:  $S, R$  inaktiv  $\rightarrow Q$  hält

$Q = Q_N$

weil  $S, R$  gleichzeitig

aktiv sind

Timing mit

"Kavern"

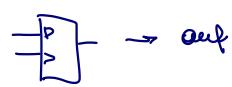

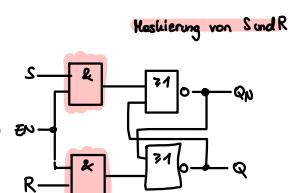

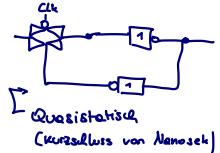

SR Latch mit Enable

wie SR Latch; S, R inaktiv wenn enable = 0

Enable steuert S, R

$EN = 1 \rightarrow S$

Wenn bei Enable nichts geschallen

ist, geht das Ding nicht

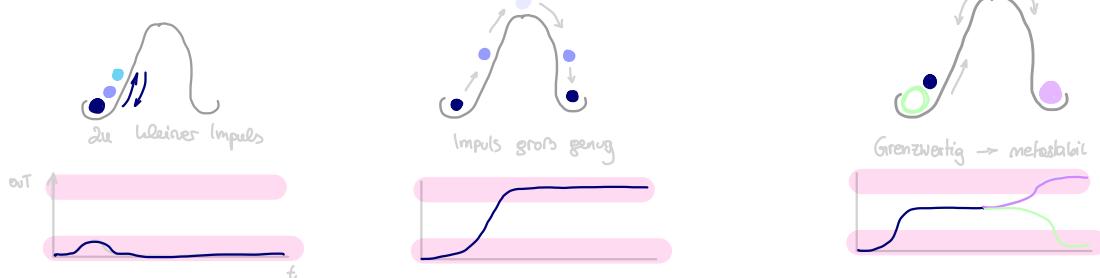

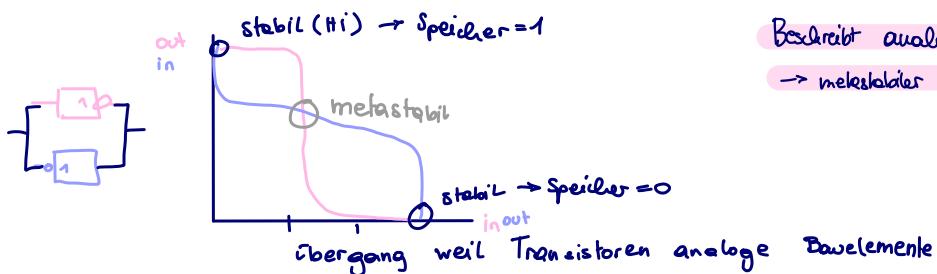

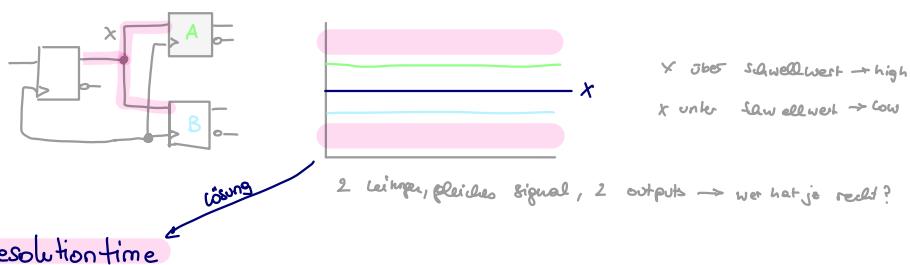

Problem: Es kann "Metastabilität" auftreten!

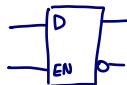

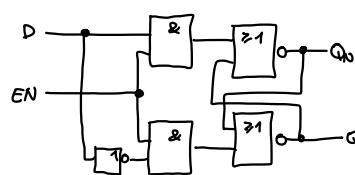

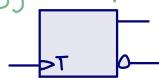

## D Latch

Eingang für D ... Data

Set/Reset gleichzeitig nicht mehr möglich

( $Q_N = \neg Q$ )

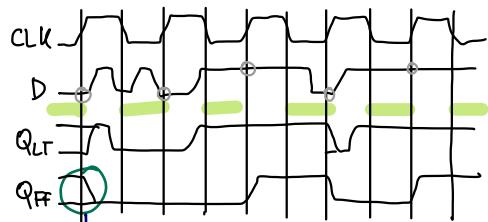

## Latch

vs

## Flipflop

Periode bewirkt Zustandsänderung

bei aktiver Taktflanke

kein Taktsignal

synchron: mit Taktflanke parallel nur

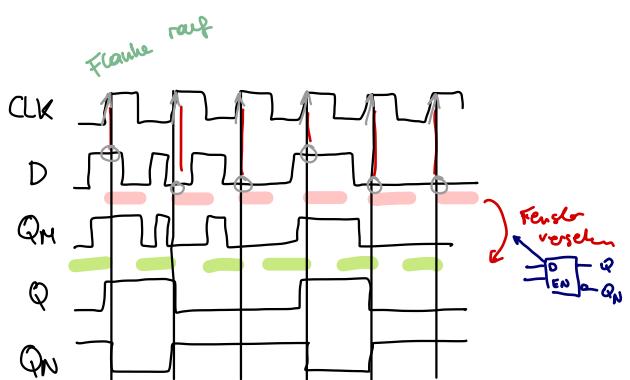

## D ~ Flip Flop

CLK ist wichtigstes Element

$D \rightarrow Q_N \rightarrow Q$

ENABLE ist nicht immer Aktiv

nur hold / übernehmen

PR: Ausgang von Flip flop aufgrund von Flanken bestimmen

## Latch

CLK low  $\rightarrow$  undurchlässig

CLK high  $\rightarrow$  durchlässig

## D-Flipflop

steigende Taktflanke

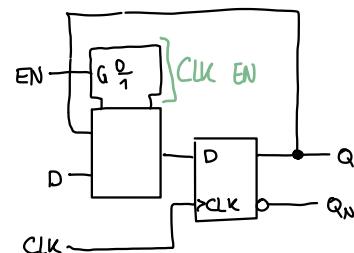

## Clock Enable

$\rightarrow$  steuert Übernahme von D nach Q

$\rightarrow$  Es werden nicht immer alle Funktionseinheiten benötigt

Preset erzwingt  $Q = 1$

Clear erzwingt  $Q = 0$

for initialisierung wichtig!

(Durch spez Gitter)

| D | CLK | PRE | CLR | Q      | Q_N      |

|---|-----|-----|-----|--------|----------|

| 0 | ↑   | 1   | 1   | 0      | 1        |

| 1 | ↑   | 1   | 1   | 1      | 0        |

| 0 | 1   | 1   | 1   | Letz.Q | Letz.Q_N |

| 1 | 1   | 1   | 1   | Letz.Q | Letz.Q_N |

| 0 | 1   | 0   | 1   | 0      | 1        |

| 1 | 0   | 0   | 1   | 0      | 1        |

preset

clear

(Ohne Takt ist alles initialisiert!)

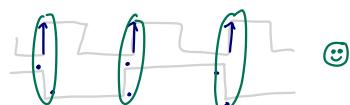

## Toggle Flip Flop

mit jeder steigenden Flanke ändert sich der Ausgang (Taktänderung)

toggle: bei aktiver Flanke wird Ausgang invertiert

$\searrow$  Umschalter

hold: Q hält Zustand bis zur nächsten aktiven Flanke

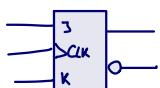

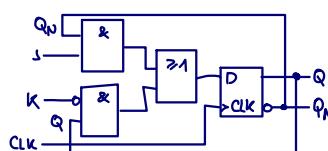

## JK Flip Flop (jump and kill)

$\rightarrow$  ähnlich Mux, Toggle FF

$\rightarrow$  J - Set Eingang

K - Clear Eingang

$J = 1$  setzt

$K = 1$  löscht  $J \wedge K = 1 \rightarrow$  toggle (definiert, nicht instabil)

Some random shift ... ?

Takt ist verschoben  $\rightarrow$  timing durch einander für Register schlecht!

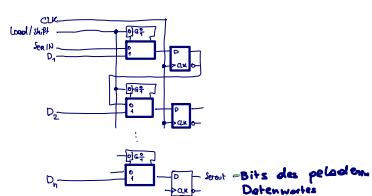

## Seriell - parziell Konverter

$\rightarrow$  Kette von DFF als Schieberegister

$\rightarrow$  Aktive Taktflanke: 0 des vorherigen FF als D übernommen

$\rightarrow$  LOAD  $\xrightarrow{\text{Hinweis}}$  Datenwort synchron übernommen

$\rightarrow$  Hinweis legt Q als D an

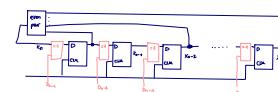

## Linear Feedback Shift Register

$\rightarrow$  für Polynomdivision

$\rightarrow$  arbeitet zyklisch

$\rightarrow$  full length LFSR hängt von Auszäpfen (Polynom) ab

$\rightarrow$  hat Eigenschaften einer Zfolge

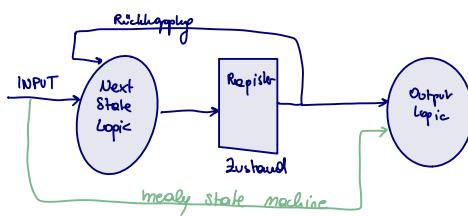

# Finite State Machines

synchrone Zustandswechsel

Moore: Ausgangssignal durch Zustand

Mealy: Ausgangssignal durch Eingang und Zustand

Bsp: Ampel braucht Kombinatorische Logik

nicht nur 0/1

Zustand: 3 Register  $\rightarrow$  8 Zustände

PR: Blöcke für Zustandsdiagramm / Beschreiben

# Boolsche Algebra

Identität, Nullelement, Indempotenz, Komplement, Involution, Kommutativität, Assoziativität, Überdeckung, Kombination, Distributivität

$$\text{De Morgan} \quad \neg F(x_1, \dots, \wedge, v) = F(\neg x_1, \dots, v, \wedge)$$

Shannon: 1 Variable loswerden  $\rightarrow$  Variable auf 1 setzen (HDX maskiert)

$$(a \wedge b) \vee (b \wedge c) = (\underbrace{b \wedge (a \wedge 1)}_{b=1} \vee (1 \wedge c)) \vee (\underbrace{1 \wedge (a \wedge 0)}_{b=0} \vee (0 \wedge c))$$

Minterm: UND von Variablen  $\wedge \neg$  (Variable  $\leq 1$ )

Maxterm: OR  $\vee \neg$  (Variable  $\leq 1!$ )

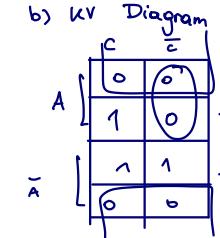

KV Diagramm

KNF: Nuller DNF auslesen  $\rightarrow$  Invertieren

DNF: 1 bei OR

PR KNF, DNF angeben

KNF: 0 bei AND

# ASIC Fertigung

## MOTIVATION:

Integrated Circuit; schneller, kleiner, leistungsfähiger, billiger, störsicherer

Technology Roadmap ITRS → (Moores Law: Halbleiterindustrie wächst sehr schnell an!)

1971 - 2000 Trans ~ 2008  $731 \cdot 10^6$  Trans

Rechner werden schneller durch Microchips, Speicher wächst nicht so schnell ⇒ Cache

5 GHz war/ist die Obergrenze

## Digitale Logik

Isolierung: Silizium Dioxid  $\text{SiO}_2$  (0 Kelvin)

Schaltbare Verbindungen: Dotiertes Silizium (Silizium & Germanium)

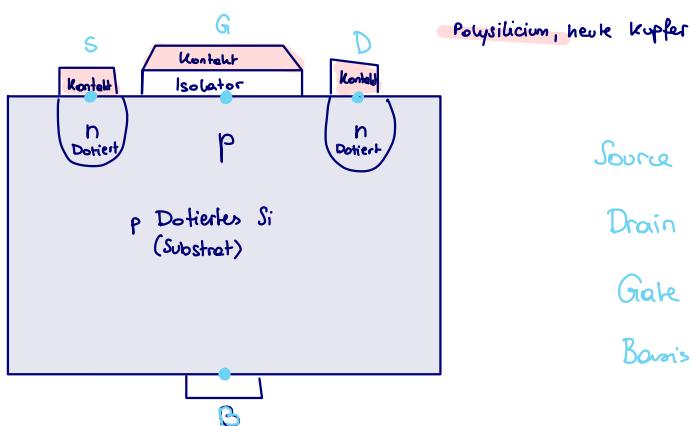

Feste Verbindungen: früher PolySi, heute Kupfer, Aluminium

### Dotieren:

• n-Dotierung: Elektronenüberschuss (Elektronendonoratoren) Arsen, Antimon

• p-Dotierung: zu wenig  $e^-$  (Elektronenakzeptoren) Bor, Indium

→ es gibt auch Dotierungsstärke!, Legierung ist eine Art Dotierung

pn Übergang: keine Leitung aber mit elektrischen Feld angeleitet führt Strom zw np

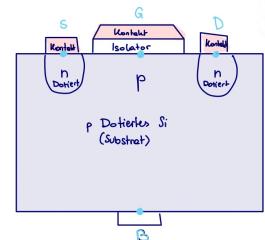

## Metall Oxid Semiconductor Transistor

Source

Drain

Gate

Basis

4 mögliche Beschaltungsarten

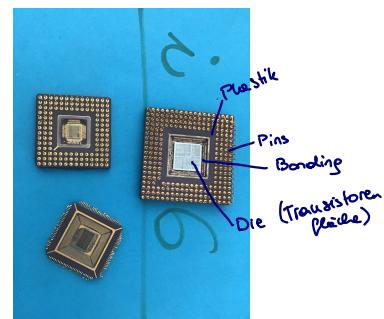

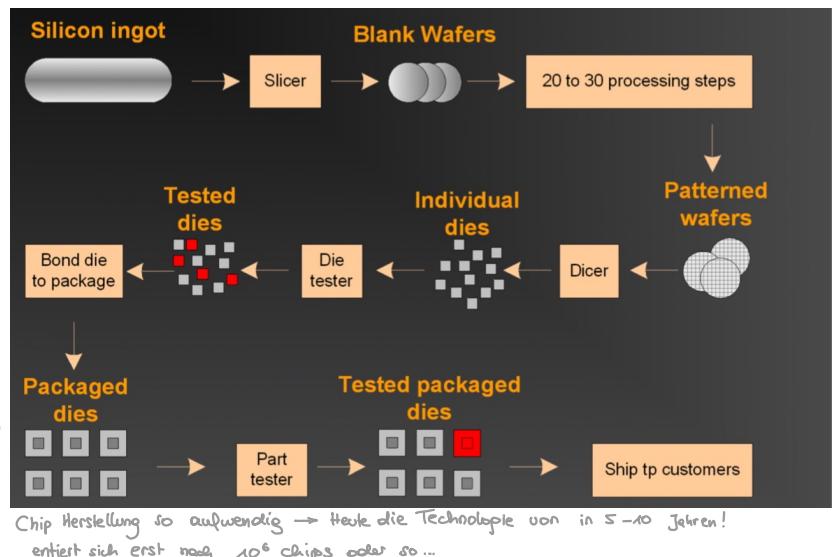

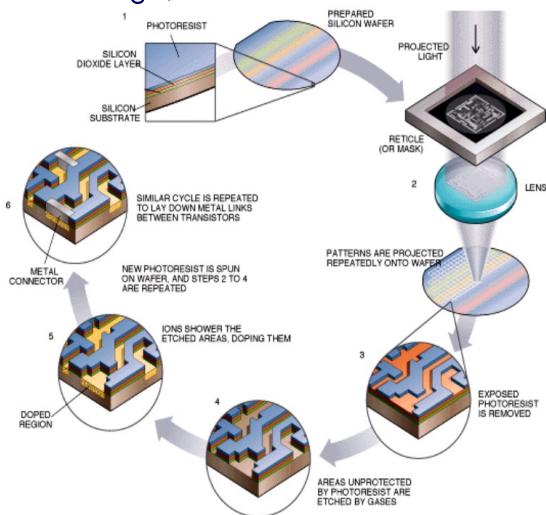

# Chip Fertigung

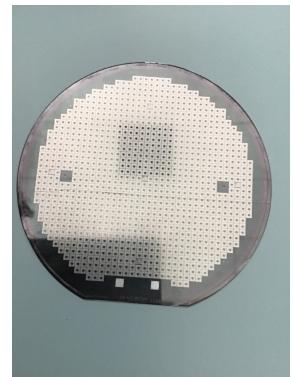

- Sand ~99% Reinheit durch Tiegelziehen (rund!)

- Runterschneiden → es entstehen "Waffer"

- Muster hineinätzen mittels Photolithographie

- Zerschneiden (je größer desto weniger Verschnitt)

- testen (kaputte markieren) mit Prüfpunkten

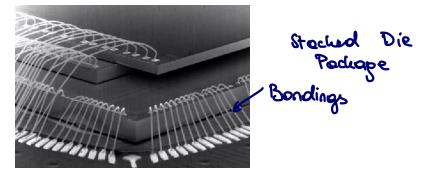

- Packaging: Gehäuse mit Anschlägen (Flip Chip → kein Package)

- Bonding: Drehk mit Kontakten auf Packaging pins

## Photolithographie - Prozess:

Wozu dienen die Masken?

Wie wird Licht richtig fokussiert?

Laserstrahl Elektronenstrahl

Wafer (waffer)

## Feature size 1

Maß für Technologiefortschritt

Kanallänge  $2L \rightarrow 0.014\mu m$  (haar  $100\mu m$ )

feature size wächst → Transistor kleiner, schneller, leistungsfähiger

## Prozessparameter:

Kanal Länge  $2L$ , Breite  $3L$

Oxid Dicke  $T_{ox} < 1nm$

Diffusionsbereich Länge  $3L$

Aber: Je geringer die Spannung  $U$ , desto weiter muss man Frequenz senken!

Metallverbindungen Breite  $3L$ , Abstand  $3L$

Subthreshold

Größe der Dies bleibt konstant

## Interconnect:

Verbinden der Leiterbahnen (früher Löcher, heute Isolation & Vias)

# Moderne Formen von Chips

**SOC** - System on a Chip

Früher: Für jede Funktion ein anderer Chip

Heute: IP module, Schaltbilder, Codestücke auf 1

**SOC-Pro:** Kosten, Performance, Größe

**SOC-Contra:** Komplexität (mehr Prozessschritte), nicht alles integrierbar, suboptimale Technologie

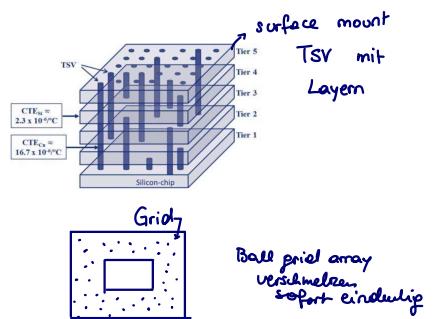

**MCM** - Multi Chip Modul: Mehrere Dies planar → kleiner, billiger

**mems**: Hebelarm aus Silizium auf Chip (Widerstand für Beschleunigungssensoren)

**Stacked Die Package**: mehrere Dies gestapelt, Entfernung Thermisch

↳ Through Silicon Via (TSV)

## Grenzen der Technologie:

**Miniaturisierung**: Elektron ist kleinstes Ladungssymbol → Quantenphysik

Materialien:

**Isolatorproblem**: nicht so belastbar (zu hohe Feldstärke 😕)

$1V/m \rightarrow 1nV/m$

**Tunnelströme**: steigen exp(x) bei kurzem Kanal (isoliert nicht 100%)

Gate-Oxid

$1GV/m \rightarrow 1V/nm$

Quantenmechanik

Wellenlänge von Licht, Molekülgröße Photolack, thermische Leitfähigkeit begrenzt, Kosten

Wafer Dotierung stört im Silizium → Silizium an Isolator

**Transistor der Zukunft**: strained silicon, Gate aus Metall, High k, SOI, 3D → Gate beidseitig

**SOI**: Isolator als Träger

**Tinfet**: 3 Kanäle

Alternativen:

Quantencomputer (ja)

Nanotubes (vielleicht)

Molekular Elektronik (eher nicht)

**Geschwindigkeit**: Wellenausbreitung (natur)

Ladungsvorgänge (unvermeidbar) ↗ Verzögerung

Bewegung Ladungsträger (unvermeidbar)

Mit welcher Geschwindigkeit breite sich eine Welle aus?

**Komplexität**: Aufwand, Design Crisis, Ausbaute, Anzahl an Pins, Leistungsverbrauch

**Multiprozessorchips**: parallel programming

# Aufbau logischer Gatter

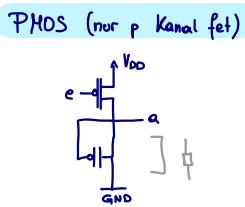

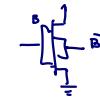

n Kanal Enhancement MOSFet

## Feldeffekttransistor

3 Anschlüsse: Gate, Drain, Source

Funktioniert wie ein Schalter (eigentlich analogen Bauelement)

Spannung am Gate und Source → sperrt, kein Stromfluss

Schwellspannung  $U_{th} > 100 \mu V$

Spannung am Gate, Source, Drain → Stromfluss

(Fast) kein Strom für Energiefluss nötig → energieeffizient

Bipolartransistor hat immer Basisstrom für Funktion

Was passiert im Fet:

p  $\rightarrow$  3 1 zu wenig

n  $\rightarrow$  5 1 überschuss

elektrische Kraft

"Gitterkraft"

$U_{GS}$  bewirkt elektrostatisch

$U_{GS} = U_{th}$  p Si lädt auf  $\rightarrow$  Elektronen passieren

Potentialunterschied von n und p  $\rightarrow$  Gatter sind schneller bei hohen Temperaturen

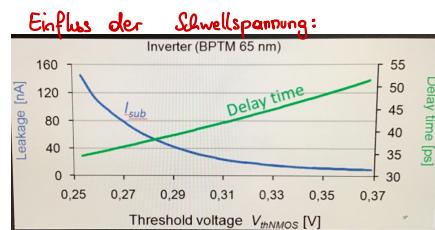

## Eingangskennlinie

Schwellspannung über Dotierung einstellbar

Leakage current (Strom der Fließt obwohl es aus ist)

Je höher Schwellsp desto langsamer Trans.

Ausgangsstrom  $I_{DSS}$ : Maximaler Strom den fet bei "Schalter geschlossen" führen kann; Reproduzierbar über Kanallänge L: Kanalbreite W  $\rightarrow$  Formfaktor

Formfaktor:  $\frac{W}{L}$   $W > L$  guter Leiter, großes W, größerer Transistor (Treiberstärke verstetigbar)

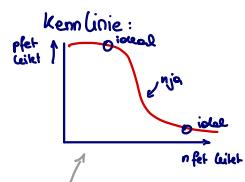

p Kanal fet um Faktor 2 schlechter als n Kanal fet

n Kanal fet

|            |                     |                   |   |

|------------|---------------------|-------------------|---|

| logisch 1: | schwach geschlossen | $1 - \frac{1}{W}$ | 1 |

| logisch 0: | stark offen         | $0 - \frac{1}{W}$ | 1 |

p Kanal fet

|           |             |        |

|-----------|-------------|--------|

| logisch 1 | offen       | strong |

| logisch 0 | geschlossen | weak   |

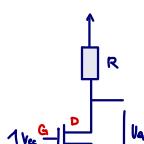

## Source-Schaltung

ist besser als

Spannung wird invertiert

Strong 0

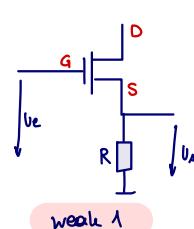

## Sourcefolger

weak 1

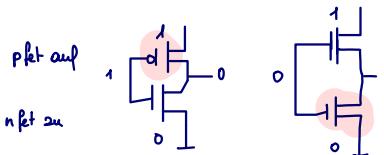

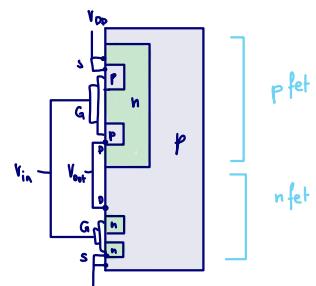

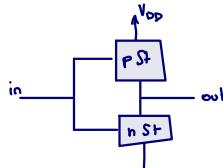

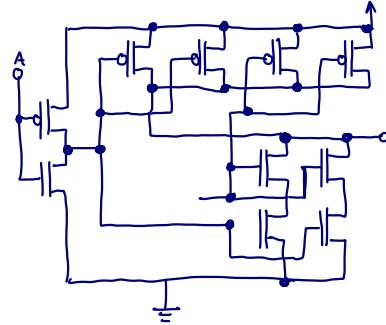

## CMOS Logik

Kombi von pKanal & nKanal

↳ beide logischen Pegel aktiv

0 1 1 gleichzeitig

Zueinander komplementär

## Kombinatorische Logizellen

### Cmos Inverter (2 Transistoren)

Technologie:

B-Anschluss "ganz unten"

pFet in nFet integriert (Gates breiter)

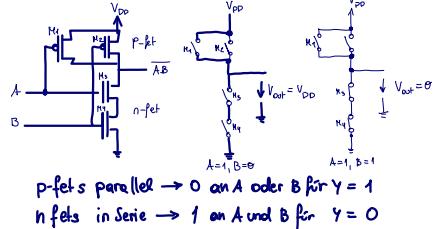

### NAND

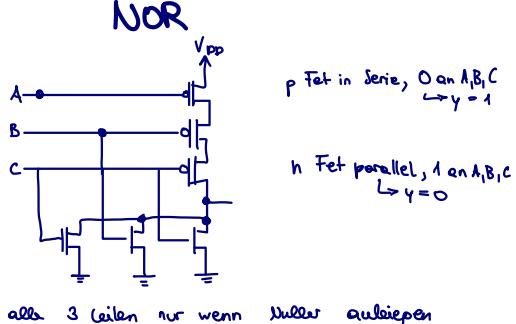

### NOR

### Buffer

2 Inverter, sonst nur schwache Wirkung

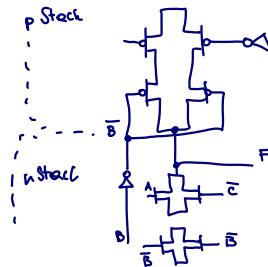

p Stack: aus pFet Aus: 1

AND durch Serie

OR durch Parallel

Invertierter Eingang

$$F(\neg x_1, \dots, x_n, v, \wedge)$$

n Stack: aus nFet Aus: 0

AND durch Serienschaltung

OR durch Parallelschaltung

Invertierter Eingang

hier AND/OR mit Inversion am Schluss

$$\neg F(x_1, \dots, x_n, \wedge, v)$$

### Open drain

#### Tristate:

P ein  $\rightarrow \text{V}_{\text{DD}}$  mit GND  $\rightarrow$  geht nix (Kurzschluss)

aus aus  $\rightarrow$  "Tristate", meistens Floating Pin (0/1/nix)

mehrere Ausgänge zum Schalten, nur einer aktiv

Wie funktioniert Tristate?

kein p Stack (Ausgang 0 durch nStack erzwungen)

ist ein "And" Schaltung, Ausgang 1 durch  $R \rightarrow$  Spannung bei groben Stößen

RC braucht länger als Gate Delay

Was ist Unterschied zu Tristate / Open drain?

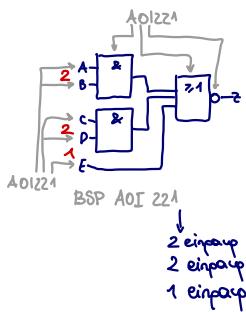

## AOI:

- ↳ Gleichung aufstellen       $n \text{ Stack} = \text{Strong } 0$

- 2) Inversion zu Eingängen  $\rightarrow p \text{ Stack} = \text{Strong } 1$

- 3) AND  $\rightarrow$  Serie

OR  $\rightarrow$  Parallel

N Stack aus AOI / OAI bauen

Inverter dazuschalten ( $\rightarrow$  was passiert...)

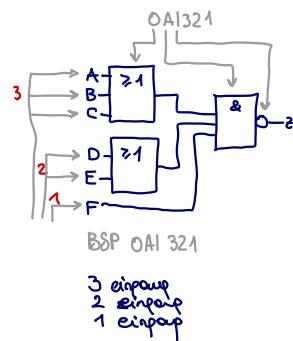

## OAI:

$n$  Stack bauen  $\rightarrow$  für  $p$  Stack:  $n$  Stack komplett invertieren, Serie parallel schalten

### BSP Alarmanlage

$p$  Stack zeichnen,  $n$  Stack zeichnen, verknüpfen

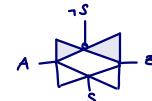

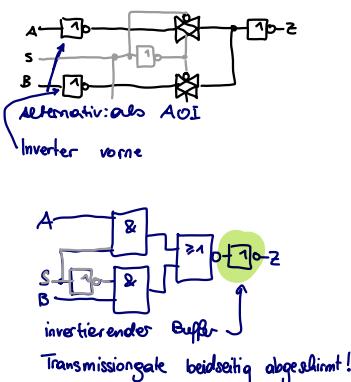

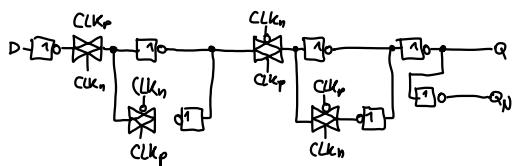

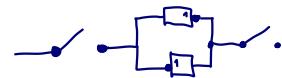

### Transmission Gate

- $p$  Kanal / nkanal fet parallel  $\Rightarrow$  INVERTER

- Schaltbare Verbindung zw 2 Leitungen

- bei A unbekannt ob high / low

- Buffer: nicht schaltbar

- $\Rightarrow$  Transmission Gate ist schaltbar

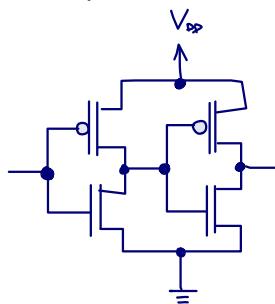

### MUX mit Transmission Gate

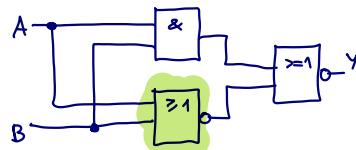

### XOR

als Transmissiongate, 3 Eingänge, einer als schaltbarer Inverter (ungünstig)  $\rightarrow$  2 Transistoren in Serie :

Lösung: XOR als AOI - NOR Gatter davor

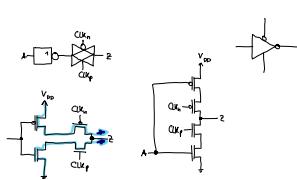

### Getakteter Inverter

- wie TG

- Signal invertiert, Takt = Steuersignal

- Inverter + Schalter  $\rightarrow$  getakteter Inverter

- einlaufen benötigt Zeit: hold & set

- Buffer am Ende um Bitflip zu verhindern

Bei Latch & Flip flop

### Gatereinheit GE

2 Transistoren  $\rightarrow$  0,5 GE

4 Transistoren  $\rightarrow$  1 GE

**Latches** Transparent, Hold (Setup Time & Hold Time)

Decision Window: Wenn Schalter betätigt, dann fix (bei Flanke metastabil!)

**BSP** Speicher kann immer metastabil werden → Grenze muss immer verschwinden

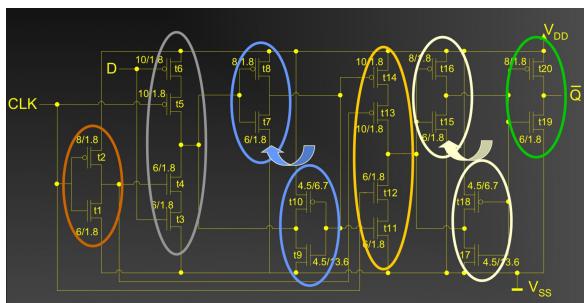

Aufwand:  $7 \text{ Inv} + 2 \text{ TG} = 18 \text{ Trans} \Rightarrow 9,5 \text{ GE}$

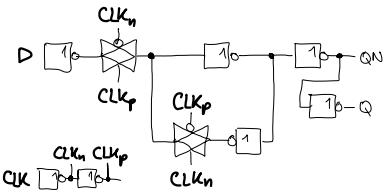

**D Flip Flop Data, Clock**

2 latches in Master - Slave

Theoretischer Aufbau mit TG

Theoretischer Aufbau mit TG

Speicher kann immer metastabil werden

→ Grenze muss immer verschwinden

4,5 / 13,5

Wid klein | L groß

8 / 1,8 breiter weil p-Kanal fet (wg Löchen)

6 / 1,8

**SR Latch:** Metastabilität (Kurzer Plus, gleichzeitige Aktivierung)

Register Array aus Flip Flops

Speicher: FlipFlop, SRAM, DRAM ( $D \rightarrow S \rightarrow D$ )

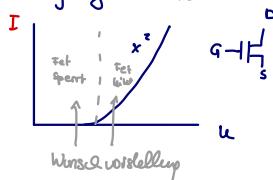

Fet als Widerstand

⇒ Ausgangs I abhängig von Ausgangs U → saturation reach

⇒ Formfaktor W/L

**TTL**

Transistor - Transistor - Logic

Durch Bipolartransistoren

Stromverstärkung von 50 oder 100 fach

74xx früher Bipolar

Bipolare Logikfamilien

ECL

Emitter Coupled Logic

Schnelles Umschalten

nicht kompatibel zu CMOS/TTL

Glasfaser

→ Umschalten von Stromplatten

Bi CMOS Logik

hohe Ströme (Motoren etc.)

**BSP** Autobeschleifer

Kontaktfehler Tastrelais

↓

extern löken, Treiber im Baustein

# Design Flow eines ASIC

VHDL

## Y Diagramm (Denkhilfe)

Sichtweisen auf Schaltung: Verhalten, Struktur, Geometrie

Konvergenz: Design Flow

## Designschritte beschreiben Prozessübergang

- Specs - Exakte Formulierung des Produktes (zB Synchronisationszeitpunkt, viele non functional Parameter)

Validation

Design Entry - Specs in Computer / Compiler übersetzen / Basis / Dokumentation → Möglichkeiten

Behavioural Simulation

Compilation - verhaltensbasierte in strukturelle Darstellung (Analyse, Elaboration, Transformation, Minimierung, Timing Analyse)

Functional Simulation

Technology Mapping - Target Library → Zieltechnologie festlegen (Generische Gatter auf Logikelemente)

Pre Layout Gate-level Simulation

Partitioning und Placement - Designaufteilung (wenige Verbindungen, Größe, Speed, Verlustleistung) & Verteilung Logikelemente / Platzierung & Routing

Post layout

Manufactory & Download

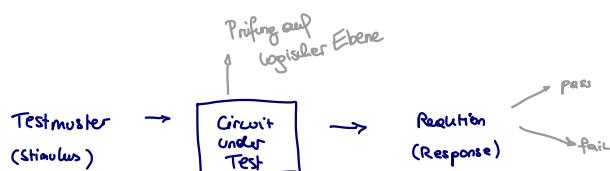

Test

Chip Complete

| Ebene                  | Verhalten                                                             | Struktur                                                       | Geometrie                            |

|------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------|

| System                 | Inputs : Keyboard<br>Output: Display<br>Funktion: Umrechnung,...      | Speicher ↔ CPU ↔ IO<br>Control                                 | Q1 GND PLCC84<br>VDD IO DO DIO A7 A5 |

| Algorithmisch          | while input<br>Read „Schilling“<br>Calculate Euro<br>Display „Euro“   | Speicher<br>μP<br>IO-Ctrl<br>RS232 Interface<br>PS/2 Interface | μP PS/2<br>IO-Ctrl RS232             |

| Registertransfer (RTL) | case A<br>when '1' then<br>nextB <= C;<br>nextstate <= idle;          | RAM → Register → ALU<br>Counter                                | REG ALU Counter                      |

| Logik                  | D = NOT E<br>C = (D OR B) AND A                                       | E → NOT → AND2 → C<br>B → OR2 → C                              | INV1 AND2 x3<br>OR2                  |

| Schaltkreis            | $\frac{dU}{dt} = R \frac{dI}{dt} + \frac{1}{C} + L \frac{d^2I}{dt^2}$ | [Circuit diagram]                                              | [Circuit diagram]                    |

# Detaillierte Auflistung des Design Flows

FBGA - Ball Grid Array

BUS - Ein Weg viele Daten

## ① Specs

### ② Design Hierarchie:

Volladdierer aus 2 Halbaddierern

Vectorized instance (Parallelshaltung  $\rightarrow$  BUS)

Schematic Entry  $\hookrightarrow 1:4 : 4$  Bit Latice

BCD (Binary Coded Decimal) 0001 - 0111  $\rightarrow$  0 - 7

### ③ SW vs HW

Hochsprache vs VHDL  $\rightarrow$  alle in Assembler

Compiler  $\nearrow$  SW: Zeifreie Beschreibung, Funktion ohne Timing

$\searrow$  HW: Timing notwendig!

"file open" / "wait" in HW nicht implementierbar

$\rightarrow$  VHDL (nur für HW konzipiert)

$\rightarrow$  Verilog - Simulationsprolgle

$\rightarrow$  C

### ④ Optimierung: Kosten & Nutzen

Synthese: Optimiervriterium (speed  $\times$  area  $\times$  effort) OK

Raudbedingungen (Timing, Power, Sperren) einhalten RB

### ⑤ Strategien für Partitioning:

Konstruktiv - Zamsköpfchen

Iterativ - Sackauftilung, 2 Elemente vertauschen  $\rightarrow$  in Richtung optimum

Simulated Annealing: Schmetzgel  $\rightarrow$  je kühler umso weniger will ich Versaldeierung.

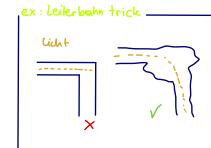

### ⑥ Placement

Floorplanning

Placement

Grundproblem: Leitungen optimieren bevor sie belegt wurde

$\hookrightarrow$  Lösung: Heuristik

Delay: Gitter, Leitungen

massives Problem zw Gate Delay & Interconnect Delay

### ⑦ Routing: Verbindungsherstellung

Interconnect - half pitch zeitversatz

CLK: minimaler Delay / Skew (Treiber & Buffer zum Ausgleichen)

Stromversorgung: Strom  $\frac{1mA}{mm^2}$  maximal, sonst Elektromigration  $\rightarrow$  chip stirbt

$\hookrightarrow$  Gewollige Stromdichte!!! 0,5 mA zu 230V!

Wir haben: Positionen, Library, Routen ...

Simulatoren: Kapazitive Kopplungen, ...

Was versteht man unter Back-Annotation?

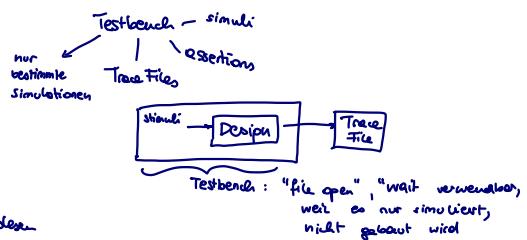

## Verifikationsschritte

Validation - "Do I built the thing right or do I build the right thing?

Simulation - "If SW Developer had to build planes" Flugzeug

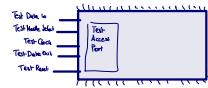

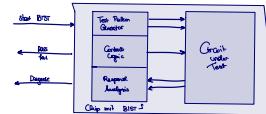

ASIC - sehr nur Pins außen! (Zugänglichkeit)

Fertigungskosten, Dauer, Prototypen

Testbench: Hardwarecodierung von TR in größere Beschreibung → Signale durch → ändern

ist keine Garantie!

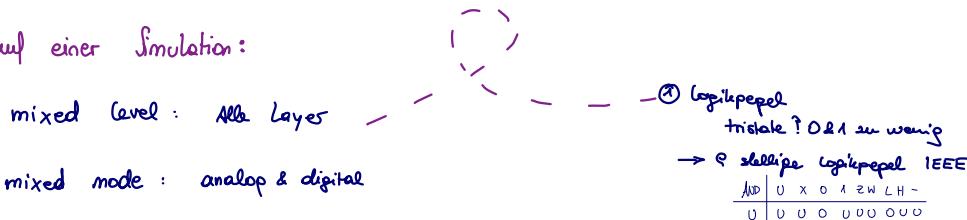

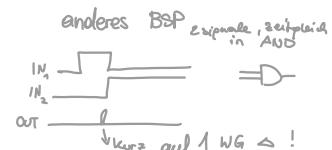

Arten von Simulationen (auf allen Ebenen)

Behavioral Simulation: Testbench, specs, what's happening ...

Des → Beh. → Syn

Functional Simulation: Code richtig interpretiert, Timing!

Syn → Fun → Tech

Pre Layout Gate Level Simulation: Latch, FlipFlops

Post Layout ... Simulation: Timing Wichtigster Schritt

Simulation notwendig, aber nicht

auf allen Ebenen, auf jeder

Fall Post Layout Sim!

Vielen Sims gut zum genauen Fehlerorten.

→ Fehlermaskierung fällt auf!

Ablauf einer Simulation:

sign-off: Vorlagen von mixed level/mode als "Abkommen"

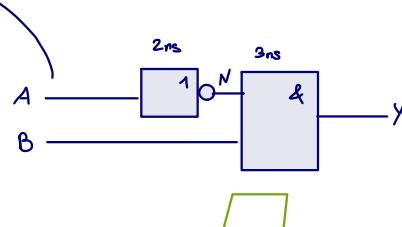

BSP | Annahme: vorher stabil

|         |                                                | event | A | B | N | Y |

|---------|------------------------------------------------|-------|---|---|---|---|

| 0       | 0-(vor Use!)                                   | init  | 1 | 0 | 0 | 0 |

| 0       | 0+(restetig, findet periodisch, ist empfohlen) | A↑    | 0 | 0 | 0 | 0 |

| 1       |                                                | B↑    | 0 | 1 | 0 | 0 |

| 2       |                                                | A↑    | 1 | 1 | 0 | 0 |

| 2+△     |                                                | N↑    | 1 | 1 | 1 | 0 |

| 3       |                                                | B↓    | 1 | 0 | 1 | 0 |

| 3+△     |                                                | y↓    | 1 | 0 | 0 | 0 |

| 2+2ns=4 |                                                | N↓    | 1 | 0 | 0 | 0 |

| 2+3ns=5 |                                                | Y↓    | 1 | 0 | 0 | 1 |

| 3+3ns=6 |                                                | Y↓    | 1 | 0 | 0 | 0 |

Signal Resolution Table für ein OR Gatter

Abbruchbedingung angeben

△ ... Virtuell

Schaltung neigt zu Glitches: (Problem von 3 und 3+△) bei puls Schaltung eigentlich wurst.

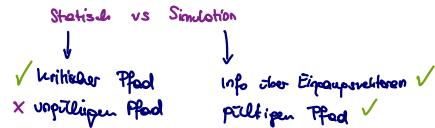

## Statische Timinganalyse

Prototyp: notwendig, nicht hinreichend wegen Cornercases

wie lange muss Taktperiode sein, dass sich "logikwolke" ausdeilt?  $\rightarrow$  Backtracking (langsamer)

$$\frac{1}{f_{cell,max}} = \max(t_{delay,DAT\downarrow,ij}) + t_{su} \dots - \min(t_{delay,D,CLK,i})$$

[ nur lagsamstes und rekt das als Timing]

Library Databook

charakterisiert verfügbare Basiszellen, definiert Timing (Variationen durch Derating-Faktoren)

$$t_{delay} = t_{int} + C_{load} \cdot t_{ext}$$

Hohe Temperatur und niedrige Versorgung verlangsamt den Chip

W-L einstellen: W-L größer  $\rightarrow$  Kapazität steigt

$$Max \cdot t_{delay} = t_{int} + C_{load} \cdot t_{ext}$$

Fixes Delay & Lastabhängiges Delay

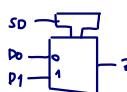

BSP: D0↓ schneller, aber starker Lastabhängig

| from input | $t_{output}$ | intrinsic | extrinsic (ns/pF) |

|------------|--------------|-----------|-------------------|

| D0↓        | 2↓           | 1.42      | 2.10              |

| D0↑        | 2↑           | 1.23      | 3.66              |

| D1↓        | 2↓           | 1.42      | 2.10              |

| D1↑        | 2↑           | 1.23      | 3.66              |

| SD↓/↑      | 2↓           | 1.42      | 2.10              |

| SD↓/↑      | 2↑           | 1.08      | 3.66              |

### Derating Factors

Kühl: schneller Warm: langsam

wenig Spannung: langsam viel Spannung: schnell

Corner Cases: beliebt  $\rightarrow$  Wahrscheinlichkeitsverteilung

|            | 4,5V | 4,75V | 5V   | 5,25V | 5,5V |

|------------|------|-------|------|-------|------|

| -40°       | 0.77 | 0.73  | 0.68 | 0.64  | 0.61 |

| 0          | 1    | 0.93  | 0.87 | 0.82  | 0.78 |

| 25°        | 1.14 | 1.07  | 1    | 0.94  | 0.9  |

| 85°        | 1.5  | 1.4   | 1.3  | 1.26  | 1.2  |

| 100°       | 1.6  | 1.48  | 1.41 | 1.34  | 1.28 |

| 125°       | 1.76 | 1.65  | 1.56 | 1.44  | 1.41 |

| Worst Case |      |       |      |       |      |

WORST Case: 1.76 (fast doppeltes delay!)

## Formale Verifikation:

vollständige Überprüfung  $\rightarrow$  Darstellung des Designs als Modell (gibt Deadlock? wird Zustand A erreicht?)

modell Model Checking  $\rightarrow$  Überprüfen von Bedingungen/Eigenschaften

vollautomatisches, kommerzielle Tools, pass/fail, Nachträgliche Prüfung

& Equivalence Checking  $\rightarrow$  Übereinstimmung von zwei Modellen

formal Formel: manuell, mathematisch, Parameter als Variable, Design Entklemmungen

## Design Tools

unab

hängig } Design Entry, Logic Compiler,

Simulation, PPR

Laufzeit erst wenn es fertig ist  $\rightarrow$  Heuristiken zur Berechnung verwenden

# Speichertechnologien

Speicher: strukturierte Anordnung von Informationsträgern

Speicher: strukturierte Anordnung von Informationsträgern

Funktionsprinzip:

Analoger Speicher: Magnetisiert, Lichten bei alten Kinofilmen

Digitaler Speicher: 1 bit = 1 Informationsträger mit 2 unterscheidbaren

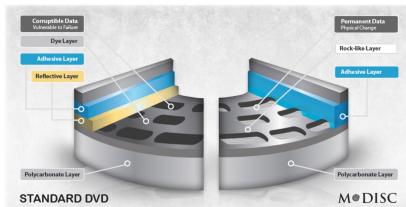

**BSP** Optischer Speicher

Ladungszuständen

Spannungsregeln

Magnetisierungsrichtungen Festplatten

Topologien (Spiralvorgang)

optischen Reflexionseigenschaft BluRay

Eigenschaften

im Betrieb beschreiben: Reg File, Read/Write Memory

im Betrieb nicht beschreiben: Read only Memory (ROM) → non volatile (nicht flüssig), schreibgeschützt

nur schreiben, nicht lesen: Write only ROM, Log File (Blackbox)

Auslesen von Speicherinhalten im Betrieb immer möglich!

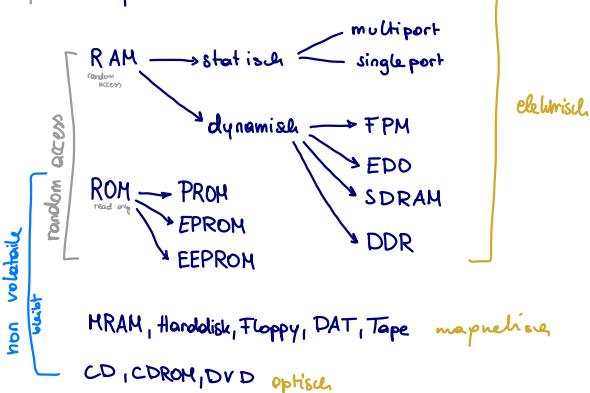

Speicherzugriff:

Random Access: Wahlfrei

zu jedem Zeitpunkt zugreifen mittels Adresse

FILO: First in Last out (keine Adressen notwendig!)  $a_1, b_1, c_1, d_1 \rightarrow [d \boxed{c} \boxed{b} \boxed{a}] \rightarrow d, c, b, a$

FIFO: First in First out (Adresse nötig, mehr Rechenaufwand)  $a_1, b_1, c_1, d_1 \rightarrow [a \boxed{c} \boxed{b} \boxed{d}] \rightarrow a, b, c, d$

NVM: Non volatile Memory (Inhalt bleibt erhalten) ROM, Harddisk, CDROM

VM: Volatile Memory (weg, wenn Strom aus) Ram, SRAM, DRAM

**BSP**

FPGA → serial ROM

(Festplatte - mischform, Wahlfrei, kriegt aber erst wenn Daten "vorbeikommen") Festplatte → Zugriff abh. von Position

Arten von Speichern

speziell FIFO, FILO

MRAM: Speicherbauslein mit Bitzellen auf magnetischer Basis

nicht flüssig

RWM und ROL sind beide RAM

# ROM (Read only memory)

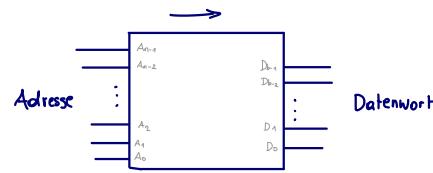

- Adresse anlegen → Daten raus

- Jede kombinatorische Logikfunktion kann dargestellt werden

- Kombinatorisches Bauelement

Anwendung: Logikfunktion, Prozessor (Befehlscode), Decoder, Linearisierung,

[BSP] Tabellenberechnung: EEPROM als Befehlsspeicher

|      | Adresse           | Daten        |

|------|-------------------|--------------|

| 0x08 | 00001000 00010100 | add r1 r2 r5 |

| 0x09 | 00001001 01001001 | cmp r2,r0,r4 |

| 0x0A | 00001010 11000101 | leq r4,r7,r3 |

| 0x0B | 00001011 11100010 | or r7,r6,r5  |

| :    |                   |              |

|      |                   | EEPROM       |

[BSP] Wahrheitstabelle

[BSP] Gray Decoder

[BSP]

Prinzip:

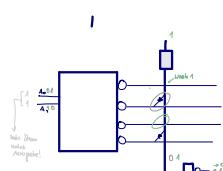

- 1) Decoder wandelt Adresse um (ausgänge invert)

- 2) Bits von Datenwort in Spalten → Full up auf 1

- 3) Diode an Kreuzpunkt von Spalte/Zeile → auf 0 (sonst 1)

- 4) Programmierung: Sektoren von Dioden

2 Adressbits →  $2^2$  Möglichkeiten!

Problem:  $\geq 2$  Adressbits →  $2^n$  Gates mit n Eingängen!

$1M \times 1ROM \rightarrow 1048576$  Gates mit je 20 Eingängen!

Lösung: 2D Codierung

Decoder: Je Ausgangbit 1 AND mit je 1 Eingang (teilweise Inv.) → genau 1 spricht an

MUX: Je Eingangbit 1 AND mit je 1 Adressbit + 1 Datenbit

↪ Alle ANDs vereinigt!

Mask ROM:

Dioden seien oder nicht (als Transistor realisiert)

Maske → Jeder Fehler ist fatal (Speicher nicht veränderbar)

Fertigung

PRO: Billig, Störfest, nicht programmierbar

Mehrere Datenbits → mehrere Arrays (BSP McDonalds Spielzeug)

Floating Gate (ex):

Gate hat keinen Anschluss → Tunneleffekt

Programmieren → wird Ladungsträger: Schwellwert

Störungen: Bit fällt um (nur bestimmte # von Prog. Zyklen) ~10.000

OTP ROM

PROM Überall Dioden selbst programmieren (1x brennen)

[BSP] 3 bit Decoder, 2bit Mux

möglichst quadratisch → hoher Gewinn

z.B. MUX 4x4 bauen (array!)

ROM Timing:

UV EPROM:

Transistoren mit Floating Gate

Erasable

Löscharbar mit UV (Fenster - zukleben)

Störfestig

Daher RegFile: Jagdieren, alles ausgleichen

EEPROM:

Wie UV EPROM

electric Einzelne Zellen lösbar (elekt. Feld)

erasable Write dauer

≈ 10.000 Zyklen pro Zelle

Warum haben UV Eproms Fenster? zum Löschen

Solid state drive

↳ Alterung, Isolator leiert aus

↳ als Repile ca. 10ms!

Steuersignale

Adressen : Speicherzellenwahl

chip select : "du bist gemeint"

output enable: Ausgangstreiber (low aktiv)

Datenbus, Ram, Peripherie

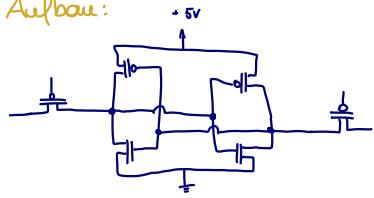

# SRAM (static random access memory)

Aufbau:

Symbolisch wie Latchzelle

"Inverterschleife"

Inverterschleife wird von Latchzelle durch 2 Transistoren angesteuert

↳ 2p Kanal fet (1,0 erzwungen)

Vereinfachung

Kein Buffer nötig, weil geordnete Struktur!

Write: Kein Transistornotig (nur einfacher Fet) weil einer immer Strom

Kein Transitionale für Feedback notig (wenn Treiberstärke richtig) → Feedback schwach

Speicherzellen einfacher gehalten durch Verwendung von Steuerlogik und Ein/Ausgangsbuffer für alle Zellen

Steuersignale:

gleich wie ROM (Adressen, Chip Select, Output enable, Write enable)

Bus Zusammenhänge: Write & Read (in/output) über gleiche Pins geführt → Hälfte der Pins gespart

Readtiming wie bei ROM

Writetiming Daten müssen vorher & nachher eine Zeit lang stabil sein, Adressen müssen gehalten werden

Rising von Chip Select und Write Enable, Pulsbreite = Write (WP)

Synchrones SRAM

Eingangssignale Synchron in Register

Read Daten asynchron flow through output

Synchron: Pipelined output

Zugriffe: überlappbar, über Pipeline

Cache/Burst Mode: ganzes Paket einlesen (automatic. increment.)

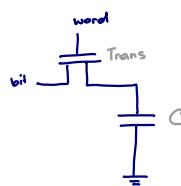

# DRAM

## Aufbau

Bit wird als Spannung in Kondensator abgelegt (H1 / L0)

Fet Schalter offen → Ladung erhalten

Write (WR): Laden / entladen des Fet

Read (RD): Auslesen der Spannung → Sense Amplifier (Auswertung)

→ konsumiert Ladung (Frequenz Back benötigt!)

H1; dr:

Kondensator: geladen oder nicht?

Schalter: schreiben und lesen

Refresh: Abfangen bevor bit kippt! ( $10 \cdot 100\text{ms}!$ )

Timer lädt C ständig auf  $3 \cdot 10^{-15}\text{F}$

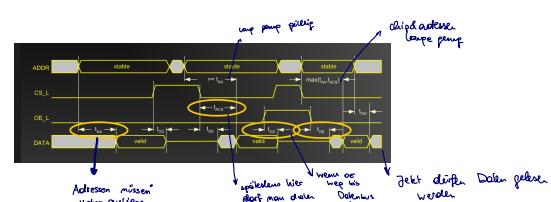

## Steuersignale

halbe Adressanzahl

Write Enable: RD oder WR → anderes muss stoppen!

Row, Col hintereinander anlegen

Ras Row Address Strobe

Cas Column Address Strobe

Read Timing: Cas = Output enable

Flanke: gültig

Pegel: output enable

Ras weg → Zeile refresh

Write Timing: Column address an → lesen stoppen!

## SRAM vs DRAM

Störfestigkeit: Einzelfall (nicht verallgemeinerbar!) ↓ wieviele Bits sind stand der Technik?

DRAM = 4 · SRAM

6 · Trans → 1 Trans, 1 Colat

DRAM: hohe Speicherperiode, als Hauptspeicher

SRAM: höhere Leistung, schnell, kein Refresh, als Cache für embedded speicher

## Zugriffarten

Page Mode: (2-fach schnellerer Datenzugriff in Row)

Zugriff → RAS active, RD-Adresse in Latch → Zugriff auf gleiche Row, nur CAS Pulse nötig

EDO: Extended Data OUT Ausgangssignal von OE → Überlappen von Zugriffen

## Schematisierte Zugriffarten

Standard: row - col - data - row - col - data

Page Mode: row - col - data - col - data

EDO: row - col - data - col - data

SDRAM: row - col - - data - row - col

DDRAM: - - row - col - - data

SDRAM = Synchro Dynamic RAM nur eine Taktflanke)

DDRAM = Double Data Ram (Speicher einbellen → Taktein → Pipelinien)

Verwendet beide Taktflanken → wird schneller → ca. 50% von Tastverhältnis, sonst ist Timing dafüro!

DDR3 Signallaufzeiten, Reflexionen → noch schneller

standardisiert, geht bis in Leiterplatte (wie beschaffen, das Timing passt?)

# MRAM

## Aufbau:

"Spindependent tunneling"

Write: Magnet drehen (umpolen) → mittels Spule, Magnetfeld

Read: Strom → Tunnelstrom groß oder klein?

alternativ: GMR / Pseudo Spin Valve

## Features:

non volatile

kleine Einzelspeicher wie Ram ansprechen

nicht für Cache

so schnell wie DRAM, 40% kleiner

Stromsparend

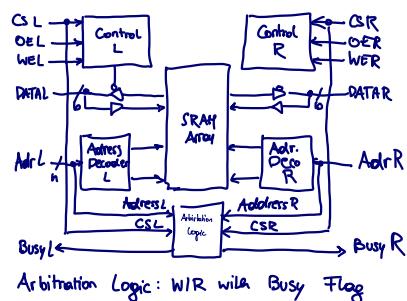

# Multiport RAM

Ein Ramarray mit Werten, mehrere Ports greifen zu

Doppelte Steuerlogik für RD, WR, CS, OE + "BUSY" Signal

Doppelte Adressdecoder & Doppelte Interfaces (Pins)

Semaphor Bit: Koordinierter Zugriff auf gemeinsame Ressourcen

Setzen von S.Bit → Request

Lösen von S.Bit → Release

DPRAM mit integriert

## Anwendung:

DPRAM: Adresse hat Bedeutung

[BSP] Temperatur: WD? Wie viel?

→ Daten nicht immer refreshed

Block: WR auf Adresse während RD

FIFO: Adresse simblos

Empty Flag: Blockieren

Kopplung von Zeitverhalten

## FIFO Prinzip

nicht wahlfrei zugreifen, Speichert in Tiefe

WR/RD überlappbar

Flags: (Hilfe für Verkopplung von 2 Systemen, die Daten austauschen)

Full Flag: alle Speicherzellen geschrieben, noch nicht gelesen

Half full Flag (Half empty flag): Vornahme für Speicherverwaltung

Empty Flag: Keine Daten zum RD im Speicher (WR, sonst RD undefined!)

Ringspeicher: Daten listenweise sortieren (internes Pointermanagement)

Was lesen wo nix steht → Pointervergleich

Fifo voll: schreiben?

Writepointer = Readpointer?

## Error detection & Error correction

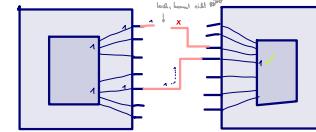

Speicher schützen?  $\rightarrow$  Fehlererkennung mittels Redundanz

Hammingdistanz  $D = 0 < D = 1$

$4 \text{ bit for } 16 < 5 \text{ bit for } 16$

EDC Bitfehler erkennen

ECC Bitfehler erkennen & korrigieren

Parity: Prüfbit an Datenwort anhängen  $D=2$

Hamming Code: Multibitfehler  $\rightarrow$  besser für breitere Datenworte

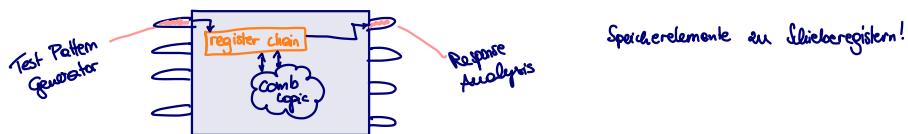

Blocksignatur CRC: Hash bilden  $\rightarrow$  Länger gespeicherte / übertragene Blöcke, in Hardware: Linear Feedback Shift Register, kein unbegrenzter Schutz!

Aliasing

ex:

Kondensator in CMOS?

-!-  Trenn kondensator

ex: <https://en.wikichip.org/wiki/intel/loihi>

# Zieltechnologien

ASIC = Application specific Integrated Circuit

Die Aufbau → Interconnect (Metallisierung) 5-12 Layer

Zellen (Silicium) 5-10 layer (inkl Transistoren)

Full Custom ASIC: Alles vom Designer festgelegt

anwenderspezifisch

Standard Cell ASIC: Zellen in Library mit fertigen Bauelementen

CBIC (bereits geleset → funktionieren)

Block mit Anschlüssen.

**BSP** CBIC in Software:

Vorgefertigte Funktionen

Elemente sind Betriebsgeheimnis

## Zellen Library

für Standard Cells, FPGAs, Gate Array Macros

von Hersteller / Vendor (koop. mit Hersteller)

vorgefertigte Funktionen

## IP Core (fertige Funktionseinheit, kann als Macro eingebunden werden)

Hard Macro: Block Box (Leitbahnen, Dotierungen vorhanden)

Soft Macro (bevorzugt) selbst synthetisieren → technologieunabhängig, VHDL, System on a Chip

## Gate Array (generische Lösung) MGA (Mask Gate Array)

Wafer haben Basiszellen → als Macros realisiert

Metallisierung von Anwender entschieden

Structured GA vs Structured Cell

↓

billiger

↓

weiter optimierbar

cores frei wählbar

- ) channelless Gate Array: Trans. Anschlüsse wählbar, Kanäle besetzt, Interconnect: Unbenützte Trans.

- ) channeled Gate Array: Trans. Anschlüsse fix, # an Kanälen frei → für Interconnect

- ) structured Gate Array: (embedded GA) gewisse Stücke für RAM, ROM, Basiszelle frei gehalten

## Programmable Logic Device: alle Layer fix, Interconnect programmierbar, vor. Matrix aus Macrozellen

ROM, PLA, PAL, CPLD, FPGA

ROM: (logik wandelt Adressen in Daten um)

- ↳ programmierung: EPROM (elektrisch lösbar), PROM & OTP (elektrisch permanent), mask progr. ROM

- ↳ Löschen: UV EPROM (UV lösbar), EEPROM (elektrisch)

## Programmable Array Logic

PAL (nur AND Array)

PLA (AND, OR als Core programmierbar)

## ASIC Technologien

|             |                                               | cell design | cell placement | cell connect                |

|-------------|-----------------------------------------------|-------------|----------------|-----------------------------|

|             |                                               | user        | user           | user                        |

| FULL Custom |                                               |             |                |                             |

| semi custom | Standard Cell                                 | library     | user           | user                        |

|             | NGA { channelless<br>channeled<br>structured} | { fixed     | fixed          | user                        |

| PLD         | ROM<br>PAL, PLA<br>CPLD, FPGA                 | { fixed     | fixed          | fixed<br>also programmable! |

3 Arten von Programmierbarkeit: Interconnect, Macrozelle, I/O Zelle

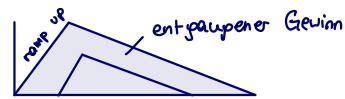

ASIC → Break Even (Marktanalyse)

FPGA (billig) → Massenproduktion teuer

CBIC (teuer) → Massenproduktion billig

Gewinnmodell

ASIC ~ 0,5 Jahre

FPGA ~ 1 Wo

selbst design :-)

## Programmierbare Logic Devices (CPLD & FPGA)

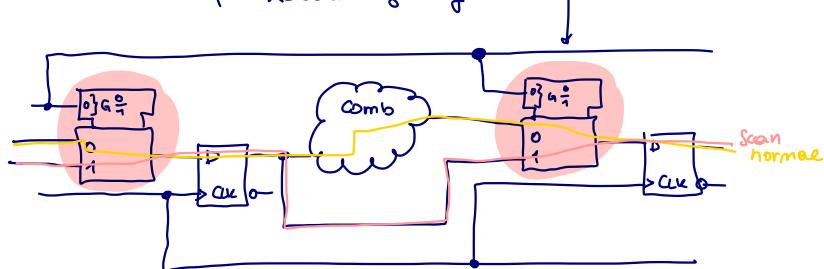

programmierbar bei FPGA: Funktion in Macrozellen, Funktion in I/O Zellen, Auswählen oder Verbindungen

programmiert durch "schaltbare Verbindungen" (wenn Verbindungen weg ist es ein ROM Transistor)

irreversibel (durch thermische Zersetzung v Isolationsleicht)

irreversibel (gründliche Simulation)

non-volatile (bootfähig), radiationhard

SRAM Konfiguration

Kopierschutz

"in System" Speicher überschreibbar → volatile

X Alterungsprobleme (irgendwann wird nicht mehr gut isoliert)

"Kontaktwiderstand"

X störanfälliger, Platzbedarf

1ns delay (zw Wolfram, Si, Al)

EEPROM Konfiguration

non volatile, überschreibbar

so groß wie Antifuse

X störanfällig

## Programmierbare Logikzellen - Macrozellen

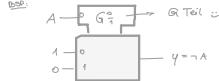

HUX basierte Logikzellen: mittels Shannons Erweiterungstheorem (nicht zu verwechseln mit Microcontroller!)

Funktionsweise: Die Variablen / Logikfunktionen werden schrittweise mit 0,1 ersetzt  $\rightarrow$  HUX Baum? durch zweistufige Logik ersekbar

Jede Variable kann beim G-Teil angelegt werden

Realisierung: Inverter, AND, OR, Identität werden alle mit einem HUX dargestellt.

Alle können mit 2 Variablen (als Latches =  $\frac{1}{2}$  FF) manche mit 3/4 Variablen

ACT 2: HUX hat 2 Eingänge

## Look up table basierte Logikzellen (LUT)

Verknüpfungen von n Variablen eindeutig darstellbar (Wahrheitstabelle)

4 in 1 out (1 bit Speicher, 4 Adressen, Wahrheitstabelle)  $\rightarrow$  allg. als  $2^n \times 1$  Bit

LUT theoretisch als RAM verwendbar (zu teuer)

konstantes Timing

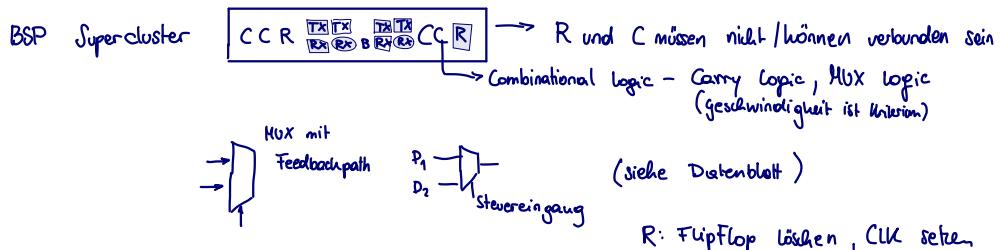

BSP Altera / Intel Logic Element

DSP Block ist Multiplier (zur Berechnung von FFT, Faltung)

LAB - Logic Array Block

Wird sehr schnell sehr komplex!

and carry chain:

<https://www.intel.com/content/www/us/en/programmable/documentation/wtw1441782332101.html#wtw1443170033156>

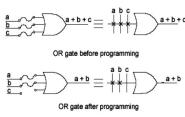

## PAL Logikzellen

Pull up R, Collector & Treiber / open drain

Direkte Implementierung der DNF

Wired AND, connecting OR  $\rightarrow$  FF für sequentielle Logik

in: j =  $\overline{D_j}$

in: i =  $\overline{D_i}$

$2^{i+j} \cdot 4$

zellen

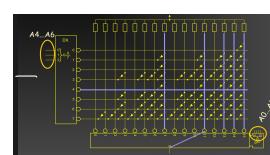

Notation: Horizontal AND, Vertikal signale, Kreuzungspunkte - Programmieren eher

AND - PLD Notation

OR - PLD Notation

Verbindungen die wir nicht wollen: Transistoren

XOR, invertieren  $\rightarrow$

Wie realisiert man programmierbaren Inverter?

Dioden

Wozu braucht man programmierbaren Inverter?

Parallel Expander: doppelte Durchlaufzeit, Kaskadierung von Stegen

CPDL durch großes Interconnect

Logic Expander: zusätzliche Durchlaufzeit, löst einzelne Produktterme (und verarbeitet diese schon zuvor!)

$$\begin{aligned} \text{BSP} \quad & (\neg A \wedge C \wedge D) \vee (\neg B \wedge C \wedge D) \vee (A \wedge B) \vee (B \wedge \neg C) = \\ & = [\neg(A \wedge B) \wedge C \wedge D] \vee [B \wedge \neg(A \wedge C)] \end{aligned} \quad \downarrow \text{Vorverarbeitung, stellt 4 nach 2!}$$

programmierbarer Inverter: Verarbeitung | Umwandlung & richtige Ausgabe inverser Funktionen

ID

BSP

minimale DNK aus KV Diagramm

HOW?

Bitstream an bestimmte Zellen

# LAB:

Scrubbing: Konfigurationspeicher während dem Betrieb überschreiben

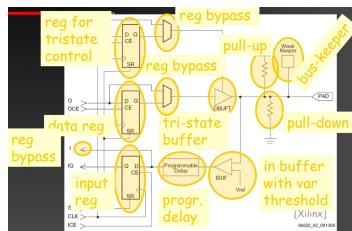

## Programmierbare I/O-Zellen

Wir wünschen uns:

Eingang - Super Schwellwerk (versch. Spannungen), direkt Input / Input FF, Timing mit Verzögerung

Ausgang - super Schwellwerke, passives Pull up / Pull down, direkt Output / FF latch, Tristate & Open drain, Flanke/Treiber wählbar

PAD als Eingang → out tut waffern → tristate (OBUFT)

in tut waffen → weg (IBUFT)

bus keeper = schwacher Treiber

entweder pull up oder pull down (beides nicht möglich!)

MUX = Steuereingang kann an ROM hängen.

## Programmierbares Interconnect

Wir bekommen alles, was wir uns wünschen, aber die Kapazität ist weg

nix kurzschließen

(maximale Flexibilität (viele Verbindungen)  $\wedge$  langsam)  $\neq$  maximale Geschwindigkeit  $\wedge$  minimale Kapazität)

→ Direct connect (nomen est omen) - Signal wird mittels Meshierung gewählt

→ carry logic (ohne Antifuse!)

Konfig. Error → Radiation hard für FPGA

Signale in PLA (völlig sym. globaler Bus von jeder Quelle zu jeder Senke!)

Quellen:  $\forall$  I/O Pins,  $\forall$  dedicated Inputs,  $\forall$  Macrocell Outputs

Senken: LAB Inputs

## CPLD - Interconnect

hochregelmäßig & symmetrisch (einfache Struktur, voll verbunden, PPR einfach  $\rightarrow$  Timing vorhersehbar ✓)

bestimmt Funktion (Flit & Struktur fix  $\rightarrow$  P2D)

→ Konfiguration

on chip flash memory OR In-system Programmierung OR JTAG (drei system/usb)

non volatile  $\rightarrow$  security bit

(damit niemand heutet)

## Actel Interconnect

Antifuse  $\rightarrow$  effiziente Verbindung

hoch = regulär, highway = variabel (Timing, PPR schwer, highway = Flussrichtung)

bestimmt Funktion (MUX, Signale wohin?)

## FPGA Interconnect

hochkomplexes Netzwerk (mehrstufig, Timing kann vorhersehbar)

Routing, Funktion getrennt (Flit durch LUT)

→ Konfiguration (ich muss SRAM programmieren)

durch externen Microcontroller konfiguriert OR Interfaces OR Auswahl durch Pinbesetzung

oder seriell von PC, Config device

· seriell, parallel, jtag

## HardCopy Devices

FPGA  $\rightarrow$  ASIC

1 Woche Lieferzeit & ich darf selbst backen!

PS: Umprogrammieren von FPGAs im Betrieb =

Humor Design!

Konvektion:

transient:

crawbar:

# Datenblatt - Aufgaben

Grenzen:

Absolute Maximum Ratings: Limits (geht man darüber, ist es hin)

## Temperatur

Fehlerrate steigt mit Temperatur exponentiell, chip wird langsamer

→ junction Temperatur (unmittelbar am Die)

$$\text{vereinfachte Wärmeleitungsgleichung: } T_{\text{junction}} = T_{\text{ambient}} + P \cdot \vartheta_{jA}$$

$\vartheta$  Wärmewiderstand: Maß für Vermögen zur Wärmeleitung

spezifisch: Konstante

absolut:  $[K/W]$ , je größer  $\vartheta$  desto ...

messbar: Case & ambient

Gehäusetemperatur Umgebungstemperatur

P... Verlustleistung

$\vartheta_{jA}$  Wärmewiderstand  $[K/W]$

Was ist Wärmewiderstand? Einheit

$\vartheta_{jc}$  Wärmewiderstand junction/case  $\xrightarrow{\text{abh. von}}$  Gehäusetyp

$\vartheta_{ca}$  Wärmewiderstand case/ambient  $\xrightarrow{\text{abh. von}}$  Gehäuse, Einbaulage, Kühlkörper, Lüfter

$\vartheta_{ja}$  Wärmewiderstand junction/ambient  $\rightarrow \vartheta_{ja} = \vartheta_{jc} + \vartheta_{ca}$

- Lüfter (erzwungene Konvektion)

- Kühlrippen

Warum schmilzt Diode nicht?

Daher: Temperaturfühler (Diode hängt an Die, direkte Messung von  $T_{\text{junction}}$ )

$$\frac{dU_D}{dT} \Big|_D = -2 \text{ mV/K}$$

## Komponenten der Verlustleistung

statischer Anteil: tritt auf wenn Chip nicht getaktet  $\hat{=}$  zusätzlicher Strom trägt nicht zur Erwärmung des Chips bei quiescent current

Bei CMOS: Tunnelstrom, Leckstrom, Sperrstrom, Ströme über Pull up Widerstände

dynamischer Anteil: Ladestrome dominieren (switching current) or transiente Kurzschlüsse (crawbar current)

Verlustleistung durch periodisches Schalten von 0 auf  $V_{DD}$ :  $P_{\text{load}} = C_{\text{load}} \cdot f \cdot V_{DD}^2$

→ Seltene Umladen, geringe Spannung  $V_{DD}$

Verlustleistung proportional zu Kapazität, Frequenz, Versorgungsspannung

Beispiel zur Verlustleistung berechnen

transiente Kurzschlüsse: kurzzeitig leiten beide gut

kleine Asymmetrie der Schaltzeitpunkte

seltene Umschalten

Energie sparen: CLK Gating

Dynamic Voltage & Frequency Scaling

LV... Low Voltage

LVTTL ...

## Versorgungsspannung:

Reduktion von Versorgungsspannung auf Hälfte

→ geringere Verlustleistung

→ für CMOS supi

→ oft nur bei Core ( $\setminus 10$  bleibt)

Ungeeignete Versorgung:

HV: Chip heiß → Ausfall → Gate Oxid

LV: Chip langsam → hohe Ströme!

## Spannungspegel & Störungssabstand

Spannungspegel am Eingang: Eingangsspannung beachten!

sicher als 0 (unterhalb Eingang)

Spannungspegel sicher als 1 (oberhalb Eingang)

?! Schwellwert! (Pegel = Grenzwert!)

↳ aufpassen, sonst out of spec!

Störungssabstand: Sicherheitsabstand zu zugehörigen Ausgangssignalen

Kompatibilität:

hängt von Höhe des Schwellwertes ab; (bzw "undefined" ab!)

Wenn Schwellwert zu niedrig, nicht möglich

(muss direkt an Grenze zu Output High / Input High liegen!)

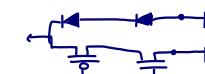

Klemmodioden:

wie Schalter (schließen sobald U an IO Pin  $> V_{DD} + 0.6V$ )

$< GND - 0.6V$

unerwünschte Überspannung abgeleitet (halten aber auch nur begrenzt!)

Spannungspegel am Ausgang:

Lopikpegel ideal:  $1 = V_{DD}$   $0 = GND$

Lopikpegel real: Verschiebung durch Schwellspannung / Spannungsabfälle wg  $I_{out}$

Grenzwerte (Abhängig von Lopikfamilie / Versorgungsspannung)  $\min U_{out} = 1$

$\max U_{out} = 0$

$V_{IH}$  (High level input voltage) → kl. U die noch als 1 erkannt wird

$V_{IL}$  (Low level input voltage) gr. Spannung, die als 0 wird

$V_{OH}$  (High level output voltage) für 1 zumindest spannung X

$V_{OL}$  (Low level output voltage) für 0 höchstens gegebene spannung X

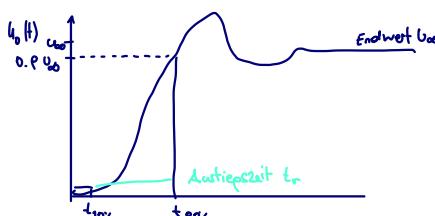

## $t_r$ Rise Time (Anstiegszeit)

Dauer des Signalanstiegs von 10% auf 90% des Endwerts

Flankensteilheit: In Datenblatt durch  $t_R$  (Input rise time)

$t_F$  (Input fall time)

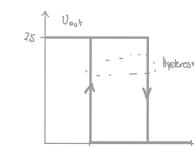

[BSP] Schmitt Trigger Eingang: Hysteresis

100mV Hysteresis um 1,2V herum

Hysterese, Schwellspannung etc benennen können

Toleranz der Hysterese im Datenblatt auffindbar

# Treiber:

## Ausgangstrom

Wirkung Ausgangströme  $I_{out}$

- 1) Abweichung v.  $I_{out}$  von Idealwert wg Spannungsabfall an  $R_{out}$

- 2) zu hoher Ausgangstrom: GW für 0,1 nicht mehr eingehalten

Signalverzögerung steigt, Flanken flach

Ausgangstreiber überlastet

Ausgangswiderstand

zulässige Ausgangströme, Typische Ausgangströme aus Datenblatt auslesen

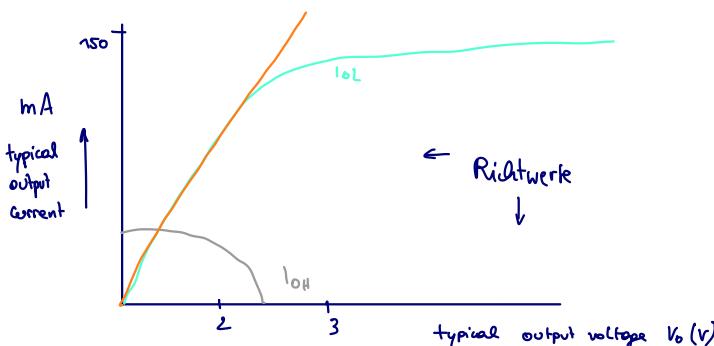

## Ausgangskennlinie

Steigung der Kennlinie:

Ausgangswiderstand:

- Abweichung von  $I_{out}$  vom Idealwert

- verzögert Umladen / R/C Verhalten

- An Steigung d. Ausgangskennlinie ableiten

$r_o = \frac{\Delta V_o}{\Delta I_{out}}$  (Am Bild orange)

- von Logikpegel, Ausgangstrom abhängig (~~konstant~~)

- Durch Treiberstärke eingestellt

- Idealwert Null ≠ erreichbar!

typical output current: Abhängig von Exemplarsteuerung,  $V_{DD}$ ,  $T$

Worst Case Angaben:

unter schlechtesten Bedingungen immer noch gültig

alle anderen Annahmen optimistisch → Mehrkosten (von Murphy)

↳ Typical Values (unbrauchbar), Messergebnisse v. Prototyp (Funktionserweis)

Fanout:

Wie viele Eingänge an Ausgangstreiber (meist max hohe positive Belastung!) sehr klein, stört nicht

↳ Überzählige Eingänge: Wenn benötigte # von Inputs nicht verfügbar, wird größeres Gitter gewählt, überzähliger Eingang mit anderem Paar zsm abschließen/ logisch neutralisieren an  $V_{DD}$ , GND

↳ Offene Eingänge: parasitäre Effekte bei bestimmten Spannungen

(In FPGA automatisch korrekt behandelt) (bei CMOS typischerweise „0“ undefined)

Spannungswerte sind labil / störsensibel → subtile Fehler, unnötiger Leistungsverbrauch

jede Störung hat keinen Gegner → Regel geht in irgendeine Richtung

Eingangsströme:

Angeschlossener Eingang belastet vorhergehenden Ausgang

## Spezifikation des Zeitverhaltens

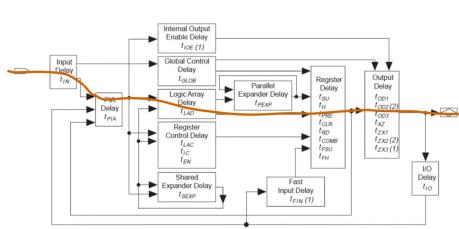

Timing - Angaben → kombinatorische Logik: Propagation Delay, Output Enable, Output Disable

→ sequentielle Logik: Flip Flop Input → Setup Hold window output → Clock to Data out Taktflanke, Dauer, Delays, Setuptime

steuern Signale (CLK enable, ...) wie lange bis wirklich Q

Interconnect: versch Segmente, Parameter

## Timing Modell

## Optimierung des Zeitverhaltens

Einflussfaktoren:

- Versorgungsspannung (RC Ladekurve)

- R durch Rout, Dm von Fet an Out, R der Leitung

- C durch Kapazität Leitung, Gate, lasten, Programmierbare Verbindungen

- Kapazitive Last  $\Rightarrow$  Ohmsche Last!

- Einfluss Lastkapazität - Größenordnung  $10\text{ pF} \dots 1\text{ a ns!}$

- An CiOTB, CiOLR ablesbar

- Temperatur, Treibstärke

- Eingänge, Routing, Exemplarstreuungen

Hohe Temperatur und niedrige Versorgung verlangsamen den Chip

Induktivität?

Optimierung: starke Treiber (hastet Chipfläche)

Fan out verringern (1 out mit 10 zu 2 out mit 5)

Sinnvolle Constraints (Timing Con  $\Rightarrow$  Optimierung auf wesentliche, nur unbedingt nötige Pins festlegen, Layout Vorgaben)

## Slew Rate

maximale Steilheit des Spannungsanstiegs (am Out)

hohe Slew Rate: Out liefert hohe Stromspitzen ( $\nearrow$  verursachen Störung)

Vermindert Delay

[BSP] Stratix

Taktnetz: (Sollte man verwenden!)

Flanken überall gleichzeitig  $\rightarrow$  verzweigtes Netz, hohes Fan Out

Spiques (Fischgerippe!)

Clocking: hierarchisch 4 PLLs + 2 enhanced PLLs

Features: Signal Tap (Logik Analyser)

Speedrate Pinning

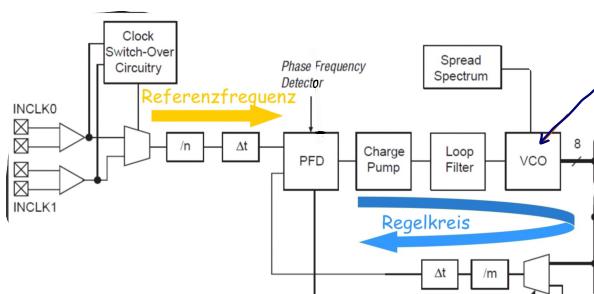

## PPL (phase locked loop)

Frequenzmultiplizierer VCO

- DC höher Freq höher

- generiert Frequenz (Spannungsfeststeller Out)

- so gefügt, dass er input entspricht

Phasenreferenz PFD: schaut wie 2 Eingänge zueinander sind

geblockt  $\rightarrow$  nur These einstellen

(auch Phasendetector)

Spread spectrum: VCO wird verstellt damit Stromspitze nicht passiert

# Synchrones Design

**boolsche Logik:** eindeutig zeitfreie Beschreibung, unabhängig von Implementierung (kombinatorische / sequentielle Logik)

↳ Realität: Delays (nicht vermeidbar, nicht deterministisch)

Einflussfaktoren auf Delay:  $\underbrace{\text{Logikstufen, Routing}}_{\text{durch Technologie fixiert}}$ ,  $\underbrace{\text{Exemplarsteuerung}}_{\text{worse case annehmen}}$

Delaykomponenten: Gate Delay, Interconnect Delay

Verhalten eines Chips ist nicht exakt vorhersagbar!

$\Rightarrow \exists$  Grenzen für Design (Leistung hat Grenzen, Laufzeit nie gleich  $\rightarrow$  Skew)

**Skew:** Unterschied im Signaldelay  $t_{skew} = |t_{delay_1} - t_{delay_2}|$

Folgen  $\rightarrow$  (theoretisch): eingeschwungener Zustand ist  $\neq \emptyset$

$\downarrow$  (praktisch): Glitch  $\Rightarrow$  Hazard

Glitch: Puls, den wir nicht wollen

Puls: Folge von entgegengesetzten Flanken

Hazard: Möglichkeit für Glitch

**Hazard:**

"Möglichkeit für Entstehung von Glitches"

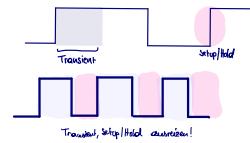

Gefährlich: Glitch wird in Zustand übernommen wo Flanke auswirkt hat

Glitch wird in Zustand übernommen wo transizenter falscher Wert in Speicherelement

Arten von Hazards

static 1: hölt gerne 1er, wiegt Nullen...

static 0: hölt gerne 0er, wiegt Einsen

dynamic Glitch: Transitions, die wir nicht wollen

**BSP** Asynchroner Teiler

mehrstufig verzweigter rückkopplungsfähiger

Teiler würde mit Glitches hin werden!

**Datenkonsistenz:** Daten für gleichen Zeitabschnitt richtig korreliert

(Asynchroner Zähler + optimal!)

**Grundproblem:** Wir dürfen nur mit konsistenten eingeschwungenen Zuständen arbeiten

Lösung: synchrones Design

$\exists$  asynchron, mit bounded delay & delay insensitive (erst in RestVO)

$\Rightarrow$  Bei boolscher Logik sind explizite Zeitbezüge nicht darstellbar!

beschränkt in/out zeitfrei

kontinuierlich gültige Eingänge

(Skew macht ungültige Zwischenzustände!)

## wie wir Synchrones Design bauen

Lösung im Zeitbereich finden

Eingänge verarbeitet, nachdem alle Einschwingvorgänge sicher beendet

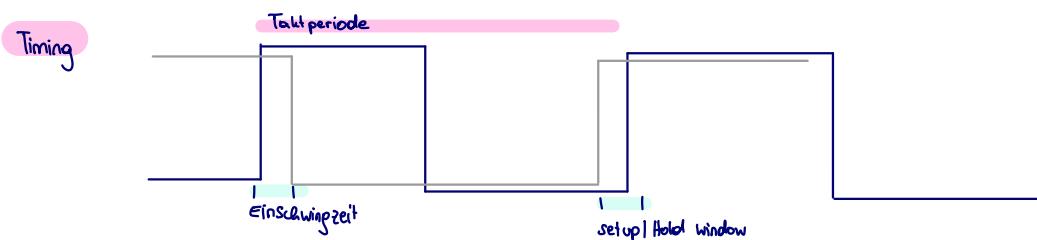

Taktsignal: Gibt Zeitpunkte an, wo Daten gültig

**BSP:**

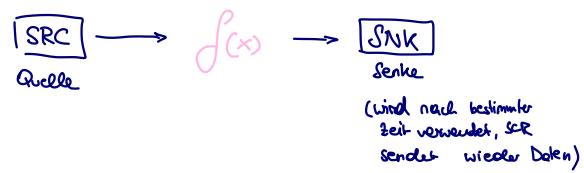

SRC schickt um 7 Uhr Daten  $\rightarrow$  SNK übernimmt um 7<sup>o</sup>

SRC schickt um 8 Uhr nächste Daten

$\rightarrow$  globaler Plan nötig

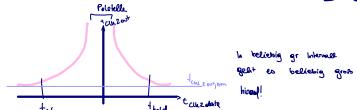

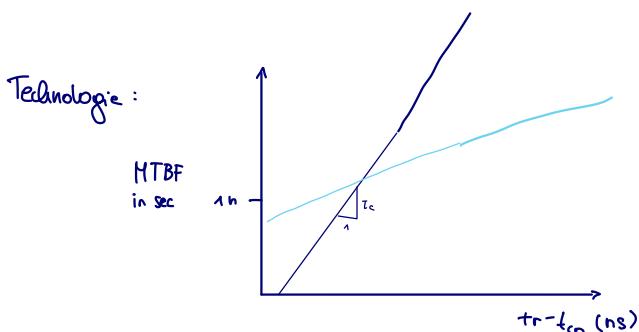

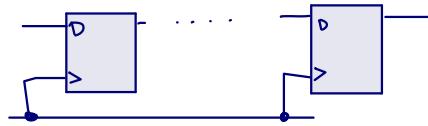

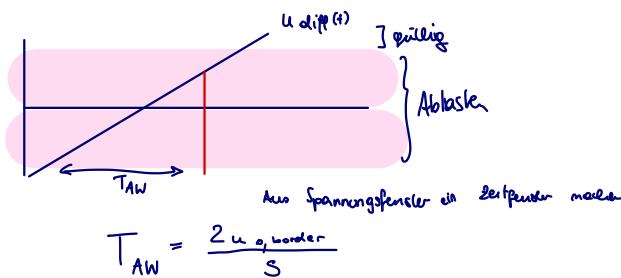

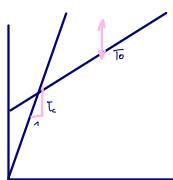

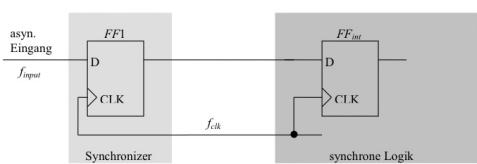

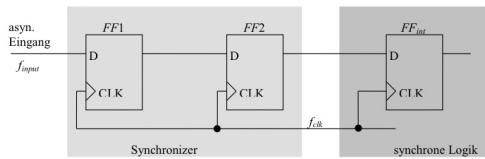

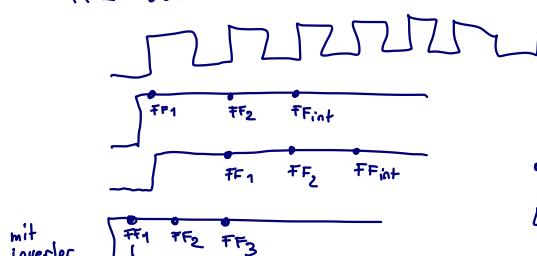

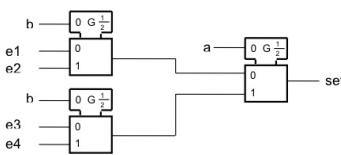

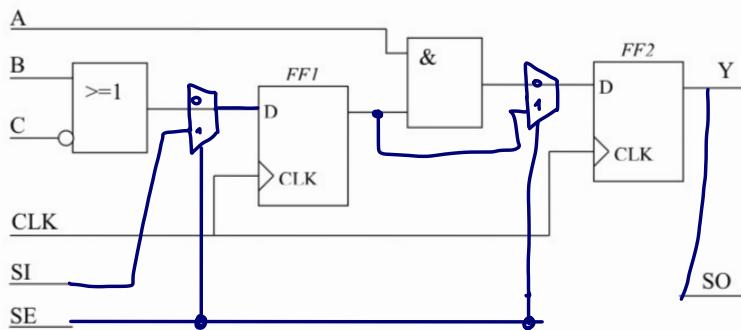

- 1) lokaler Plan muss von f umgesetzt werden