## **Computer Systems**

Advanced Processor Pipelines 1

Daniel Mueller-Gritschneder

15.04.2024

#### Persons

Prof. Daniel Müller-Gritschneder Embedded Computing Systems

Florian Kriebel Embedded Computing Systems

#### Sources

This book covers the basics of how to design a simple in-order scalar processor pipeline <u>in detail in hardware</u>.

- Literature: "Digital Design and Computer Architecture: RISC-V Edition", by Sarah L. Harris and David Harris

- https://shop.elsevier.com/books/digital-design-and-computer-architecture-risc-v-edition/harris/978-0-12-820064-3

- https://pages.hmc.edu/harris/ddca/ddcarv.html (Includes resources for students!)

- They also provide slideshows the basis for ours! You can investigate extended version at their website.

- Available at TU's library: <a href="https://catalogplus.tuwien.at/permalink/f/qknpf/UTW">https://catalogplus.tuwien.at/permalink/f/qknpf/UTW</a> alma21139903990003336

#### Sources

So-called application processors have many additional features: Branch prediction, Out of order execute, Scoreboard, Superpipelining, Multi-issue, Superscalar, VLIW, Multi-threading, ...

**Disclaimer**: The book provides advanced concepts from real complex processor designs. We only study the concepts at a high level. For simplicity, the used pipeline models in this lecture are reduced strongly in complexity.

**But**: We will have a look at some current RISC-V processor designs

Literature: "Computer Architecture A Quantitative Approach" 5th Edition - September 16, 2011 Authors: John L. Hennessy, David A. Patterson eBook ISBN: 9780123838735

- https://shop.elsevier.com/books/computer-architecture/hennessy/978-0-12-383872-8

- Available at TU's library: https://catalogplus.tuwien.at/permalink/f/8agg25/TN cdi askewsholts vlebooks 9780123838735

#### Content – Session 1

- Short Recap: RISC-V Assembly

- Five-Stage In-order Scalar Processor Pipeline

- Pipelined Execution & Stages

- Data Hazards & Forwarding Paths

- Control Hazards

- Branch Prediction

- Static Predictors: Taken / Not taken /BTFNT

- Branch Target Buffer

- Dynamic Predictors: 1 bit / 2 bit

- A look at a real RISC-V processor CVA6

- A look at a real RISC-V processor ESP32- C3

- Trap Handling

Optional, not relevant for exam

# **Short Recap: RISC-V Assembly**

### Writing a small assembly function: abs\_value

• Example C-Code 1

```

// Computes the absolute value

int abs_value(int a) {

if (a<0)

a=0-a;

return a;

}</pre>

```

#### JALR rd,rs,imm

Behavior: rd=PC+4

PC=rs+sign\_extend(imm)

JALR x0,ra,0

PC=ra

#### RISC-V Code

- According to ABI a is given to the function in register a0

- The function should also return a in register a0

```

abs_value:

BGE a0,zero,abs_value_return # if a>=0

SUB a0,zero,a0 # a=0-a

abs_value_return:

RET # JR ra

```

function return which is a pseudo instruction for JR ra which is a pseudo instruction for JALR x0,ra,0

### Writing a small assembly function: vec\_add

#### Example C-Code 3

```

// vector addition of 4-element integer vectors

void vec_add(int[4] a, int[4] b, int[4] c) {

unsigned int i;

for (i=0;i<4;i++) {

c[i] = a[i] + b[i];

}

}</pre>

```

#### RISC-V Code

```

# base address of a: a0,

# base address of b: a1,

# base address of c: a2,

# i: t0, constant 4: t3

vec add:

LI t0,0

# i=0

# t3=4

LI t3,4

vec add for:

LW t1,0(a0) # t1 = a[i]

LW t2,0(a1)

# t2 = b[i]

ADD t1,t1,t2

# t1 = a[i] + b[i]

\# c[i] = t1

SW t1,0(a2)

ADDI a0,a0,4

#next element is base address + 4

ADDI a1,a1,4

#next element is base address + 4

ADDI a2,a2,4

#next element is base address + 4

ADDI t0,t0,1

# i++

BLTU t0,t3,vec add for \# for (i < 4)

# void return

RET

```

#### RISC-V Simulator

• Visual Studio Code

Extensions -> Venus Simulator for RISC-V Assembly

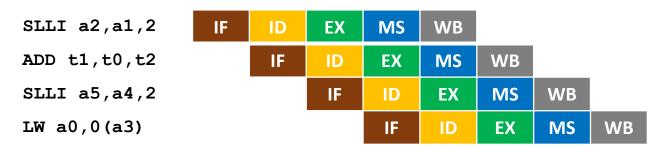

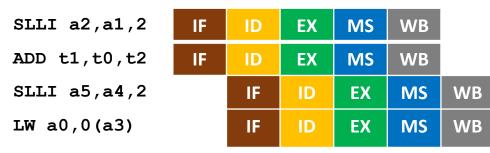

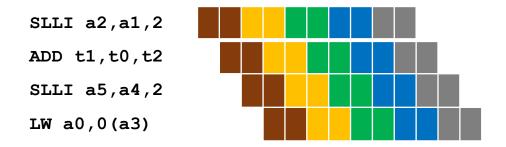

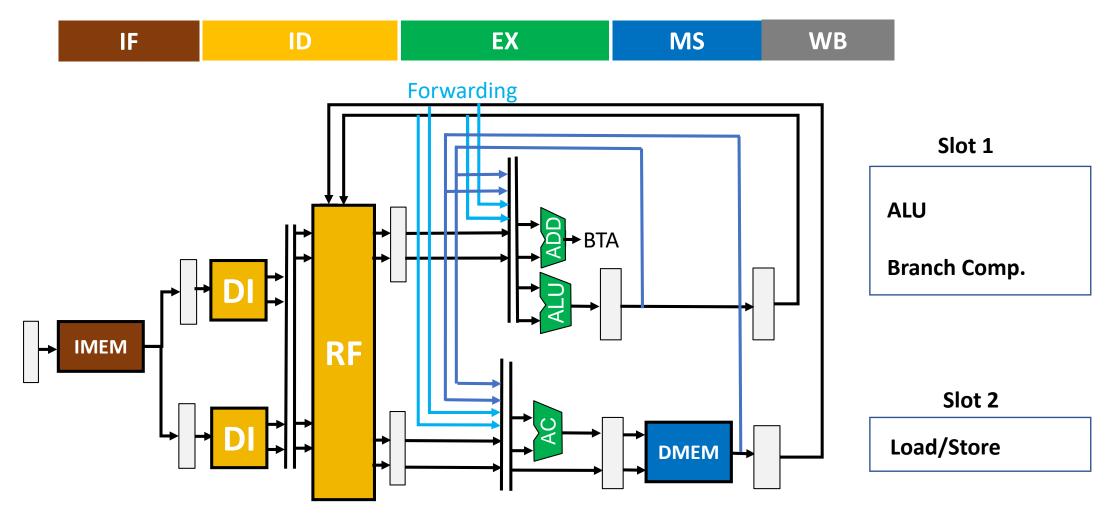

## Pipelined execution

- We break down instructions in sub-computations and place them into stages (s)

- We execute the instructions in a pipelined fashion ("Fließband")

| SLLI a2,a1,2 | <b>s1</b> | s2        | s3        | s4 | s5 |    |    |

|--------------|-----------|-----------|-----------|----|----|----|----|

| ADD t1,t0,t2 |           | <b>s1</b> | s2        | s3 | s4 | s5 |    |

| LW a0,0(a3)  |           |           | <b>s1</b> | s2 | s3 | s4 | s5 |

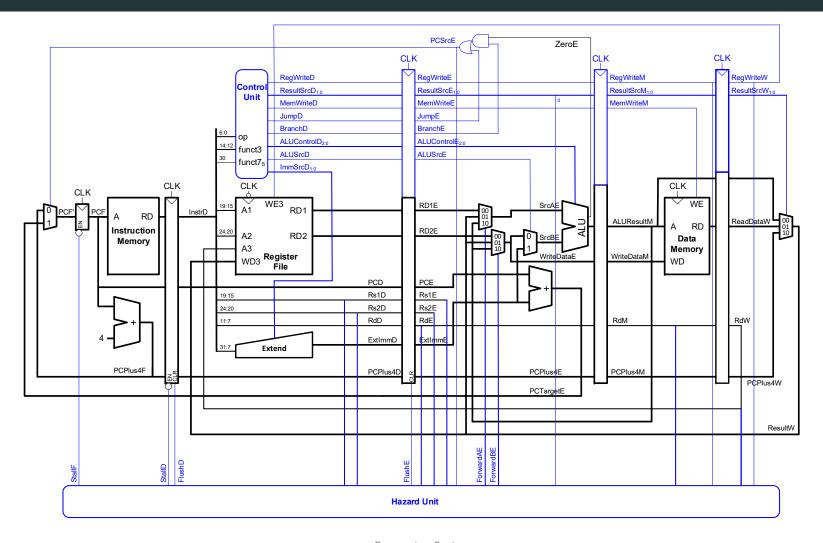

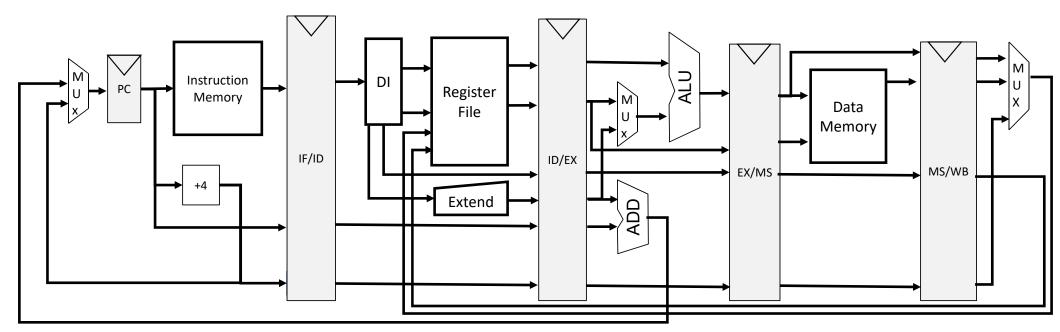

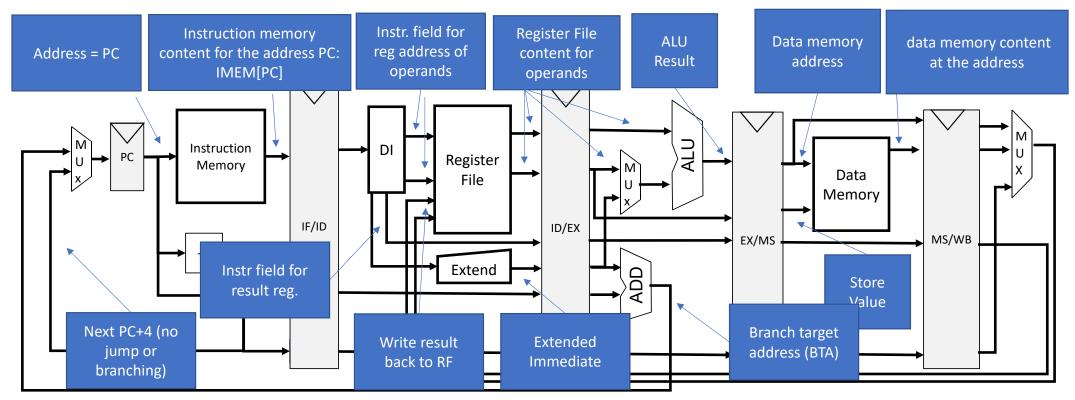

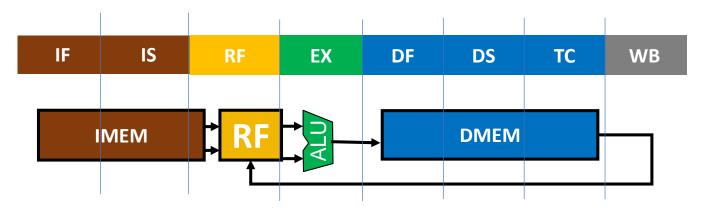

## Recap: Five-Stage In-order Scalar Processor Pipeline (Harris & Harris)

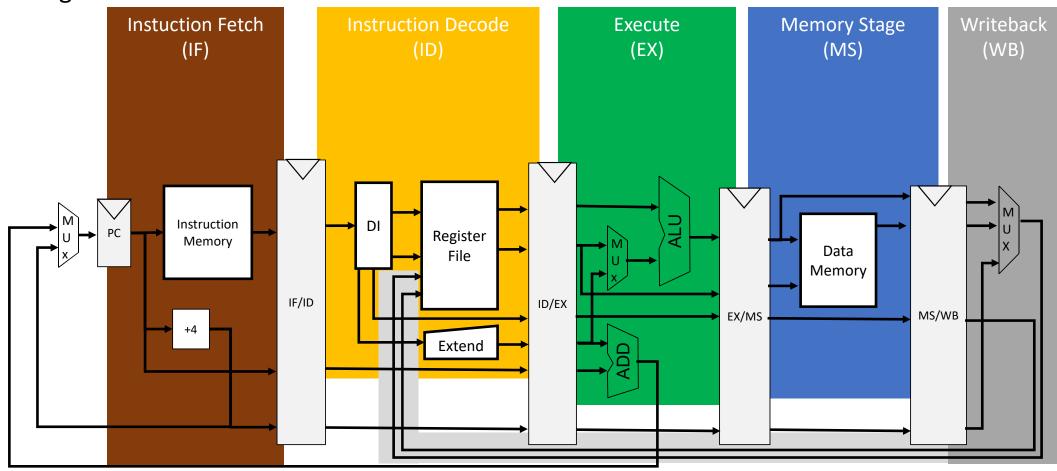

### Five-stage Pipeline - Data Signal Busses

- Data path scheme of the pipeline:

- We omit all control signals.

- We are only interested how instructions can "flow" through the pipeline (data signal busses)

### Five-stage Pipeline - Data Signal Busses

- Data path scheme of the pipeline:

- We omit all control signals.

- We are only interested how instructions can "flow" through the pipeline (data signal busses)

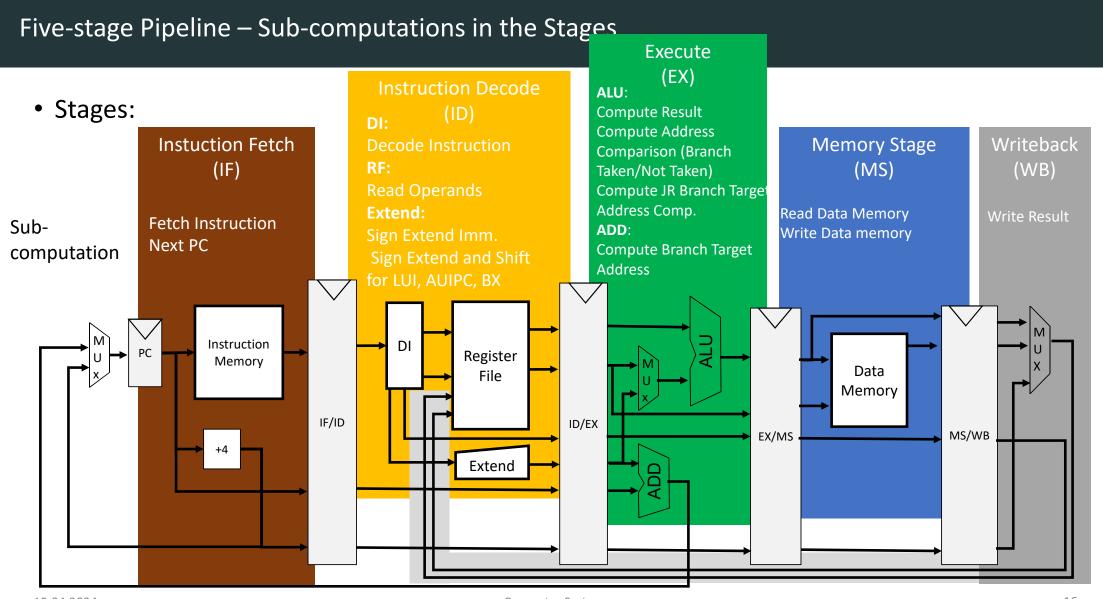

## Five-stage Pipeline - Stages

• Stages:

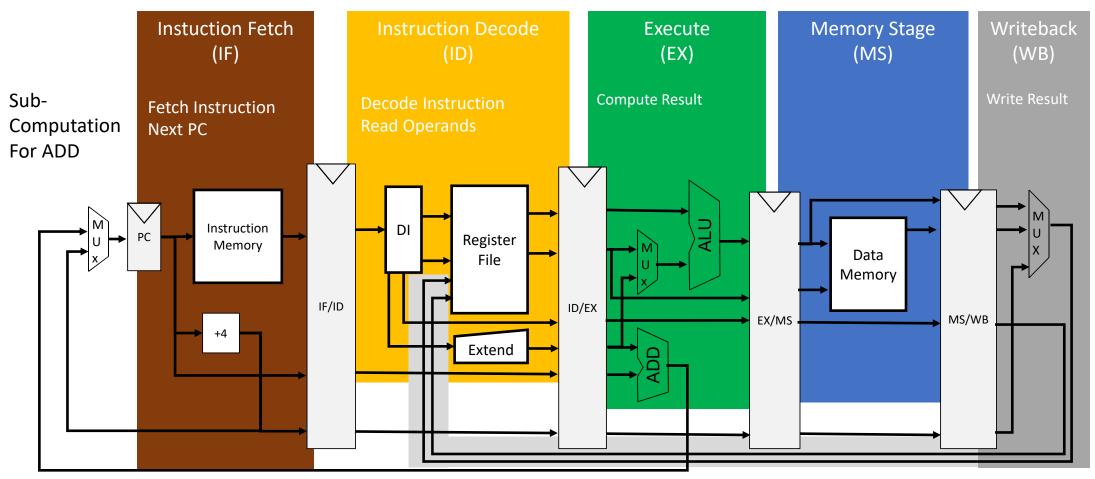

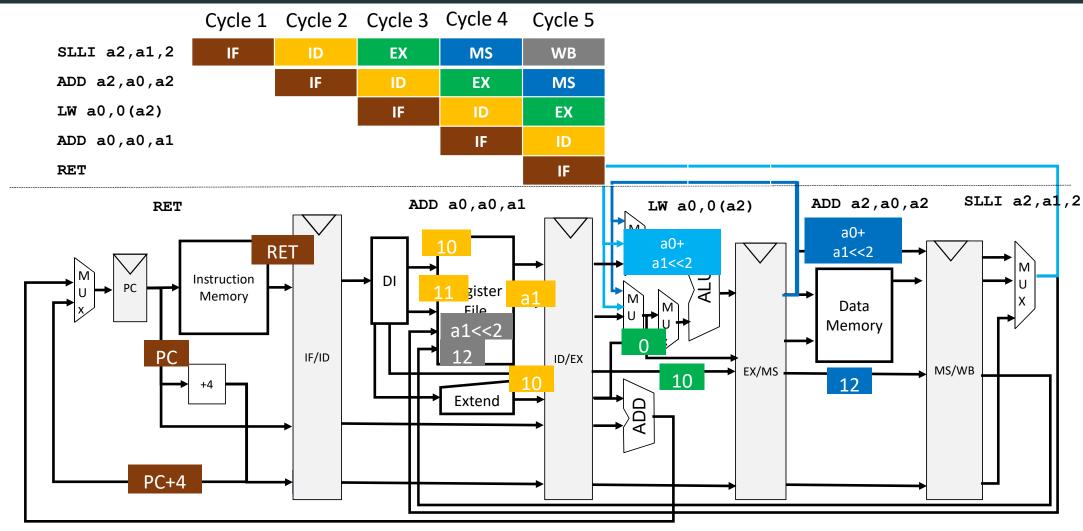

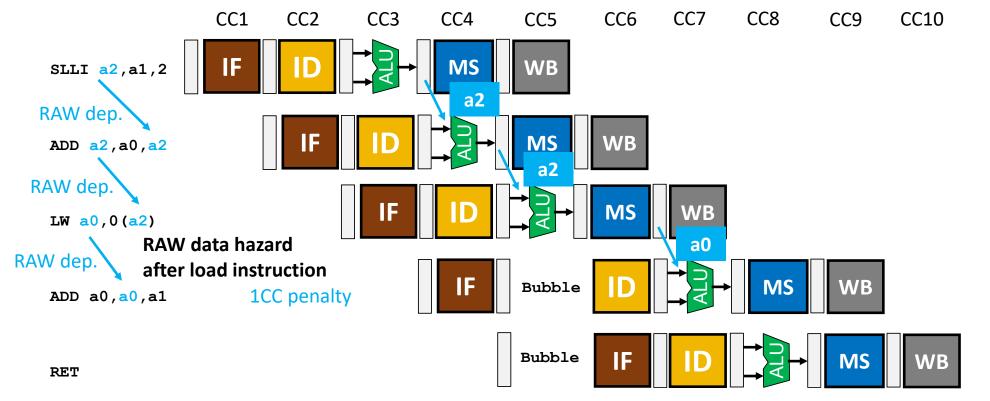

#### Five-stage Pipeline – Sub-computations in the Stages (Example ADD)

• Instructions do not require all subcomputations, e.g. ADD

Example program

```

#int test1(int *x, int i) {return x[i]+i;}

test1:

SLLI a2,a1,2 # a2=i*4

ADD a2,a0,a2

# baseaddr+offset i*4

LW a0,0(a2) \# a0 = x[i]

ADD a0,a0,a1

# a0 = x[i] + i

RET

```

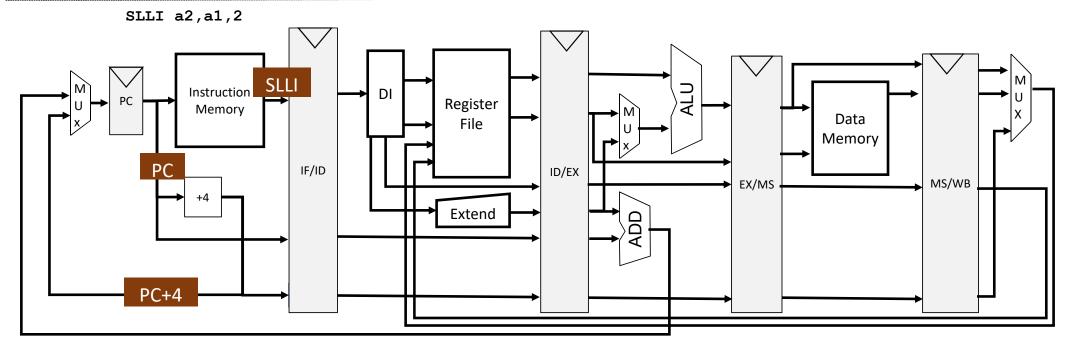

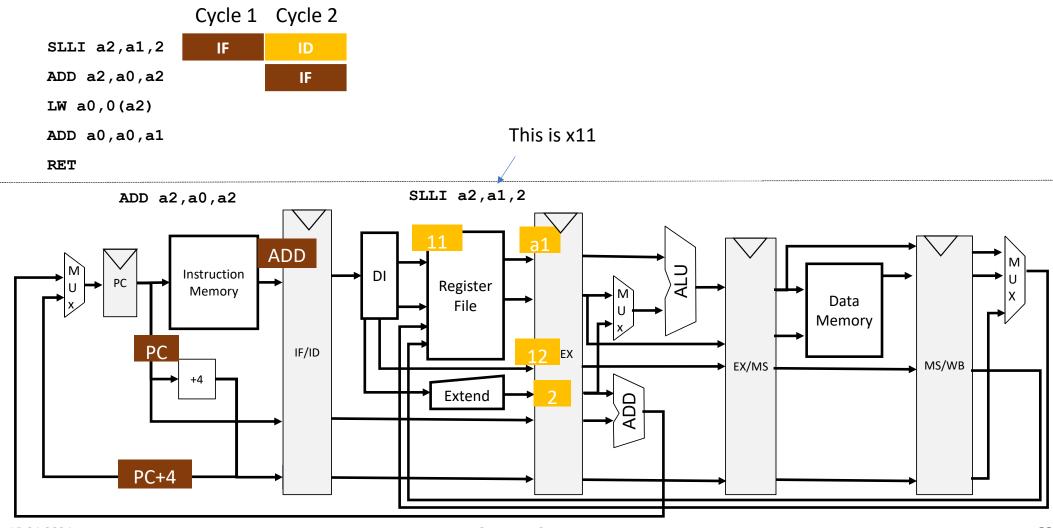

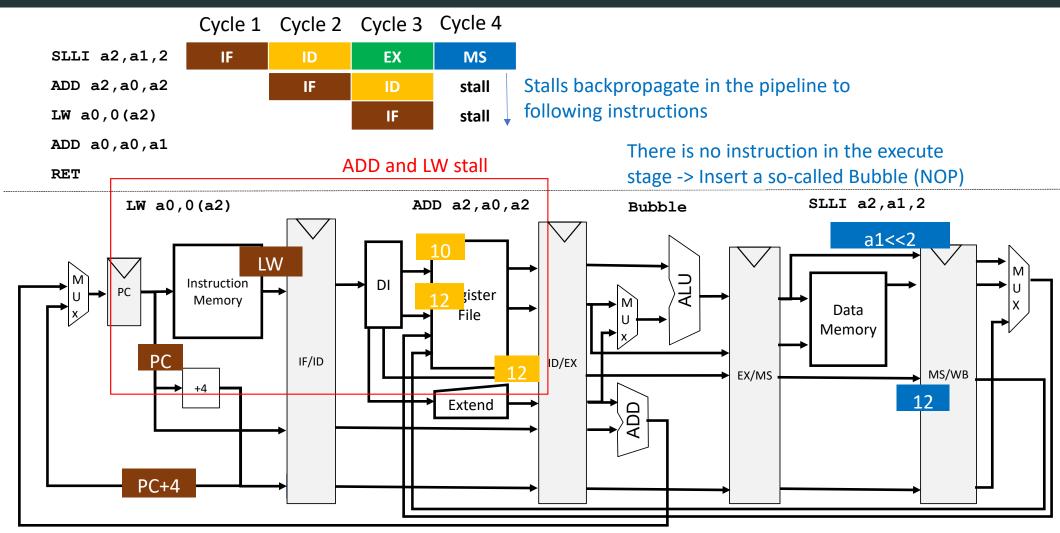

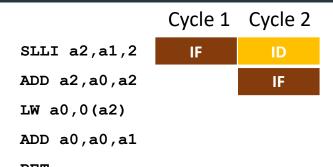

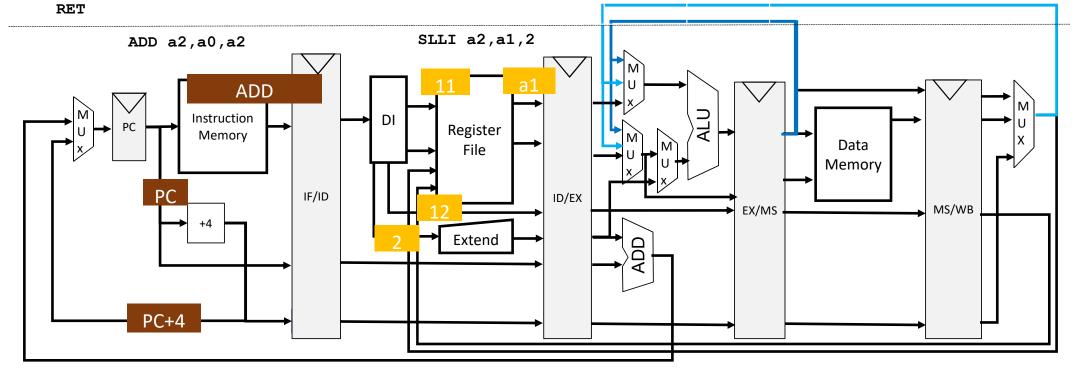

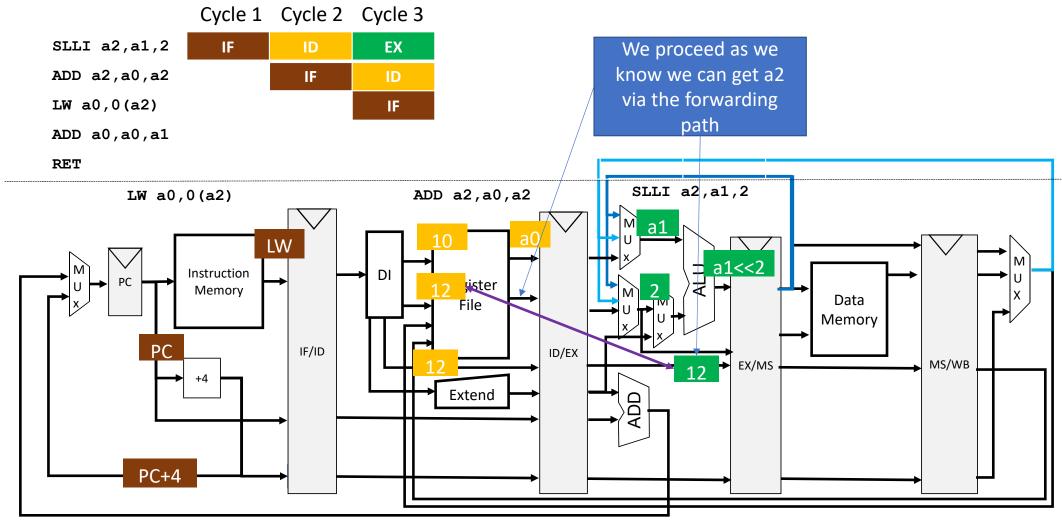

#### Cycle 1

SLLI a2,a1,2

IF

ADD a2,a0,a2

LW a0,0(a2)

ADD a0,a0,a1

RET

Data hazard: a2 not yet updated by SLLI -> Stall ADD because it cannot leave ID stage

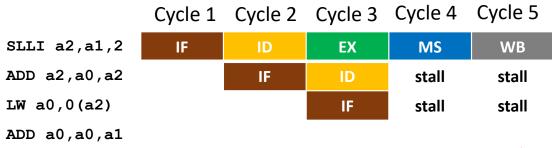

ADD can complete ID stage -> stop stalling

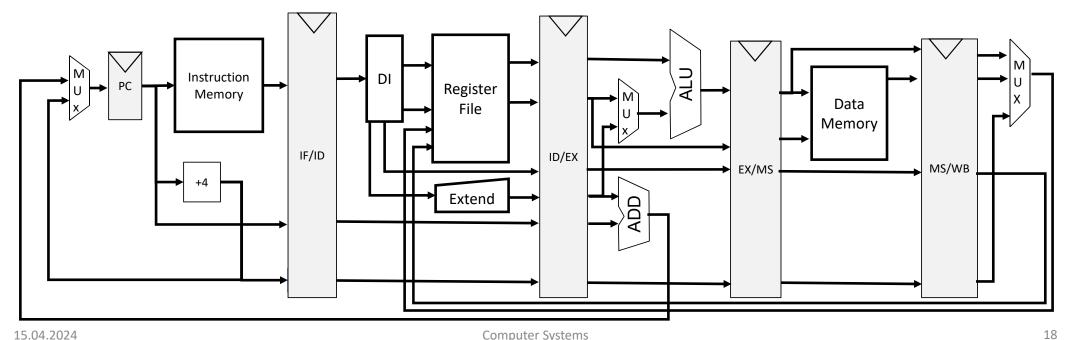

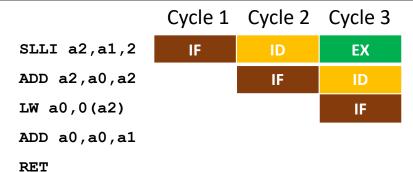

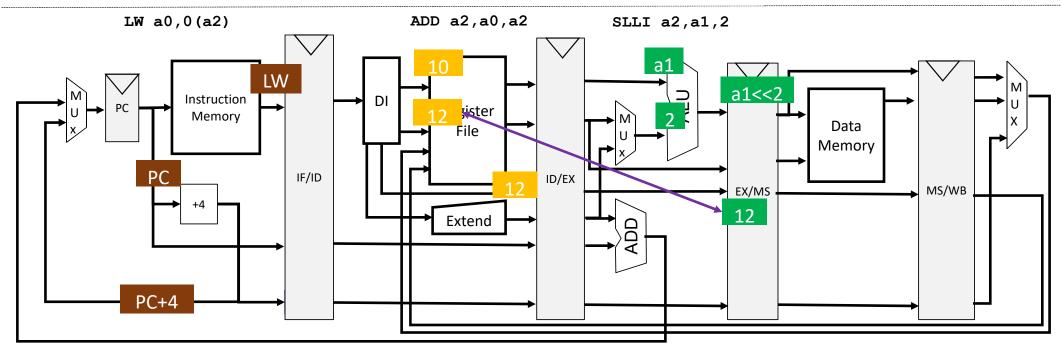

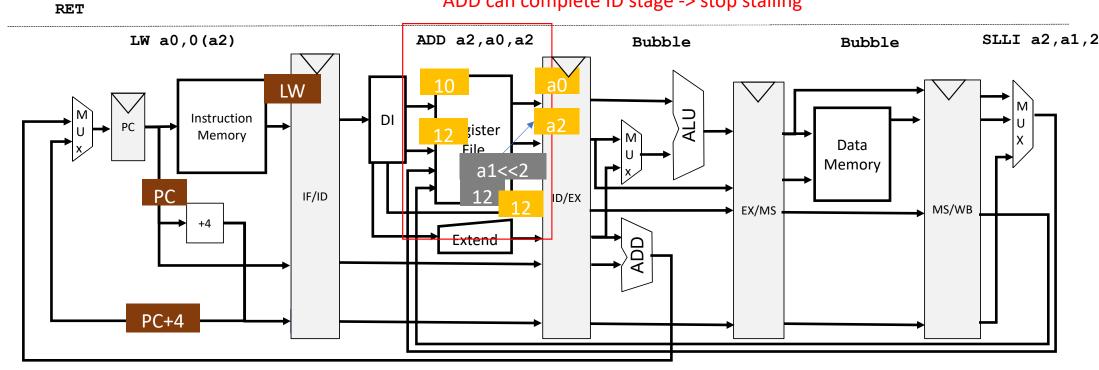

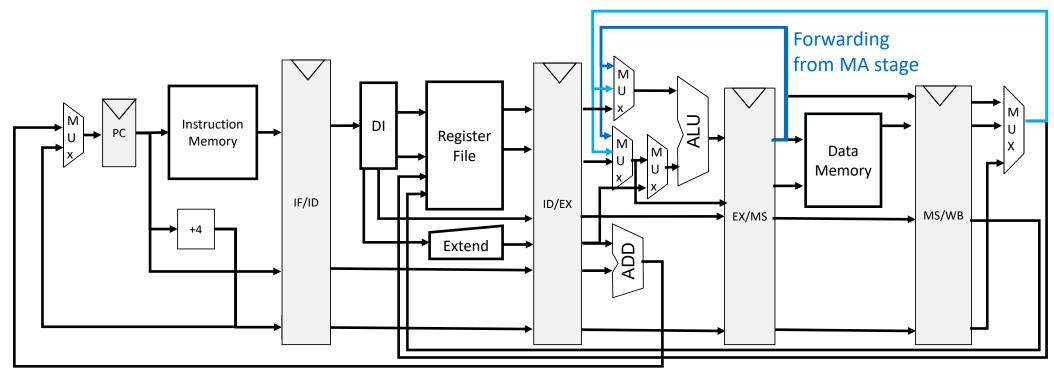

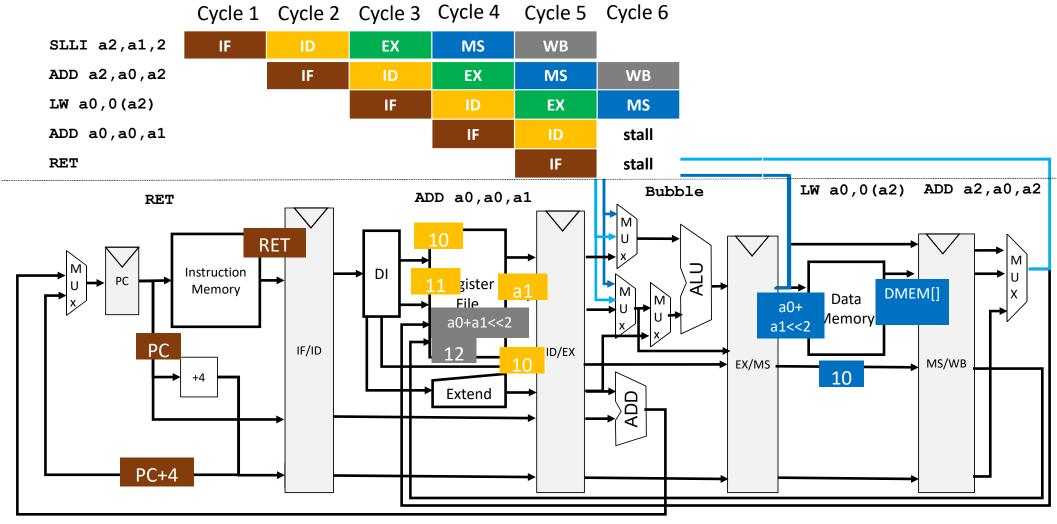

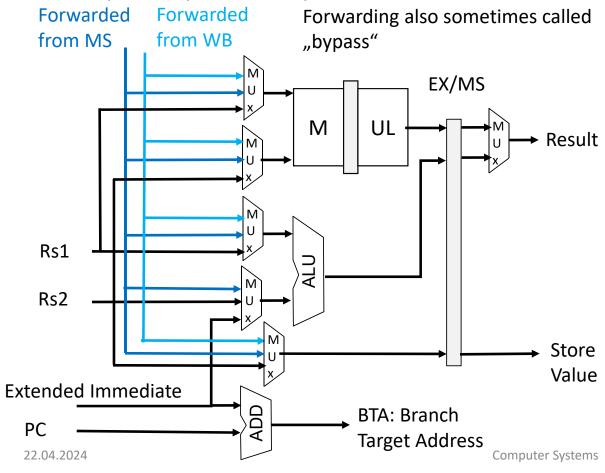

## Five-stage Pipeline with Forwarding Path

- Data hazards can be effectively mitigated using a forwarding path

- While named "forwarding path" the signal buses go "back" in the pipeline

#### Forwarding path from WB stage

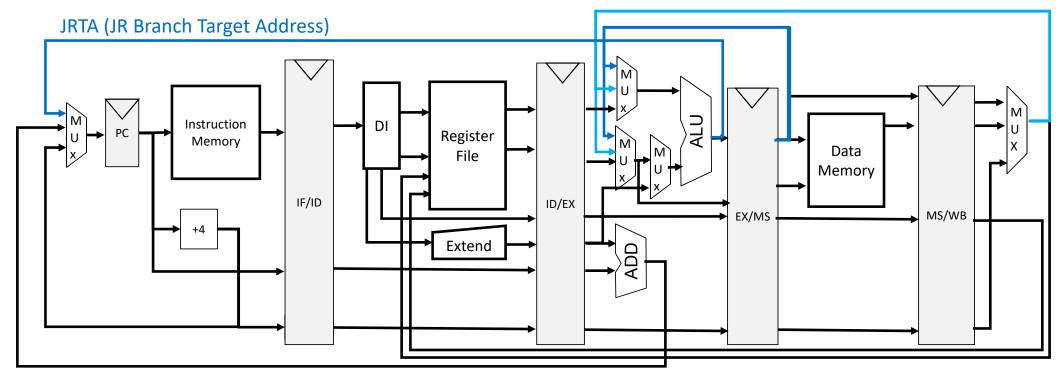

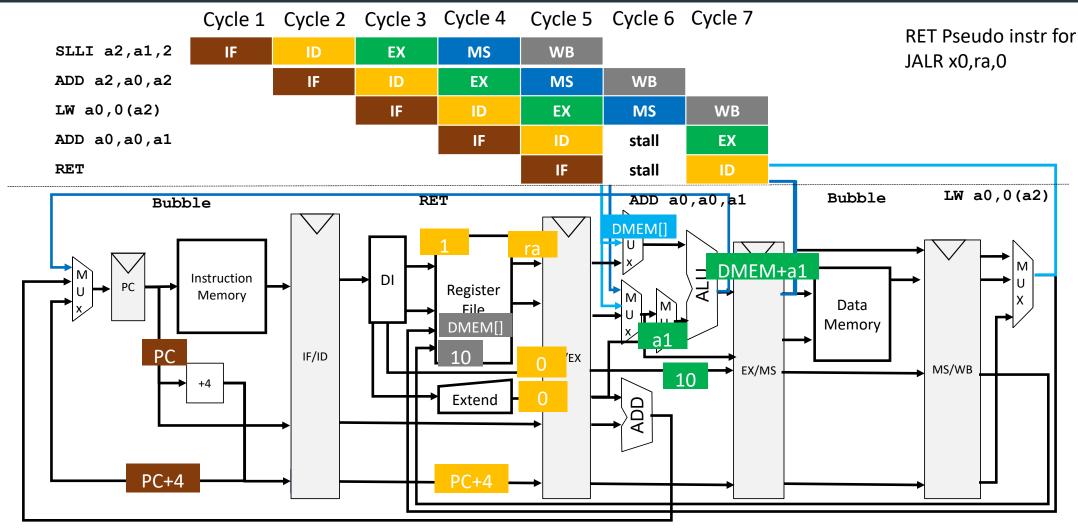

## Five-stage Pipeline with Forwarding Path and JR

- RET is a pseudo-instruction for jump register JR ra, which is a pseudo instruction for JALR x0,ra,0

- The Harris pipeline does not support to load a register value into PC

- We need another bus for implementing the JR instruction

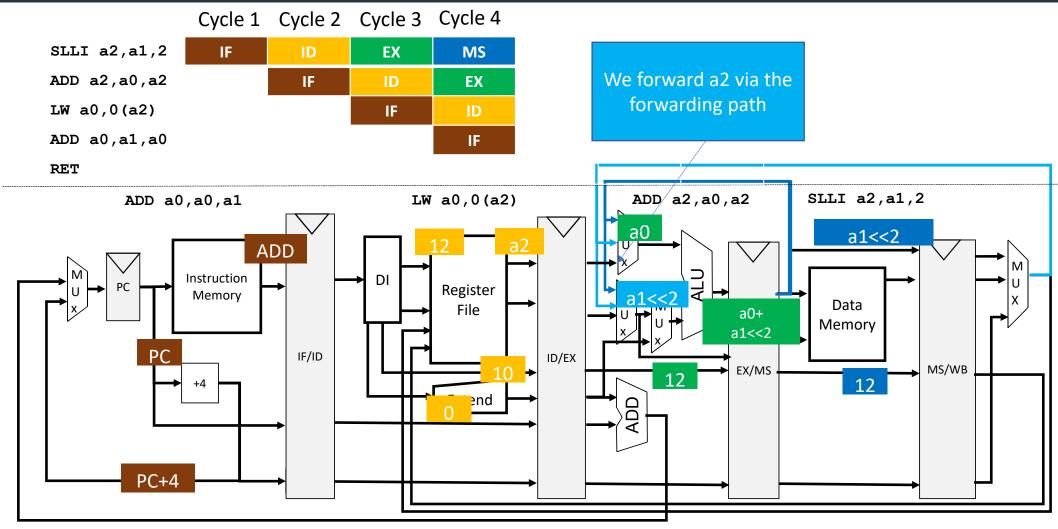

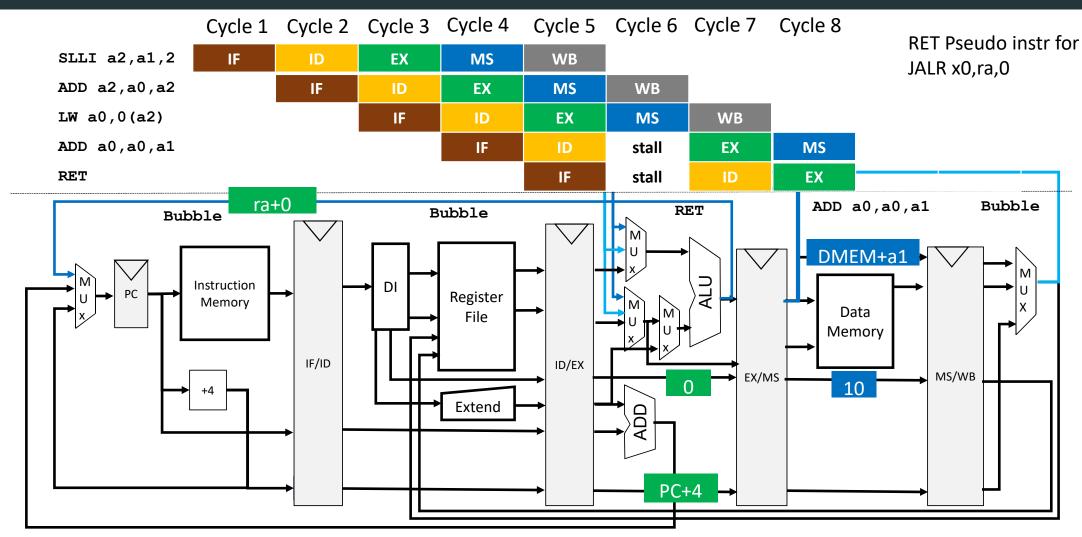

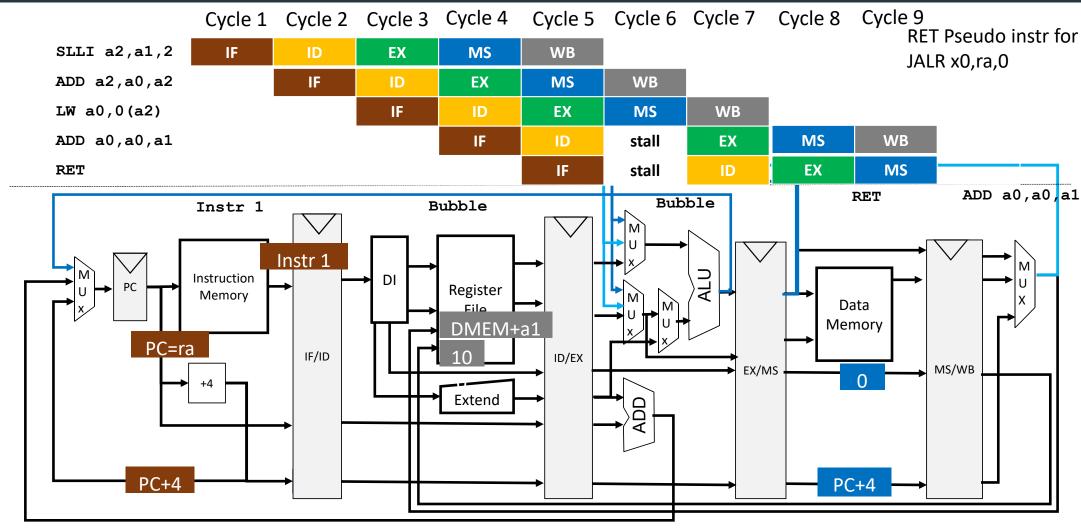

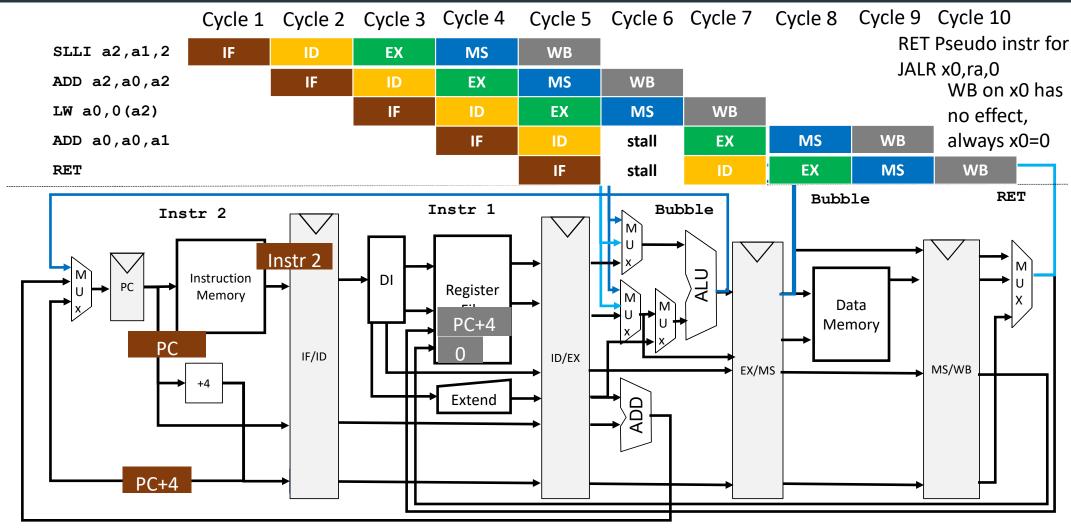

### Five-stage Pipeline with Forwarding Path and JR - Pipeline Execution Diagram

With forwarding path: Possible data hazard after load with penalty of 1 clock cycle (cc)

#### Read After Write (RAW) dependency or "true dependency":

One instructions reads operand that is written as result of previous instructions.

Data hazard prevents the next instruction in the instruction stream from executing during its designated clock cycle.

#### Compiler Instruction Scheduling to Avoid RAW Data Hazards after Load Instructions

- Compiler often can move instructions to avoid RAW data hazards after loads

- Program order must not change (See next session)

- Rarely data hazard penalty observed in five-stage pipeline with forwarding paths

- **≻**Example:

```

vec add for:

vec add for:

LW t1,0(a0) # t1 = a[i]

LW t1,0(a0) # t1 = a[i]

LW t2,0(a1) \# t2 = b[i]

LW t2,0(a1) \# t2 = b[i]

ADDI t0, t0, 1 # i++

RAW 1CC penalty

ADD t1,t1,t2 # t1 = a[i] + b[i]

ADD t1,t1,t2

# t1 = a[i] + b[i]

SW t1,0(a2) # c[i] = t1

SW t1,0(a2) # c[i] = t1

ADDI a0,a0,4 #base address + 4

ADDI a0,a0,4 #base address + 4

ADDI a1,a1,4 #base address + 4

ADDI al,al,4

#base address + 4

ADDI a2,a2,4 #base address + 4

ADDI a2,a2,4

#base address + 4

(...)

ADDI t0,t0,1

# i++

(...)

```

# **Control Hazard**

#### **Control Hazards**

- Control hazards arise from instructions that change the PC

- When the flow of instruction addresses is not sequential

- Unconditional branches (jal, jalr)

- Conditional branches (beg, bne, ...)

- Exceptions

- Possible approaches

- Stall (impacts CPI)

- Move decision point as early in the pipeline as possible (Extra HW)

- Predict and hope for the best!

- **Delay decision** (requires compiler support)

- Control hazards occur less frequently than data hazards,

but there is nothing as effective against control hazards as forwarding is for data hazards

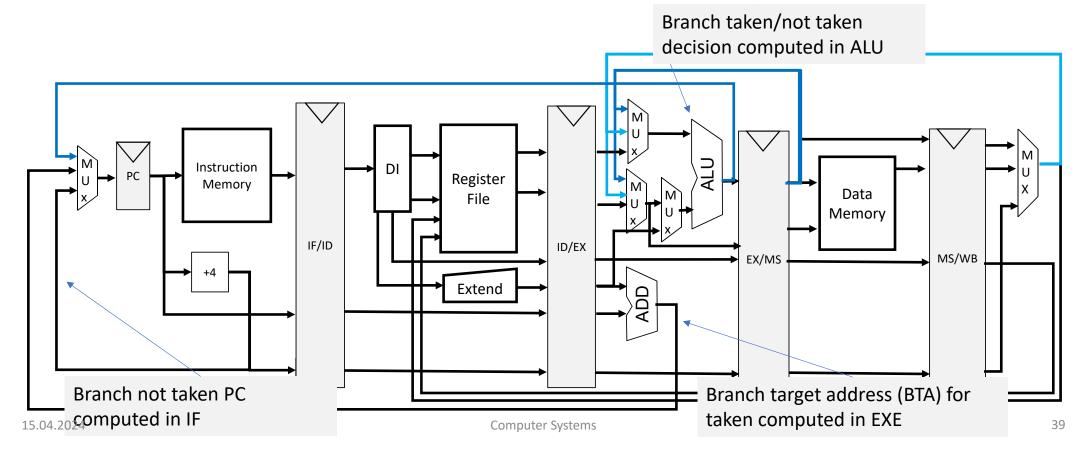

#### Control Hazards – Conditional Branches

- Branch determines flow of control

- Fetching next instruction depends on branch outcome (Branch taken/Not taken)

- Next PC is either PC+4 (branch not taken) or PC+imm<<1 (branch taken)</li>

#### Handling Control Hazards: Stall on Branch

Conservative Approach: Wait until branch outcome determined before fetching next instruction

Conservative approach: Stall immediately after fetching a branch, wait until outcome of branch is known and fetch branch address.

- Reducing Branch Delay:

- E.g. Move Branch Decision to ID Stage: Extra hardware so that we can test registers, calculate

the branch address, and update the PC during the second stage of the pipeline

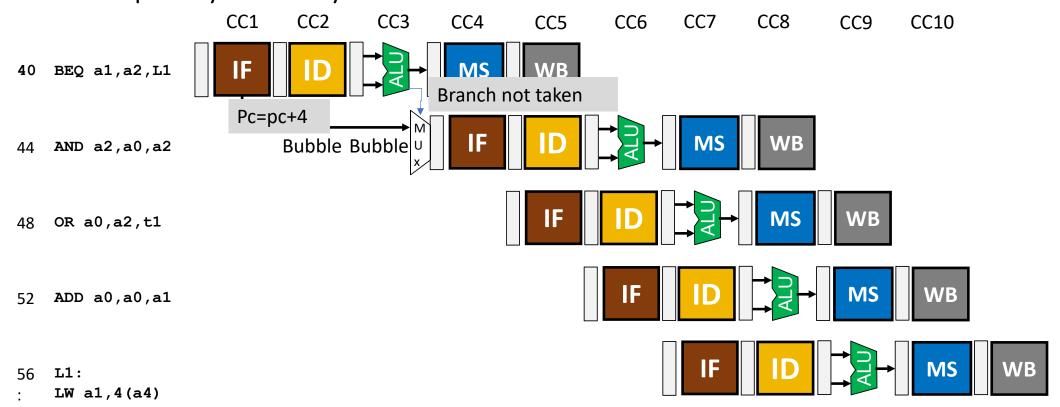

## Handling Control Hazards: Conservative Approach (Branch not Taken)

- Control hazard (branch not taken): stall pipeline until decision known

- Branch penalty: 2 clock cycles

## Handling Control Hazards: Conservative Approach (Branch Taken)

- Control hazard (branch taken): stall pipeline until decision and branch target known

- Branch penalty: 2 clock cycles

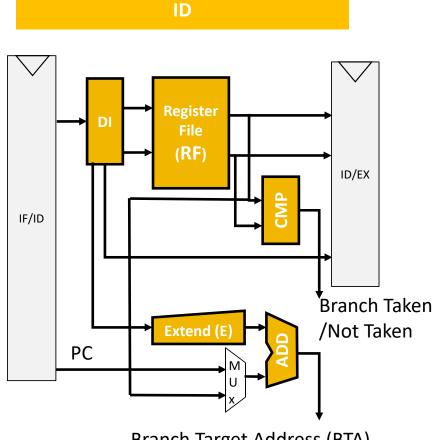

## Reducing Branch Delay - Move Branch Decision to ID Stage

- A lot of branches rely on simple tests (e.g., equality)

- Add hardware to determine outcome of branch in the ID stage

- → Reduce cost of the taken branch

- Subcomputation: Compute Branch Target Address in ID

- Move target address adder from EX to ID

- PC and immediate are already in IF/ID pipeline register

- Subcomputation: Comparison

- Additional register comparator (done before in EX via the ALU)

- Additional Forwarding and Hazard Handling

**Branch Target Address (BTA)**

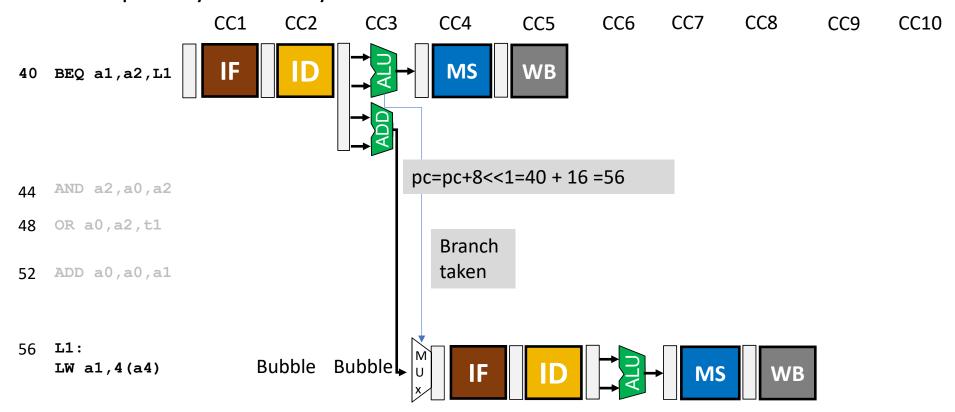

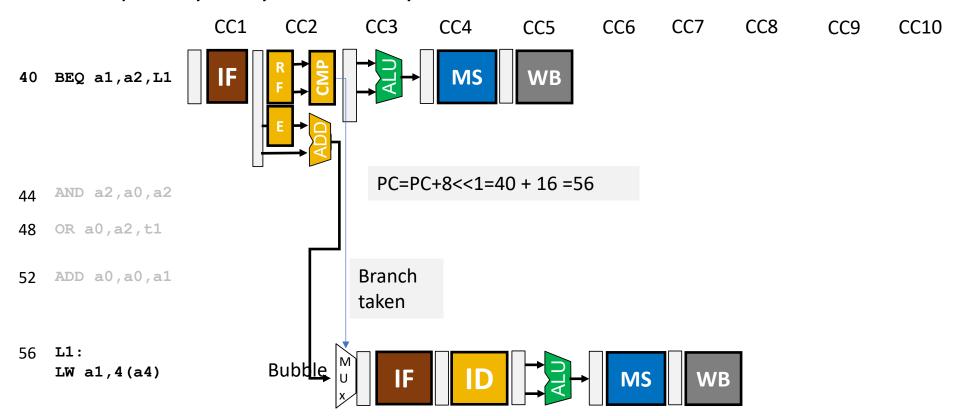

# Reducing Branch Delay - Move Branch Decision to ID Stage - Branch Taken

- Target address adder in ID, Extra comparator to get branch decision in ID

- Branch penalty: Only one clock cycle

# **Static Branch Prediction**

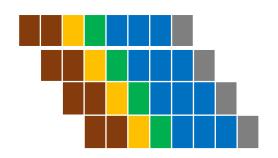

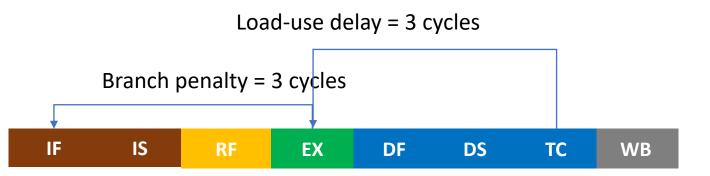

#### Motivation: Branch Prediction

- Longer pipelines can't readily determine branch outcome early

- Branch penalty becomes unacceptable

- Predict outcome of branch

- Only stall if prediction is wrong

- Simple Static Branch Prediction Schemes

- > Always not Taken: Always predict branches not taken Also called fall through (PC=PC+4)

- > Always taken: Always predict branches taken

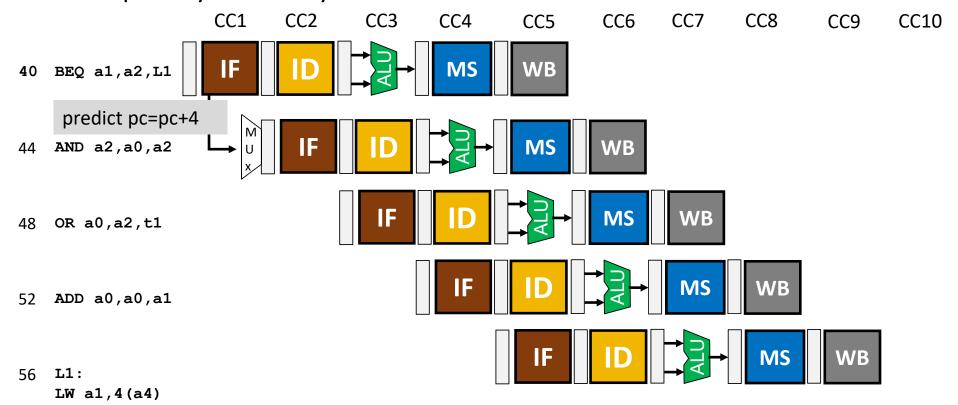

## Always Not Taken – Correct Prediction

- Prediction correct (Branch not taken)

- Branch penalty: 0 clock cycles

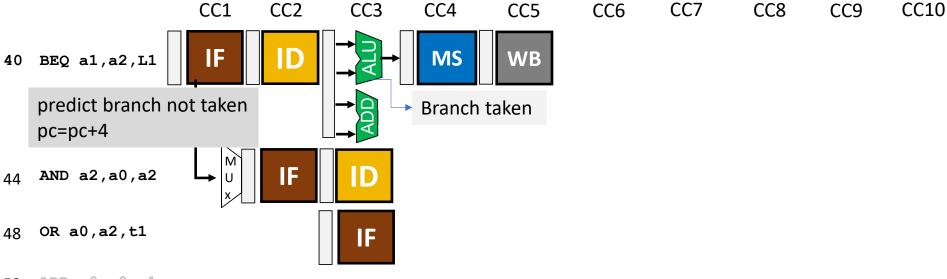

# Always not Taken – Incorrect Prediction (1/2)

- Prediction incorrect (Branch not taken) Flush instructions from pipeline

- Branch penalty: 2 clock cycles

52 ADD a0,a0,a1

56 L1: LW a1,4(a4)

# Always not Taken – Incorrect Prediction (2/2)

- Prediction incorrect (Branch not taken) Flush instructions from pipeline

- Branch penalty: 2 clock cycles

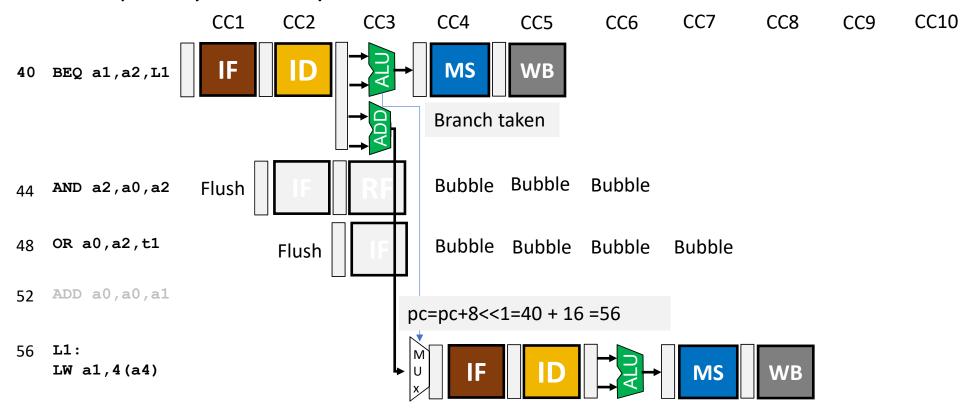

# Always Taken – Correct Prediction

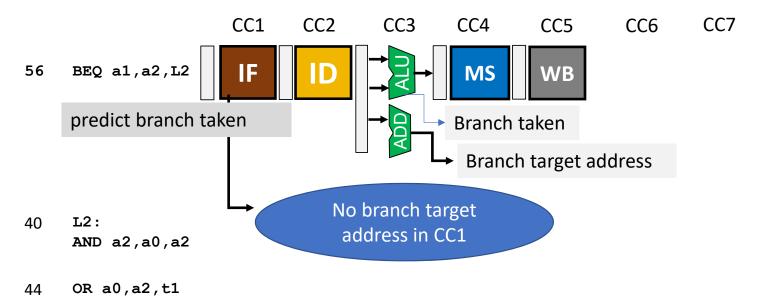

• Prediction (Branch taken) -> Branch target address is computed in EX stage

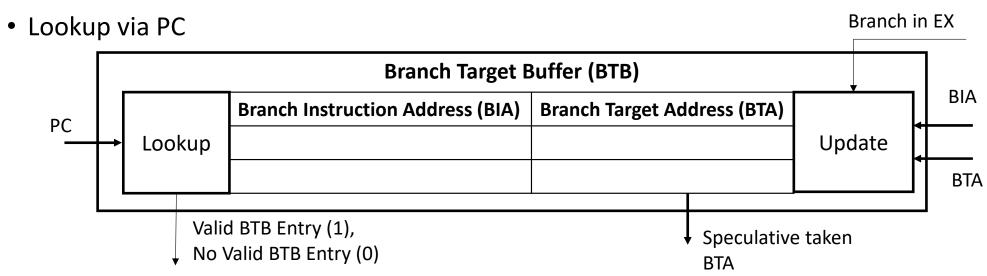

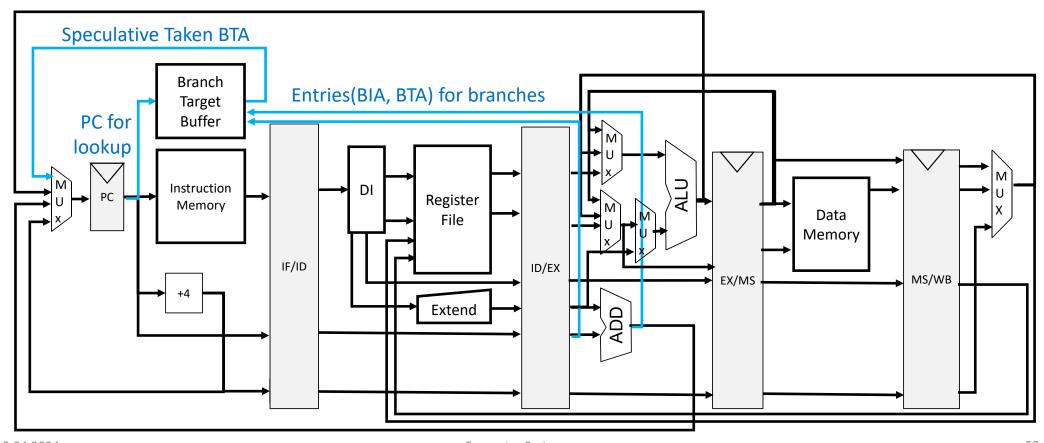

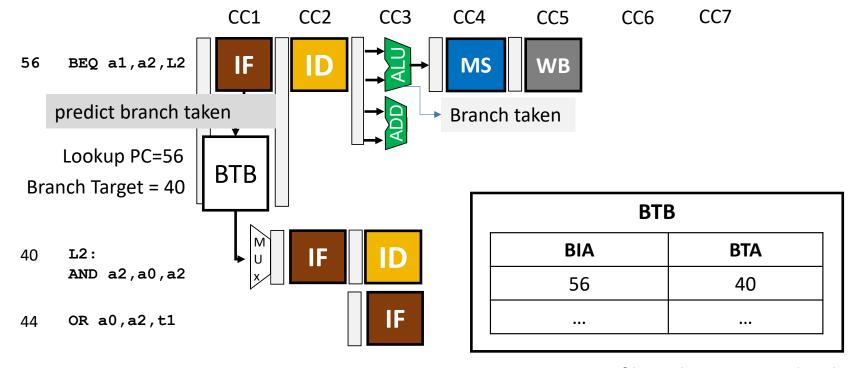

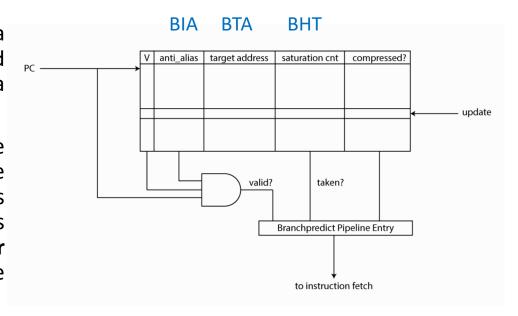

## Branch Target Buffer (BTB)

- Stores the Branch Target Address (BTA) for a certain branch (e.g. identified by its own Branch Instruction Address (BTI))

- Content Addressable Memory (Costly for entries)

- Update policy (similar to caches)

- Entries entered in pairs (BIA, BTA)

- entry not available for first branch execution

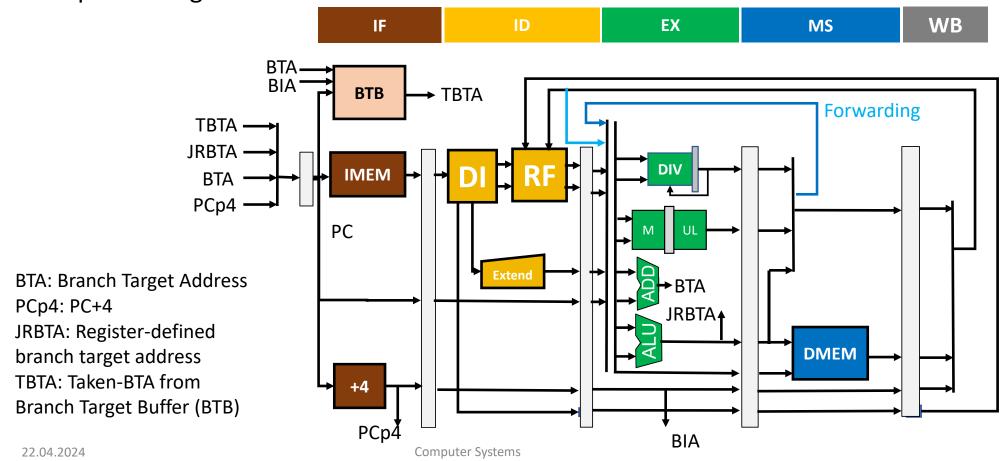

# Five-stage Pipeline with Branch Target Buffer

Only for branches and PC-relative Jumps J, JAL (not JALR, JR, RET)

# Always Taken – Correct Prediction (BTB has entry)

- Prediction (Branch taken) BTA via Branch Target Buffer (BTB)

- Branch penalty: 0 clock cycles

First execution of branch we cannot do a branch taken prediction. Entry was written to BTB on earlier execution of branch with (56,40)

#### **BTFNT:** Enhancing Static Branch Prediction

# Typical Statistics 60% to 70% of branches are taken

#### Example:

- 60% are backward branches (negative offset)

- Loops: Usual more than one iteration (branch will be taken more than once) taken ~90%

- Typical behavior: T T T T...T NT

- About 90% of backward branches are taken

- 40% are forward branches (positive offset)

- If-(Else) Constructs: Branches go forward (jump over code)

- About ~20% of forward branches are taken

- Always not taken:  $(0,6 \cdot 0,9) + (0,4 \cdot 0,2) = 62\%$  mispredictions

- Always taken:  $(0.6 \cdot 0.1) + (0.4 \cdot 0.8) = 38\%$  mispredictions

- Enhanced Static Branch Prediction: Backward Taken, Forward Not Taken (BTFNT)

- Predict forward branches not taken: ~10% mispredictions

- Predict backward branches taken: ~20% mispredictions

- Overall:  $(0.6 \cdot 0.1) + (0.4 \cdot 0.2) = 14\%$  mispredictions

## Effect of Misprediction Rate and Branch Penalty on CPI

#### Program with:

- Relative number of branch instructions (branch rate b)

- The branch cycle penalty **p** for mispredictions

- The branch misprediction rate **m**

- CPI: Cycles per Instructions (data hazards rare so base CPI=1)

$$\mathsf{CPI} = \mathbf{1} + \boldsymbol{b} \cdot \boldsymbol{p} \cdot \boldsymbol{m}$$

Five stage pipeline: b=15%, p=2 Longer pipeline: b=15%, p=5

Always not taken: m=62% -> CPI = 1,186 Always not taken: m=62% -> CPI = 1,465

Always taken: m=38% -> CPI = 1,114 Always taken: m=38% -> CPI = 1,285

BTFNT: m = 14% -> CPI = 1,042 BTFNT: m = 14% -> CPI = 1,105

In longer pipelines, branch penalty is more significant

# **Dynamic Branch Prediction**

## **Dynamic Branch Prediction**

- In longer pipelines, branch penalty is more significant

- Branch prediction buffer (aka branch history table (BHT)) for dynamic prediction

- Stores last outcome (taken/not taken)

- To execute a branch

- ➤ Check table, expect the same outcome

- > Start fetching from fall-through (not taken) or target (taken)

- > In case of misprediction, flush pipeline and flip prediction

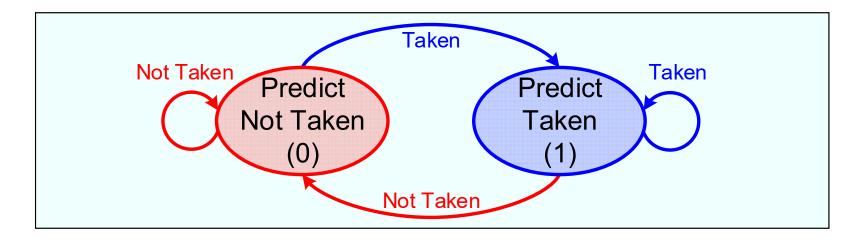

#### Dynamic Branch Prediction: 1-Bit Predictor

- Single-Bit / 1-Bit / Last-Time Predictor

- Indicates which direction the branch went last time it executed

- PNT: Predict NT (Bit=0): Fetch the instruction from (PC+4)

- PT: Predict T (Bit=1): Get target address from the BTB

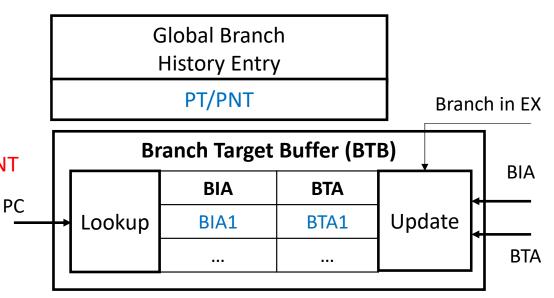

#### **Global Predictor**

- One single Branch History Entry for all branches to save last decision

- Branch reaches IF stage

- Indexed Lookup with PC in BTB

- No valid BTB entry

- -> predict NT (PNT)

- -> Supply PC=PC+4

- Valid BTB entry

- -> Global Predictor result based on BHT: PT/PNT

- -> Supply PC=BTA/PC+4

- Branch reaches EX stage

- Indexed Lookup with PC in BTB

- -> No BTB entry -> Update BTB (create entry)

- -> Eventually only in case that branch is taken

- Update Global Branch History Entry

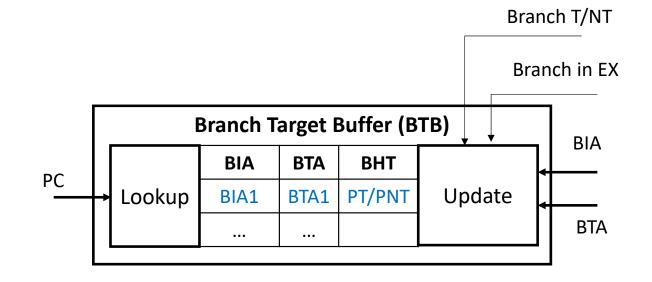

#### **Local Predictor**

• Branch History Table (BHT): One entry for each BTB entry

- Branch in IF stage

- Indexed Lookup with PC in BTB

- No valid BTB entry

- -> predict NT

- -> Supply PC=PC+4

- Valid BTB entry

- -> Local BHT Predictor result T/NT

- -> Supply PC=BTA/PC+4

- Branch in EX stage

- Indexed Lookup with BIA in BTB

- No BTB entry -> Update BTB (create entry), initialize BHB with T/NT

- BTB entry: Update Local BHT with T/NT

## Example Nested Loop Program - Static Branch Prediction

#### • Example Nested Loop Program:

```

for (x = 1024; x > 0; x--)

for (y = 4; y > 0; y--)

do_something(x,y);

```

```

01: li s0, 1024

02: xloop:

03: li s1, 4

04: yloop:

05: mv a0, s0

06: mv a1, s1

07: jal ra, do_something

08: addi s1, s1, -1

09: bnez s1, yloop

10: addi s0, s0, -1

11: bnez s0, xloop

```

Inner Loop (LO9 Branch Pattern): (T-T-T-NT)

Nested Loop Pattern: (T-T-T-NT) T (T-T-T-NT) T (T-T-T-NT) T....

#### **Static Branch Prediction:**

- ➤ Always not taken: ~80% Mispredictions

- > Always taken: ~20% Mispredictions

- > BTFNT (same as always taken): ~20% Mispredictions

# Example Nested Loop Program - Dynamic Branch Prediction (1bit Global)

• Example Nested Loop Program:

```

Inner Loop (LO9 Branch Pattern): (T-T-T-NT)

Nested Loop Pattern: (T-T-T-NT) T (T-T-T-NT) T (T-T-T-NT) T....

```

N=No, Y=Yes Misprediction rate:

```

01: li s0, 1024

02: xloop:

03: li s1, 4

04: yloop:

05: mv a0, s0

06: mv a1, s1

07: jal ra, do_something

08: addi s1, s1, -1

09: bnez s1, yloop

10: addi s0, s0, -1

11: bnez s0, xloop

```

| Branch        | Start | L09 | L09 | L09 | L09 | L11 | L09 | L09 | L09 | L09 | L11 | L09 | L09 |

|---------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| BTB entry L09 | Υ     |     |     |     |     |     |     |     |     |     |     |     |     |

| BTB entry L11 | Y     |     |     |     |     |     |     |     |     |     |     |     |     |

| Global BHT    | PNT   |     |     |     |     |     |     |     |     |     |     |     |     |

| Prediction    | NT    |     |     |     |     |     |     |     |     |     |     |     |     |

| Direction     | -     |     |     |     |     |     |     |     |     |     |     |     |     |

| Correct?      | -     |     |     |     |     |     |     |     |     |     |     |     |     |

# Example Nested Loop Program - Dynamic Branch Prediction (1bit Global)

• Example Nested Loop Program:

```

Inner Loop (LO9 Branch Pattern): (T-T-T-NT)

Nested Loop Pattern: (T-T-T-NT) T (T-T-T-NT) T (T-T-T-NT) T....

```

N=No, Y=Yes Misprediction rate:

```

01: li s0, 1024

02: xloop:

03: li s1, 4

04: yloop:

05: mv a0, s0

06: mv a1, s1

07: jal ra, do_something

08: addi s1, s1, -1

09: bnez s1, yloop

10: addi s0, s0, -1

11: bnez s0, xloop

```

| Branch        | Start | L09 | L09 | L09 | L09 | L11 | L09 | L09 | L09 | L09 | L11 | L09 | L09 |

|---------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| BTB entry L09 | Υ     | Υ   | Υ   | Υ   | Υ   | Υ   |     |     |     |     |     |     |     |

| BTB entry L11 | Y     | Y   | Y   | Y   | Y   | Y   |     |     |     |     |     |     |     |

| Global BHT    | PNT   | PNT | PT  | PT  | PT  | PNT |     |     |     |     |     |     |     |

| Prediction    | NT    | NT  | Т   | Т   | Т   | NT  |     |     |     |     |     |     |     |

| Direction     | -     | Т   | Т   | Т   | NT  | Т   |     |     |     |     |     |     |     |

| Correct?      | -     | Ν   | Υ   | Υ   | N   | N   |     |     |     |     |     |     |     |

# Example Nested Loop Program - Dynamic Branch Prediction (1bit Global)

• Example Nested Loop Program:

Inner Loop (LO9 Branch Pattern): (T-T-T-NT)

Nested Loop Pattern: (T-T-T-NT) T (T-T-NT) T (T-T-T-NT) T....

N=No, Y=Yes

Misprediction rate: ~40% (2 out of five) Repeats

li s0, 1024 02: xloop: 03: li s1, 4 04: vloop: 05: mv a0, s0 06: mv a1, s1 07: jal ra, do something 08: addi s1, s1, -1 09: bnez s1, yloop 10: addi s0, s0, -1 11: bnez s0, xloop

| Branch        | Start | L09 | L09 | L09 | L09 | L11 | L09 | L09 | L09 | L09 | L11 | L09 | L09 |

|---------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| BTB entry L09 | Υ     | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   |     |     |

| BTB entry L11 | Y     | Y   | Υ   | Υ   | Υ   | Υ   | Y   | Y   | Υ   | Υ   | Υ   |     |     |

| Global BHT    | PNT   | PNT | PT  | PT  | PT  | PNT | PT  | PT  | PT  | PT  | PNT |     |     |

| Prediction    | NT    | NT  | Т   | T   | Т   | NT  | Т   | Т   | Т   | Т   | NT  | ••• | ••• |

| Direction     | -     | T   | Т   | T   | NT  | Т   | Т   | Т   | Т   | NT  | Т   |     | ••• |

| Correct?      | -     | N   | Υ   | Υ   | N   | N   | Υ   | Υ   | Y   | N   | N   |     | ••• |

# Example Nested Loop Program - Dynamic Branch Prediction (1bit Local)

• Example Nested Loop Program:

```

Inner Loop (L09 Branch Pattern): (T-T-T-NT)

```

Nested Loop Pattern: (T-T-T-NT) T (T-T-T-NT) T (T-T-T-NT) T....

```

01: li s0, 1024

02: xloop:

03: li s1, 4

04: yloop:

05: mv a0, s0

06: mv a1, s1

07: jal ra, do_something

08: addi s1, s1, -1

09: bnez s1, yloop

10: addi s0, s0, -1

11: bnez s0, xloop

```

#### Misprediction rate:

| Branch        | Start | L09 | L09 | L09 | L09 | L11 | L09 | L09 | L09 | L09 | L11 | L09 | L09 |

|---------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| BTB entry L09 | Υ     |     |     |     |     |     |     |     |     |     |     |     |     |

| BTB entry L11 | Υ     |     |     |     |     |     |     |     |     |     |     |     |     |

| BHT L9        | PNT   |     |     |     |     |     |     |     |     |     |     |     |     |

| BHT L11       | PNT   |     |     |     |     |     |     |     |     |     |     |     |     |

| Prediction    | PNT   |     |     |     |     |     |     |     |     |     |     |     |     |

| Direction     | -     |     |     |     |     |     |     |     |     |     |     |     |     |

| Correct?      | -     |     |     |     |     |     |     |     |     |     |     |     |     |

## Example Nested Loop Program - Dynamic Branch Prediction (1bit Local)

• Example Nested Loop Program:

```

Inner Loop (LO9 Branch Pattern): (T-T-T-NT)

```

Nested Loop Pattern: (T-T-T-NT) T (T-T-T-NT) T (T-T-T-NT) T....

01: li s0, 1024

02: xloop:

03: li s1, 4

04: yloop:

05: mv a0, s0

06: mv a1, s1

07: jal ra, do\_something

08: addi s1, s1, -1

09: bnez s1, yloop

10: addi s0, s0, -1

bnez s0, xloop

Misprediction rate: ~40% (2 out of five)

| Branch        | Start | L09 | L09 | L09 | L09 | L11 | L09 | L09 | L09 | L09 | L11 | L09 | L09 |

|---------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| BTB entry L09 | Υ     | Υ   | Υ   | Υ   | Υ   | Υ   |     |     |     |     |     |     |     |

| BTB entry L11 | Υ     | Υ   | Υ   | Υ   | Υ   | Υ   |     |     |     |     |     |     |     |

| BHT L9        | PNT   | PNT | PT  | PT  | PT  | PNT |     |     |     |     |     |     |     |

| BHT L11       | PNT   | PNT | PNT | PNT | PNT | PNT |     |     |     |     |     |     |     |

| Prediction    | PNT   | NT  | Т   | Т   | Т   | NT  |     |     |     |     |     |     |     |

| Direction     | -     | Т   | Т   | Т   | NT  | Т   |     |     |     |     |     |     |     |

| Correct?      | -     | N   | Y   | Y   | N   | N   |     |     |     |     |     |     |     |

## Example Nested Loop Program - Dynamic Branch Prediction (1bit Local)

• Example Nested Loop Program:

Inner Loop (LO9 Branch Pattern): (T-T-T-NT)

Nested Loop Pattern: (T-T-T-NT) T (T-T-NT) T (T-T-T-NT) T....

01: li s0, 1024

02: xloop:

03: li s1, 4

04: yloop:

05: mv a0, s0

06: mv a1, s1

07: jal ra, do something

08: addi s1, s1, -1

09: bnez s1, yloop

10: addi s0, s0, -1

11: bnez s0, xloop

Misprediction rate: ~40% (2 out of five) Repeats

| Branch        | Start | L09 | L09 | L09 | L09 | L11 | L09 | L09 | L09 | L09 | L11 | L09 | L09 |

|---------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| BTB entry L09 | Υ     | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   |     |     |

| BTB entry L11 | Υ     | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   |     |     |

| BHT L9        | PNT   | PNT | PT  | PT  | PT  | PNT | PNT | PT  | PT  | PT  | PNT |     |     |

| BHT L11       | PNT   | PNT | PNT | PNT | PNT | PNT | PT  | PT  | PT  | PT  | PT  | ••• | ••• |

| Prediction    | PNT   | NT  | Т   | Т   | Т   | NT  | NT  | Т   | Т   | Т   | Т   |     |     |

| Direction     | -     | Т   | Т   | Т   | NT  | Т   | Т   | Т   | Т   | NT  | Т   |     | ••• |

| Correct?      | -     | N   | Υ   | Υ   | N   | N   | N   | Υ   | Υ   | N   | Υ   |     |     |

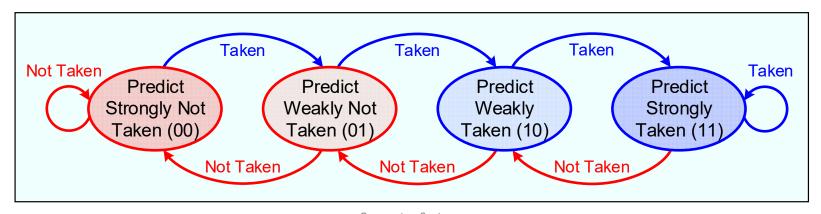

## Improving the 1-Bit Predictor

- **Problem:** A 1-bit predictor changes its prediction from  $T \rightarrow NT$  or  $NT \rightarrow T$  too quickly

- Even though the branch may be mostly taken or mostly not taken

- **Solution Idea:** Add hysteresis to the predictor so that prediction does not change on a single different outcome

- Use two bits to track the history of predictions for a branch instead of a single bit

- Can have 2 states for T or NT instead of 1 state for each

#### 2-Bit Predictor

- Prediction does not change on a single misprediction

- 2-Bit entry in BHT => Four States [2 for NT, 2 for T]

- PSNT: Strongly Not Taken (00), PWNT: Weakly Not Taken (01)

- PWT: Weakly Taken (10), PST: Strongly Taken (11)

- 2-Bit Counter

- Increment by 1 if branch taken, otherwise decrement by 1

- Saturate the counter value at 0 and 3

- A prediction must be wrong twice (consecutively) before the prediction bit is changed

# Example Nested Loop Program - Dynamic Branch Prediction (2bit Global)

• Example Nested Loop Program:

```

Inner Loop (LO9 Branch Pattern): (T-T-T-NT)

Nested Loop Pattern: (T-T-T-NT) T (T-T-T-NT) T (T-T-T-NT) T....

```

N=No, Y=Yes Misprediction rate:

```

01: li s0, 1024

02: xloop:

03: li s1, 4

04: yloop:

05: mv a0, s0

06: mv a1, s1

07: jal ra, do_something

08: addi s1, s1, -1

09: bnez s1, yloop

10: addi s0, s0, -1

11: bnez s0, xloop

```

| Branch        | Start | L09 | L09 | L09 | L09 | L11 | L09 | L09 | L09 | L09 | L11 | L09 | L09 |

|---------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| BTB entry L09 | Υ     |     |     |     |     |     |     |     |     |     |     |     |     |

| BTB entry L11 | Υ     |     |     |     |     |     |     |     |     |     |     |     |     |

| Global BHT    | PWNT  |     |     |     |     |     |     |     |     |     |     |     |     |

| Prediction    | NT    |     |     |     |     |     |     |     |     |     |     |     |     |

| Direction     | -     |     |     |     |     |     |     |     |     |     |     |     |     |

| Correct?      | -     |     |     |     |     |     |     |     |     |     |     |     |     |

# Example Nested Loop Program - Dynamic Branch Prediction (2bit Global)

• Example Nested Loop Program:

```

Inner Loop (LO9 Branch Pattern): (T-T-T-NT)

```

Nested Loop Pattern: (T-T-T-NT) T (T-T-T-NT) T (T-T-T-NT) T....

N=No, Y=Yes

Misprediction rate:

```

01: li s0, 1024

02: xloop:

03: li s1, 4

04: yloop:

05: mv a0, s0

06: mv a1, s1

07: jal ra, do_something

08: addi s1, s1, -1

09: bnez s1, yloop

10: addi s0, s0, -1

11: bnez s0, xloop

```

| Branch        | Start | L09  | L09 | L09 | L09 | L11 | L09 | L09 | L09 | L09 | L11 | L09 | L09 |

|---------------|-------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| BTB entry L09 | Υ     | Υ    | Υ   | Υ   | Υ   |     |     |     |     |     |     |     |     |

| BTB entry L11 | Υ     | Υ    | Υ   | Υ   | Υ   |     |     |     |     |     |     |     |     |

| Global BHT    | PWNT  | PWNT | PWT | PST | PST |     |     |     |     |     |     |     |     |

| Prediction    | NT    | NT   | Т   | Т   | Т   |     |     |     |     |     |     |     |     |

| Direction     | -     | Т    | Т   | Т   | NT  |     |     |     |     |     |     |     |     |

| Correct?      | -     | N    | Υ   | Υ   | N   |     |     |     |     |     |     |     |     |

## Example Nested Loop Program - Dynamic Branch Prediction (2bit Global)

• Example Nested Loop Program:

```

Inner Loop (LO9 Branch Pattern): (T-T-T-NT)

```

Nested Loop Pattern: (T-T-T-NT) T (T-T-NT) T (T-T-T-NT) T....

N=No, Y=Yes

Misprediction rate: ~20% (1 out of five)

Repeats

01: li s0, 1024

02: xloop:

03: li s1, 4

04: yloop:

05: mv a0, s0

06: mv a1, s1

07: jal ra, do\_something

08: addi s1, s1, -1

09: bnez s1, yloop

10: addi s0, s0, -1

11: bnez s0, xloop

| Branch        | Start | L09  | L09 | L09 | L09 | L11 | L09 | L09 | L09 | L09 | L11 | L09 | L09 |

|---------------|-------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| BTB entry L09 | Υ     | Υ    | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   | Υ   |     |     |

| BTB entry L11 | Υ     | Υ    | Υ   | Υ   | Υ   | Y   | Y   | Y   | Υ   | Υ   | Υ   |     |     |

| Global BHT    | PWNT  | PWNT | PWT | PST | PST | PWT | PST | PST | PST | PST | PWT |     |     |

| Prediction    | NT    | NT   | Т   | Т   | Т   | Т   | Т   | Т   | Т   | Т   | Т   |     | ••• |

| Direction     | -     | Т    | Т   | Т   | NT  | Т   | Т   | Т   | Т   | NT  | Т   |     |     |

| Correct?      | -     | N    | Υ   | Υ   | N   | Υ   | Υ   | Υ   | Υ   | N   | Υ   |     |     |

#### **2-bit Predictor: Limits**

- Still penalty on regular patterns:

- Recap: Inner loop iterations: T-T-T-NT

- Branches often show such regular patterns

- Can we incorporate this regularity? -> Use a history

- Two-level-history adaptive branch predictors (many variants \*)

- Learn the history and loop pattern T-T-T-NT

- They usually can have higher accuracy

- This is still 90ties technology \*

\*Tse-Yu Yeh and Y. N. Patt, "A Comparison Of Dynamic Branch Predictors That Use Two Levels Of Branch History," *Proceedings of the 20th Annual International Symposium on Computer Architecture*, San Diego, CA, USA, 1993

- Modern branch predictors for complex processors

- Based on neural networks

- Learn patterns, history and interrelation between branches

- Can achieve very small misprediction rates

Optional, not relevant for exam

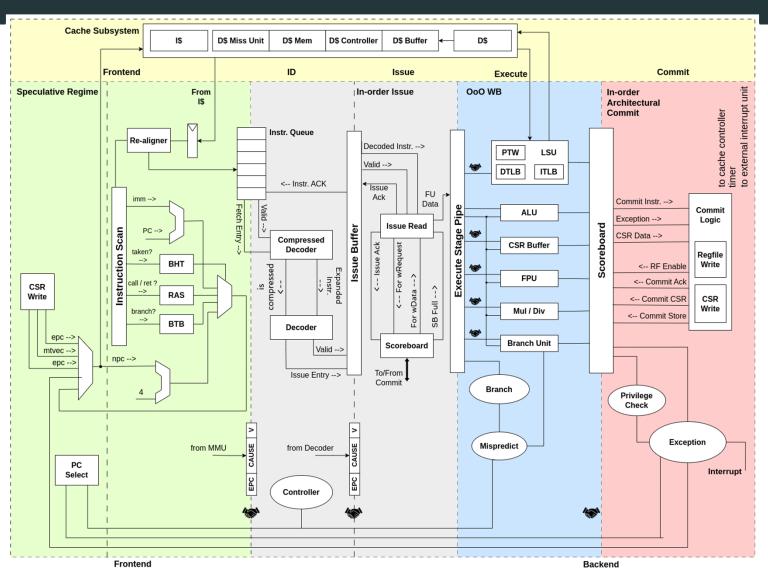

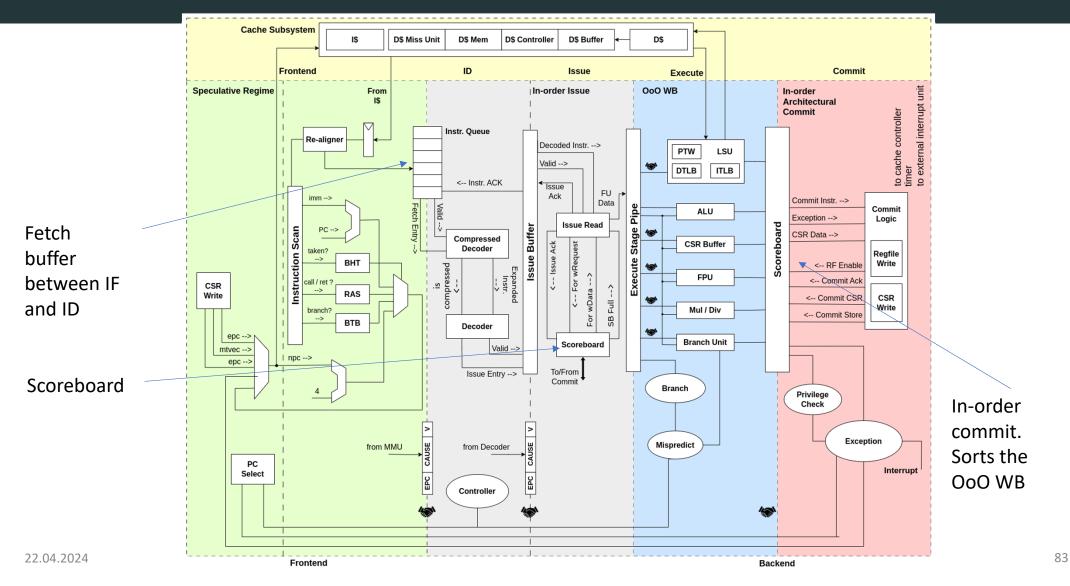

### A Look at a Real Processor – CVA6

"CVA6 is a RISC-V compatible application processor core that can be configured as a 32- or 64-bit core: CV32A6 and CV64A6".

--- CVA& User Manual

https://docs.openhwgroup.org/projects/cva6-user-manual/01\_cva6\_user/Introduction.html

Developed initially as part of PULP project (ETH Zürich), now maintained by the OpenHW Group

#### **CVA6 Branch Predictor**

"Branch Predict: If the BHT and BTB predict a branch on a certain PC, PC Gen sets the next PC to the predicted address and also informs the IF stage that it performed a prediction on the PC. (...)"

"All branch prediction data structures reside in a single register-file like data structure. It is indexed with the appropriate number of bits from the PC and contains information about the predicted target address as well as the outcome of a **configurable-width saturation counter** (two by default). The prediction result is used in the subsequent stage to jump (or not)."

-- CVA6 Design Document (deprecated) – Branch Prediction (05.04.2024) https://docs.openhwgroup.org/projects/cva6-user-manual/03 cva6 design/pcgen stage.html

Optional, not relevant for exam

### A Look at a Real Processor – ESP32-C3

ESP32-C3 Technical Reference Manual

https://www.espressif.com/sites/default/files/documentation/esp32-c3\_technical\_reference\_manual\_en.pdf#riscvcpu

#### Low Power Mikro-Controller – ESP32-C3

Picture: Alibaba-Costs less than 1€ Scalar in-order processors with five or less pipeline stages are used in low-cost **micro-controller-type** devices.

"ESP-RISC-V CPU is a 32-bit core based upon RISC-V ISA comprising base integer (I), multiplication/division (M) and compressed (C) standard extensions. The core has **4-stage**, **in-order**, **scalar pipeline** optimized for area, power and performance. (...)"

-- ESP32-C3 Technical Reference Manual https://www.espressif.com/sites/default/files/documentation/esp32-c3 technical reference manual en.pdf#riscvcpu

### Optional, not relevant for exam

## Trap Handling

### Terminology

- Terminology is used often different for different architectures (x86,ARM, RISCV,...).

- For RISC-V:

- "We use the term **exception** to refer to an unusual condition occurring at run time associated with an instruction in the current RISC-V hart."

- "We use the term **interrupt** to refer to an external asynchronous event that may cause a RISC-V hart to experience an unexpected transfer of control."

- "We use the term **trap** to refer to the transfer of control to a trap handler caused by either an exception or an interrupt."

- —- Volume 1, Unprivileged Specification version 20191213: https://riscv.org/technical/specifications/

### Trap Handling

- For a function call the compiler assures that the function call standard of the ABI is kept

- An exception and interrupt can happen during execution of a function ceither due to an instruction (e.g. memory access error) or due to an external event (device raises an interrupt)

- For a trap, we are in the middle of execution of a function and must save the context of the current execution before calling a trap handler to handle the exception or interrupt

- RISC-V has certain so-called Control Status Registers (CSRs) to identify the cause of a trap

### Causes for Traps

| Interrupt | Exception Code | Description                    |

|-----------|----------------|--------------------------------|

| 1         | 0              | Reserved                       |

| 1         | 1              | Supervisor software interrupt  |

| 1         | 2              | Reserved                       |

| 1         | 3              | Machine software interrupt     |

| 1         | 4              | Reserved                       |

| 1         | 5              | Supervisor timer interrupt     |

| 1         | 6              | Reserved                       |

| 1         | 7              | Machine timer interrupt        |

| 1         | 8              | Reserved                       |

| 1         | 9              | Supervisor external interrupt  |

| 1         | 10             | Reserved                       |

| 1         | 11             | Machine external interrupt     |

| 1         | 12-15          | Reserved                       |

| 1         | ≥16            | Designated for platform use    |

| 0         | 0              | Instruction address misaligned |

| 0         | 1              | Instruction access fault       |

| 0         | 2              | Illegal instruction            |

| 0         | 3              | Breakpoint                     |

| 0         | 4              | Load address misaligned        |

| 0         | 5              | Load access fault              |

| 0         | 6              | Store/AMO address misaligned   |

| 0         | 7              | Store/AMO access fault         |

| 0         | 8              | Environment call from U-mode   |

| 0         | 9              | Environment call from S-mode   |

| 0         | 10             | Reserved                       |

| 0         | 11             | Environment call from M-mode   |

| 0         | 12             | Instruction page fault         |

| 0         | 13             | Load page fault                |

| 0         | 14             | Reserved                       |

| 0         | 15             | Store/AMO page fault           |

| 0         | 16–23          | Reserved                       |

| 0         | 24-31          | Designated for custom use      |

| 0         | 32-47          | Reserved                       |

| 0         | 48-63          | Designated for custom use      |

| 0         | ≥64            | Reserved                       |

—- Volume 2, Privileged Specification version 20211203: <a href="https://riscv.org/technical/specifications/">https://riscv.org/technical/specifications/</a>

Word trap is mentioned 301 times

Different architectures treat exceptions differently e.g. division by zero is not raising an exception in RISC-V

### Trap Handling Basics

- Trap is detected.

- Change mode

- Jump to trap handler

- Trap handler saves context

- Trap handler identifies cause (exception/interrupt)

- Corresponding exception/interrupt handler is called

- Some handlers do not return if they can not recover from an exception

- Trap handler restores context

- Change mode

- Jump back to program execution

### Precise vs. Imprecise traps

- Precise traps:

- Associated with a certain instruction (e.g. illegal instruction exception)

- Easier to debug

- Imprecise trap:

- Not associated with an instruction

- Hard to debug

- OR: Pipelined execution makes it hard to associate the exception with an instruction (This is an issue with certain pipelines, which we see in next lecture)

## Summary

#### Where we are

- Five-Stage Scalar In-order Processor Pipeline

- Forwarding to mitigate data hazards

- Branch prediction to mitigate control hazards

- In-order pipeline

- Five Stages

- Scalar pipeline: CPI >= 1

• Upcoming Lecture: Multi-cycle Functional Units (DIV/MUL) and Out-of-Order (OoO)

## Thank you for your attention!

## **BACKUP**

### Registers of RISC-V

- RISC-V has 32 integer registers

- Processors can have different register width, we look at RV32 with 32-bit width

- Each register has two IDs (x0x31) and an ABI name that indicates its role

- ABI stands for Application Binary Interface (ABI)

| Register | ABI Name | Description                             | Saver  |  |  |

|----------|----------|-----------------------------------------|--------|--|--|

| хО       | Zero     | Hard-wired zero                         | -      |  |  |

| x1       | ra       | Return address                          | Caller |  |  |

| x2       | sp       | Stack pointer                           | Callee |  |  |

| х3       | gp       | Global pointer                          | -      |  |  |

| x4       | tp       | Thread pointer                          | -      |  |  |

| х5-7     | t0-2     | Temporaries                             | Caller |  |  |

| x8       | s0,fp    | Saved<br>register/frame<br>pointer      | Callee |  |  |

| х9       | s1       | Saved Register                          | Callee |  |  |

| x10-11   | a0-1     | Function<br>arguments,<br>Return values | Caller |  |  |

| x12-17   | a2-7     | Function arguments                      | Caller |  |  |

| x18-27   | s2-11    | Saved registers                         | Callee |  |  |

| x28-31   | t3-6     | Temporaries                             | Caller |  |  |

### Application Binary Interface (ABI) – Function Call Convention

- ABI also specifies rules for register usage in passing arguments and results for function calls

- Callee-saved registers: If function foo1 (caller) calls foo2 (callee), then foo2 is not allowed to modify this value (it needs to save it and restore it before returning to foo1)

- Caller-saved registers: If function foo1 (caller) calls foo2 (callee), then foo1 needs to save

this register before calling foo2 if it wants to keep the value in it because foo1 is allowed to

modify it

- According to ABI parameters are passed to a function in registers a0-a7

- The function should return its return value in register a0 (if <=32-bit value)</li>

#### **RISC-V Instructions**

- The RISC-V ISA is modular with base instruction sets and a large variation of extensions

- We look at RV32IM

- 32-bit Integer Instruction Set RV32I

- Integer Register-Register Instructions (R-type)

- Runs an arithmetic or logical operation on registers

- Both operands are values in registers

- Integer Register-Immediate Instructions (I-type)

- Second operand is an immediate (constant) value

- Control Transfer Instructions

- Unconditional jumps

- Conditional Branches

- Load Store Instructions

- Move data between memory and registers

- Load-store Architecture: Operations on registers only

- 32-bit Integer Multiplication RV32M Extension -> Next Session

- Integer Multiplication Instructions

- Integer Division Instructions

### **Computer Systems**

**Advanced Processor Pipelines 2**

Daniel Mueller-Gritschneder

22.04.2024 V04g

#### Sources

This book covers the basics of how to design a simple in-order scalar processor pipeline in detail in hardware.

- Literature: "Digital Design and Computer Architecture: RISC-V Edition", by Sarah L. Harris and David Harris

- https://shop.elsevier.com/books/digital-design-and-computer-architecture-risc-v-edition/harris/978-0-12-820064-3

- https://pages.hmc.edu/harris/ddca/ddcarv.html (Includes resources for students!)

- They also provide slideshows the basis for ours! You can investigate extended version at their website.

- Available at TU's library: <a href="https://catalogplus.tuwien.at/permalink/f/qknpf/UTW">https://catalogplus.tuwien.at/permalink/f/qknpf/UTW</a> alma21139903990003336

#### Sources

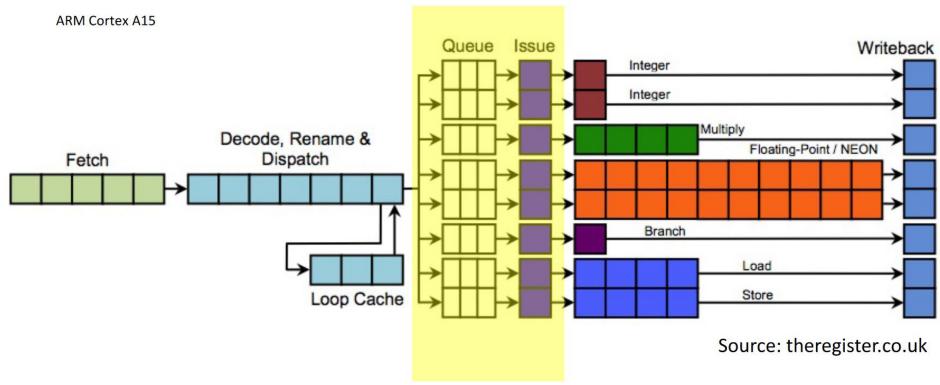

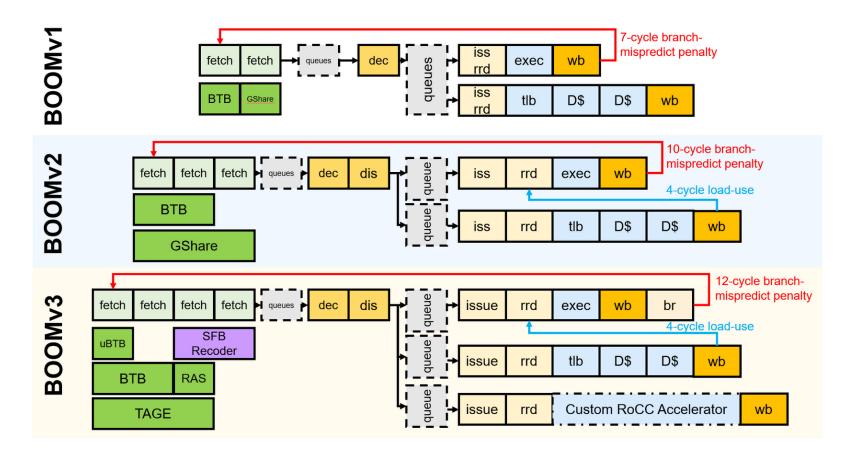

So-called application processors have many additional features: Branch prediction, Out of order execute, Scoreboard, Superpipelining, Multi-issue, Superscalar, VLIW, Multi-threading, ...

**Disclaimer**: The book provides advanced concepts from real complex processor designs. We only study the concepts at a high level. For simplicity, the used pipeline models in this lecture are reduced strongly in complexity.

But: We will have a look at some current RISC-V processor designs

Literature: "Computer Architecture A Quantitative Approach" 5th Edition - September 16, 2011 Authors: John L. Hennessy, David A. Patterson eBook ISBN: 9780123838735

- <a href="https://shop.elsevier.com/books/computer-architecture/hennessy/978-0-12-383872-8">https://shop.elsevier.com/books/computer-architecture/hennessy/978-0-12-383872-8</a>

- Available at TU's library: https://catalogplus.tuwien.at/permalink/f/8agg25/TN cdi askewsholts vlebooks 9780123838735

### RECAP: Five-Stage In-Order Scalar Pipeline

- Five Stage

- In-order pipeline

Each stage takes one cycle to complete

- Scalar pipeline

- Single access cycle to instruction and data memory: Works for small and slow micro-controller-type processors with on-chip embedded SRAM memories

- ➤ Single cycle operations, works for simple instructions (ADD, Compare,...)

Scalar processor: Can execute at maximum 1 instruction per cycle (IPC <=1)</li>

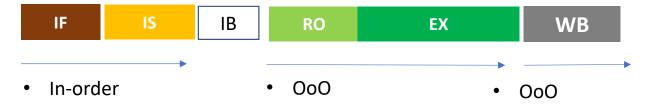

#### Content

- Multi-cycle Functional Units (FUs)

- Load and Store Optimizations

- Instruction Dependencies (RAW, WAW, WAR)

- Dynamic Scheduling with Scoreboard (Out of Order OoO)

- Register Renaming

- Superscalar

- A look at a real RISC-V processor: CVA6

- Pipeline Support for Precise Traps

Optional, not relevant for exam

## **Multi-Cycle Operations**

### Integer Multiplication Instructions

- Signed-signed Multiplication

- Multiplying two 32bit values can result in a value of up to 64 bit

- MUL a3,a1,a2

- Behavior: a3 ← a1\*a2 // only the lower 32bit

- MULH a4,a1,a2

- Behavior: a4 ← a1\*a2 // only the higher 32bit

- Example:

- MULH a4,a1,a2

- MUL a3,a1,a2

Behavior: [a4 a3] = a1\*a2 // full 64 bit

- Unsigned-unsigned multiplication MULHU

- Signed-Unsigned multiplication MULHSU

### **Integer Division Instructions**

- Signed-signed Division

- DIV a3,a1,a2

- Behavior: a3 ← a1 / a2

- REM a4, a1, a2

- Behavior: a4 ← a1 modulo a2 // remainder

- Unsigned-unsigned division DIVU, REMU

### Pipelined Functional Units (FUs)

- Complex computations require deep circuit logic

- Critical path in deep logic limits the design's frequency

- Similar to processor design, break FU into stages and integrate registers to build a pipeline

- > Latency (in cycles) equals to number of pipeline stages

- > Initialization Interval: Delay (in cycles) between start of two computations

• Example: 2-stage Multiplier

MUL a0,a0,t0

MUL a1, a1, t1

MUL a2, a2, t2

Stage Stage

Latency = 2 Cycles

Initialization Interval = 1 Cycle

Cycle 1 Cycle 2 Cycle 3 Cycle 4

MUL(s1) MUL(s2)

MUL(s1) MUL(s2)

MUL(s1) MUL(s2)

MUL(s1) MUL(s2)

Initialization

Interval Latency

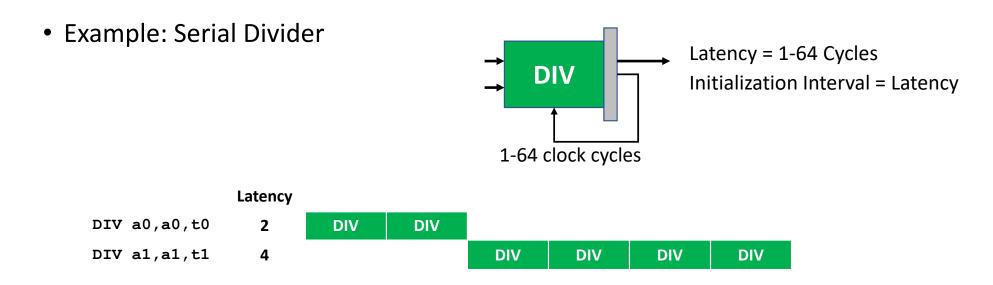

### Serial Functional Units (FUs)

- Often complex operations such as divisions can be computed by iterative algorithms

- The number of iterations (required clock cycles) often depends on the input values

- These iterations can be implemented on a serial FU, which is busy as long as it computes

- > Latency equals to number of cycles required for computation

- > Initialization Interval equals to number of cycles required for computation

### Example: RISC-V CVA6 Processor

### "Multiplier

The multiplier contains a division and multiplication unit. Multiplication is performed in two cycles and is fully pipelined (re-timing needed). The division is a simple serial divider which needs 64 cycles in the worst case."\*

\*https://docs.openhwgroup.org/projects/cva6-user-manual/03\_cva6\_design/ex\_stage.html

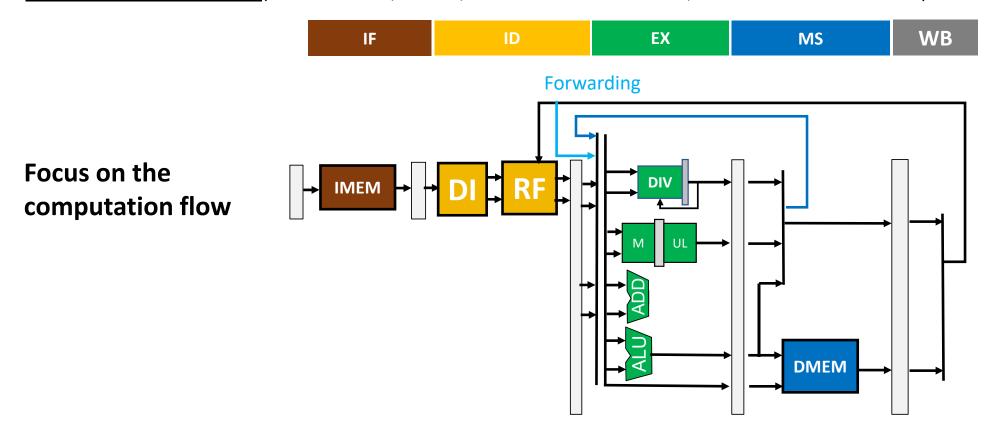

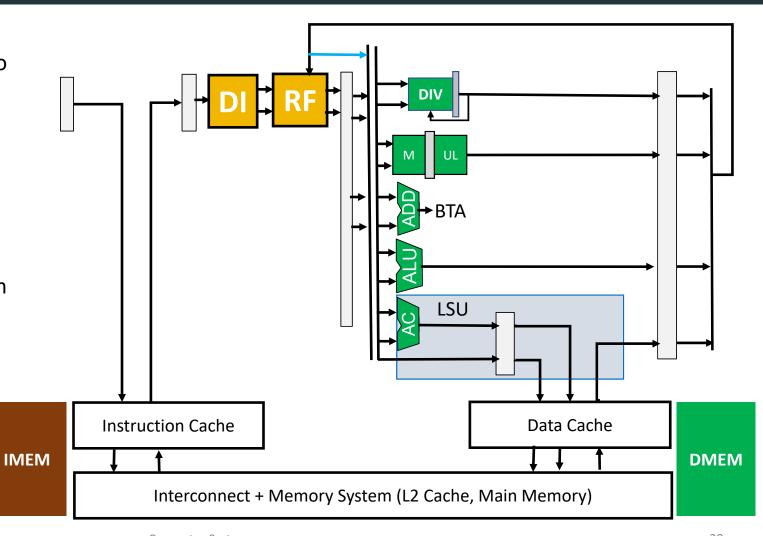

### Integration of Multi-cycle Functional Units

- Multi-cycle Functional Units are integrated into the EX stage

- Example only for Multiplier

# Simplified Illustration Style for Multiplexing

### Scalar Five-Stage Pipeline with Multi-cycle FUs and Forwarding

- Multi-cycle Functional Units are integrated into the EX stage

- Simplified diagram

13

### Scalar Five-Stage Pipeline with Multi-cycle FUs and Forwarding

- Multi-cycle Functional Units are integrated into the EX stage

- Further simplified diagram (PC Generation, Extend, PC+rd address not shown, but of course still needed!)

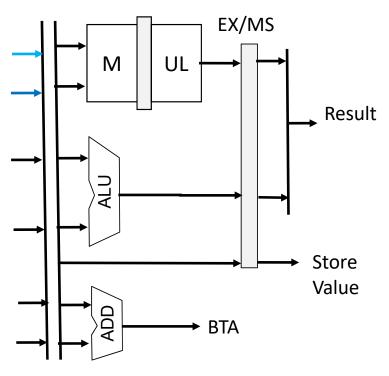

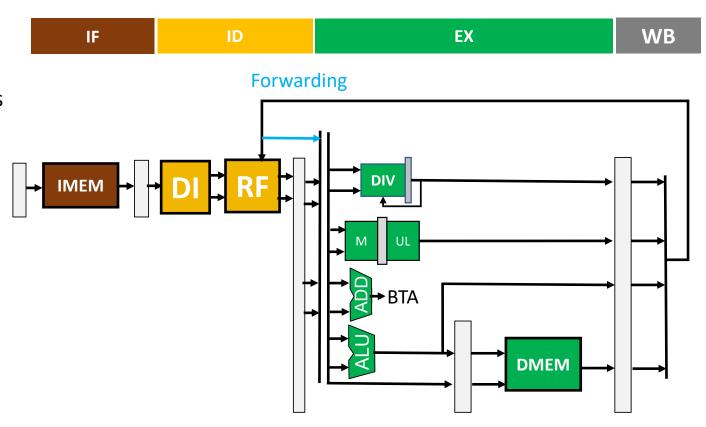

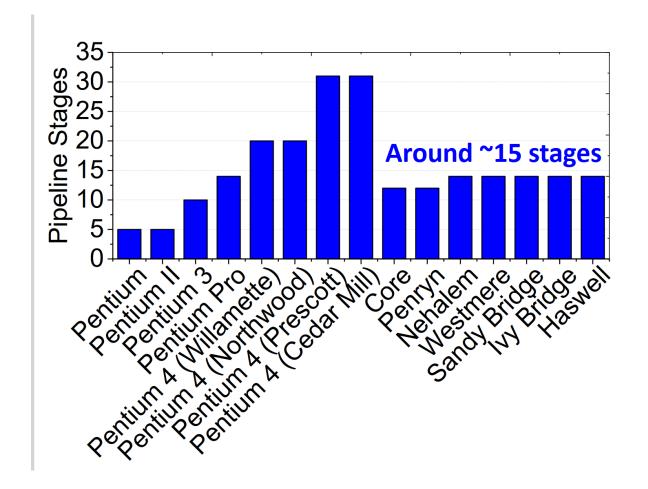

### Scalar Four-Stage Pipeline with Multi-cycle FUs with Forwarding

- The DIV and MUL do not need to make memory accesses

- Move the memory stage (MS) after the ALU (which is required for the address computation for load/store)

- Merges MS and EX stage (four stages)

- Single forwarding path required in four-stage pipeline

- Such changes need additional control in control path

22.04.2024

15

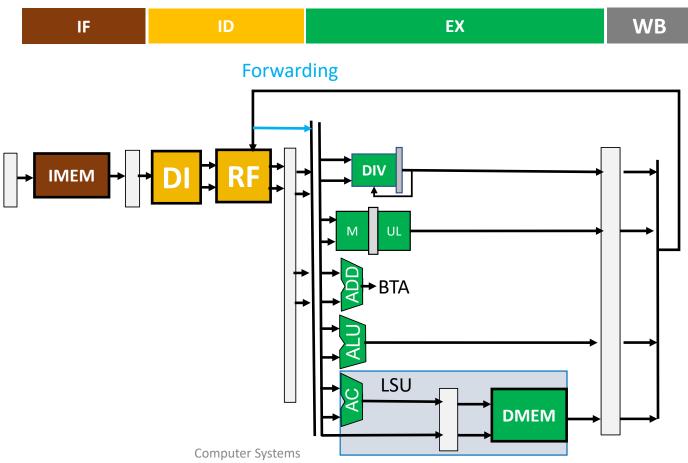

### Scalar Four-Stage Pipeline with Multi-cycle FUs and Load Store Unit (LSU)

• We can add a second address computation adder (AC) to form a simple so-called load/store unit (LSU)

16 22.04.2024

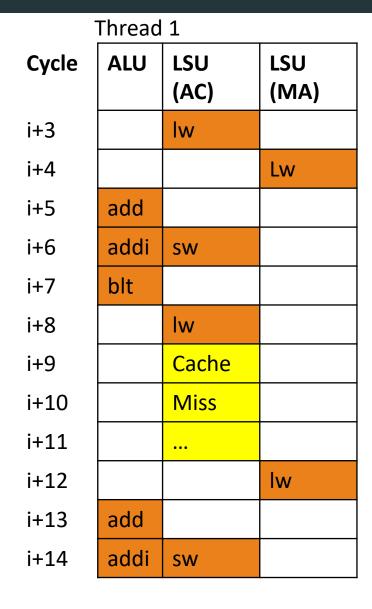

### Execution Scheme: Four-Stage In-Order Scalar Pipeline

- The EX stage has an execution scheme defined by the processor control path

- Version 1: Static In-order Scheduling

- ➤ Allow only one single instruction in the EX stage

- > Data hazards: Operands are forwarded by previous instruction

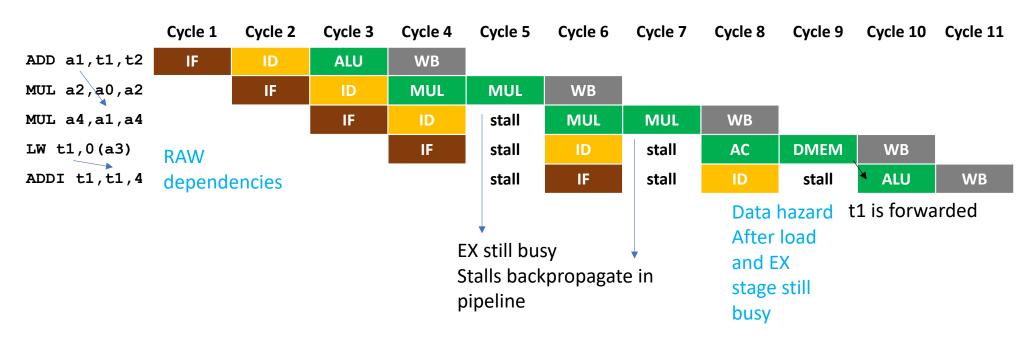

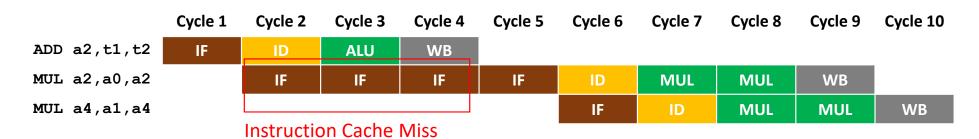

### Execution Scheme: Scalar Four-Stage Pipeline with Pipelined FUs

- <u>Version 2</u>: Static In-order Scheduling exploiting Pipelined FUs

- ➤ Allow only one single instruction in EX stage

- Except for: Pipelined MUL can use Initialization Interval for two consecutive MUL (still need to check for RAW dependency between the MUL)

|              | Cycle 1 | Cycle 2 | Cycle 3 | Cycle 4 | Cycle 5 | Cycle 6 | Cycle 7 | Cycle 8 | Cycle 9 | Cycle 10 |

|--------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|----------|

| ADD a1,t1,t2 | IF      | ID      | ALU     | WB      |         |         |         |         |         |          |

| MUL a2,a0,a2 |         | IF      | ID      | MUL(s1) | MUL(s2) | WB      |         |         |         |          |

| MUL a4,a1,a4 |         |         | IF      | ID      | MUL(s1) | MUL(s2) | WB      |         |         |          |

| LW t1,0(a3)  |         |         |         | IF      | ID      | stall   | AC      | DMEM    | WB      |          |

| ADDI t1,t1,4 |         |         |         |         | IF      | stall   | ID      | stall   | ALU     | WB       |

# **Load / Store Optimizations**

#### Memory System

- The memory for more complex processors usually uses caches to allow for fast accesses

- Memory latency depends whether the data is found in the cache (cache hit/miss)

- Also instructions are loaded from caches, so also instruction fetch may require several cycles on an instruction cache miss.

#### **Instruction Cache Misses**

- Instruction cache miss causes several cycles of delay for instruction fetch (IF), depending on speed to catch fresh instruction block from memory system

- Instructions are usually reloaded to cache in blocks (cache line size) so that usually there are several cache hits after a cache miss (depending on jumps/branches in program)

Advanced caches pre-fetch the next block before the cache miss happens to hide cache refill latencies.

#### **Load Cache Miss**

- Data cache misses lead to extra cycles for loads as the data needs to get fetched from another memory (level 2 cache, main memory)

- Example (function vec\_add, see first session): We load from two different addresses a0 and a1 (worst case both loads lead to a data cache miss)

#### Example vec\_add: Loads from two different addresses (a0,a1)

Example C-Code 3

```

// vector addition of 4-element integer vectors

void vec_add(int[4] a, int[4] b, int[4] c) {

unsigned int i;

for (i=0;i<4;i++) {

c[i] = a[i] + b[i];

}

}</pre>

```

#### RISC-V Code

```

# base address of a: a0,

# base address of b: a1,

# base address of c: a2,

# i: t0, constant 4: t3

vec add:

LI t0,0

# i=0

LI t3,4

# t3=4

vec add for:

LW t1,0(a0)

# t1 = a[i]

LW t2,0(a1)

# t2 = b[i]

ADD t1, t1, t2 # t1 = a[i] + b[i]

SW t1,0(a2)

\# c[i] = t1

ADDI a0,a0,4

#next element is base address + 4

ADDI a1,a1,4

#next element is base address + 4

ADDI a2,a2,4

#next element is base address + 4

ADDI t0,t0,1

# i++

BLTU t0,t3,vec add for \# for (i < 4)

# void return

RET

```

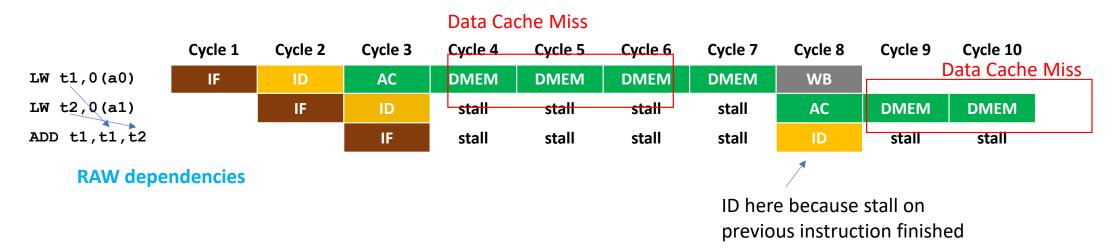

## Nonblocking Loads (1/2)

- Load accesses are for longer times in flight due to cache misses

- Most interconnects/caches allow to overlap multiple memory accesses

- Allows to execute multiple load accesses in overlapping fashion

- Example (function vec\_Add): Cache observes both addresses for load accesses and may need to reload cache lines for both accesses when both miss.

|              | Data Cache Misses |         |         |         |         |         |         |         |         |          |  |  |  |

|--------------|-------------------|---------|---------|---------|---------|---------|---------|---------|---------|----------|--|--|--|

|              | Cycle 1           | Cycle 2 | Cycle 3 | Cycle 4 | Cycle 5 | Cycle 6 | Cycle 7 | Cycle 8 | Cycle 9 | Cycle 10 |  |  |  |

| LW t1,0(a0)  | IF                | ID      | AC      | DMEM    | DMEM    | DMEM    | DMEM    | WB      |         |          |  |  |  |

| LW t2,0(a1)  |                   | IF      | ID      | AC      | DMEM    | DMEM    | DMEM    | DMEM    | WB      |          |  |  |  |

| ADD t1,t1,t2 |                   |         | IF      | ID      | stall   | stall   | stall   | stall   | ALU     | WB       |  |  |  |

## Nonblocking Loads (2/2)

- Cache usually returns values in-order (some caches/interconnects support to return data out-of-order)

- Example (function 3): When only the first load misses, the second load still needs to wait in the LSU when the LSU returns results in-order.

|              | Data Cache Misses |         |         |         |         |         |         |         |         |          |  |  |  |

|--------------|-------------------|---------|---------|---------|---------|---------|---------|---------|---------|----------|--|--|--|

|              | Cycle 1           | Cycle 2 | Cycle 3 | Cycle 4 | Cycle 5 | Cycle 6 | Cycle 7 | Cycle 8 | Cycle 9 | Cycle 10 |  |  |  |

| LW t1,0(a0)  | IF                | ID      | AC      | DMEM    | DMEM    | DMEM    | DMEM    | WB      |         |          |  |  |  |

| LW t2,0(a1)  |                   | IF      | ID      | AC      | DMEM    | DMEM    | DMEM    | DMEM    | WB      |          |  |  |  |

| ADD t1,t1,t2 |                   |         | IF      | ID      | stall   | stall   | stall   | stall   | ALU     | WB       |  |  |  |

No data cache miss, but we need to wait for first cache access to finish.

#### **Store Cache Miss**

- Depending on Store Policy: Write-back data cache:

- Additional latencies for stores possible when a dirty cache line needs to be replaced.

- Dirty cache line needs first to be written to memory before it can be replaced

- Write through data cache:

- Long store latency because the data is written not only to cache but also to main memory.

#### Example: We store to two different addresses a0 and a1 (first store misses)

|             |         |         |         | Data Cache Misses |         |         |         |         |         |          |          |  |  |

|-------------|---------|---------|---------|-------------------|---------|---------|---------|---------|---------|----------|----------|--|--|

|             | Cycle 1 | Cycle 2 | Cycle 3 | Cycle 4           | Cycle 5 | Cycle 6 | Cycle 7 | Cycle 8 | Cycle 9 | Cycle 10 | Cycle 11 |  |  |

| SW t1,0(a0) | IF      | ID      | AC      | DMEM              | DMEM    | DMEM    | DMEM    | WB      |         |          |          |  |  |

| SW t2,0(a1) |         | IF      | ID      | stall             | stall   | stall   | stall   | AC      | DMEM    | WB       |          |  |  |

| LI t2,4     |         |         | IF      | stall             | stall   | stall   | stall   | ID      | stall   | ALU      | WB       |  |  |

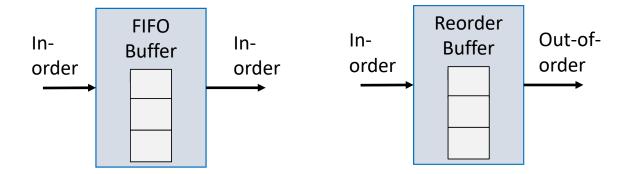

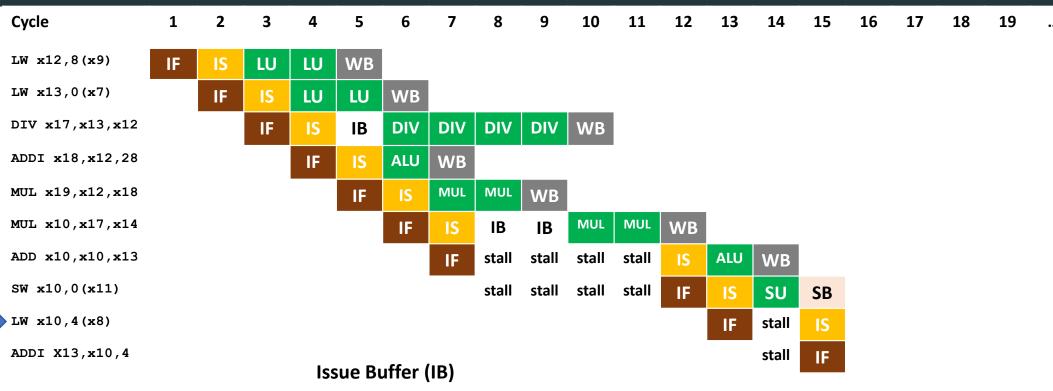

#### Buffers

- A buffer can store several values

- FIFO (First-in-first-out) buffer: Values can be read only from the buffer in the same order they are written to the buffer

- Reorder buffer: We can look up and read any value in the buffer

#### Store Buffer

- It is not really necessary to wait until a store write completes

- Store Unit (SU) with Store Buffer:

- > Put store address and data to store buffer (sometimes called "Posted stores")

- > Store buffer performs memory store access (MSA) independently from pipeline

- ➤ Only stall pipeline for stores when store buffer is full

- Load Unit (LU): Load more complex:

- > need to first look whether address is in store buffer then in cache

- riangleright or need to wait until SB is empty.

#### Nonblocking Stores with Store Buffer

- Store accesses are for longer times in flight due to cache misses

- Store Buffer store accesses and pipeline continues execution

- Store Buffer writes data to memory via Memory Store Access (MSA).

- Only stall pipeline for stores when store buffer is full

- Example:

|             | Cycle 1 | Cycle 2 | Cycle 3 | Cycle 4 | Cycle 5 | Cycle 6 | Cycle 7 | Cycle 8 | Cycle 9 | Cycle 10 |

|-------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|----------|

| SW t1,0(a0) | IF      | ID      | AC      | SB      | SB      | SB      | MSA     |         |         |          |

| SW t2,0(a1) |         | IF      | ID      | AC      | SB      | SB      | SB      | MSA     |         |          |

| LI t2,4     |         |         | IF      | ID      | ALU     | WB      |         |         |         |          |

# Execution Scheme: Scalar Four-Stage Pipeline with Pipelined FUs and Load Store Optimization

- Version 3: Static Scheduling with pipelined FUs and Load Store Optimization

- ➤ Allow only one single instruction in EX stage

- > Except for:

- > Pipelined MUL can use Initialization Interval for two consecutive MUL

- > Certain number of nonblocking Loads can be in EX stage (then EX stalls)

- ➤ Certain number of stores can be posted in the SB depending on SB size (EX stalls when SB full). When Store is posted in SB, it does not count as instruction in EX stage.

|              | Cycle<br>1 | Cycle<br>2 | Cycle<br>3 | Cycle<br>4 | Cycle<br>5 | Cycle<br>6 | Cycle<br>7 | Cycle<br>8 | Cycle<br>9 | Cycle<br>10 | Cycle<br>11 | Cycle<br>12 |

|--------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|-------------|-------------|-------------|

| ADD a2,t1,t2 | IF         | ID         | ALU        | WB         |            |            |            |            |            |             |             |             |

| MUL a2,a0,a2 |            | IF         | ID         | MUL(s1)    | MUL(s2)    | WB         |            |            |            |             |             |             |

| MUL a4,a1,a4 |            |            | IF         | ID         | MUL(s1)    | MUL(s2)    | WB         |            |            |             |             |             |

| SW a2,0(a3)  |            |            |            | IF         | ID         | stall      | AC         | SB         | SB         | MSA         |             |             |

| ADDI a3,a3,4 |            |            |            |            | IF         | stall      | ID         | ALU        | WB         |             |             |             |

| SW a2,0(a3)  |            |            |            |            |            | stall      | IF         | ID         | AC         | SB          | SB          | MSA         |

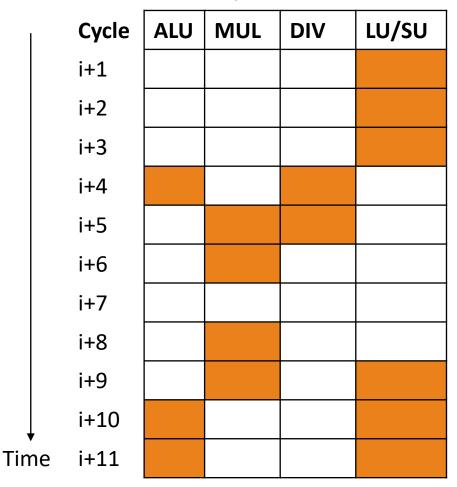

# Performance of Scalar Four-Stage Pipeline with Pipelined FUs and Load Store Optimization

- We still only allow one instruction to execute in EX stage except for some instruction types (MUL, Store, Load) in Version 3

- Multi-cycle operations cause many stalls (stiff scalar execution scheme)

|              | Cycle 1 | Cycle 2 | Cycle 3 | Cycle 4 | Cycle 5 | Cycle 6 | Cycle 7 | Cycle 8 | Cycle 9 | Cycle 10 |     |

|--------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|----------|-----|

| ADD a2,t1,t2 | IF      | ID      | ALU     | WB      |         |         |         |         |         |          |     |

| MUL a2,a0,a2 |         | IF      | ID      | MUL(s1) | MUL(s2) | WB      |         |         |         |          |     |

| DIV a4,a1,a4 |         |         | IF      | ID      | stall   | DIV     | DIV     | DIV     | DIV     | WB       |     |

| LW t1,0(a3)  |         |         |         | IF      | stall   | ID      | stall   | stall   | stall   | AC       |     |

| ADDI a3,a3,4 |         |         |         |         | stall   | IF      | stall   | stall   | stall   | ID       | ••• |

- Can we interleave instructions to make better use of parallel units, maybe even just start them when they are ready, possibly out-of-order (OoO)?

- We want to exploit so-called Instruction Level Parallelism

#### Challenges for Exploiting Instruction Level Parallelism: Structural Hazards

- Start instructions in EX stage when FUs are available?

- Challenge: Structural Hazards, e.g. in WB Stage

|              | Cycle 1 | Cycle 2 | Cycle 3 | Cycle 4 | Cycle 5 | Cycle 6 | Cycle 7 | Cycle 8 | Cycle 9 Cycle 10      |

|--------------|---------|---------|---------|---------|---------|---------|---------|---------|-----------------------|

| ADD a2,t1,t2 | IF      | ID      | ALU     | WB      |         |         |         |         |                       |

| MUL a2,a0,a2 |         | IF      | ID      | MUL(s1) | MUL(s2) | WB      |         |         |                       |

| MUL a4,a1,a4 |         |         | IF      | ID      | MUL(s1) | MUL(s2) | WB      |         |                       |

| LW t1,0(a3)  |         |         |         | IF      | ID      | AC      | DMEM    | WB      | Two WB in same cycle! |

| ADDI a3,a3,4 |         |         |         |         | IF      | ID      | ALU     | WB      | WB collision!         |

|              |         |         |         |         |         |         |         |         | Structural Hazard!    |

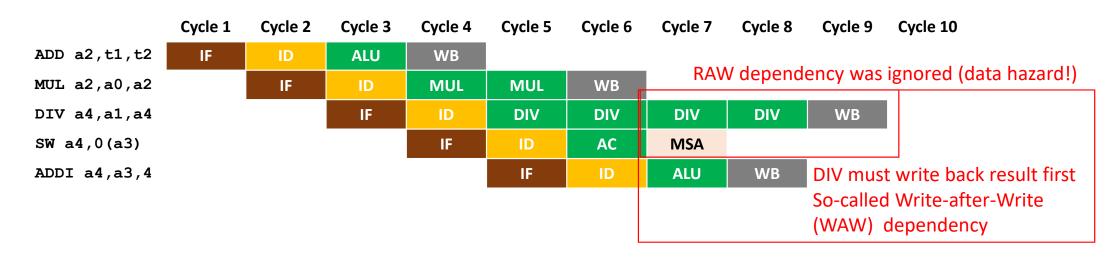

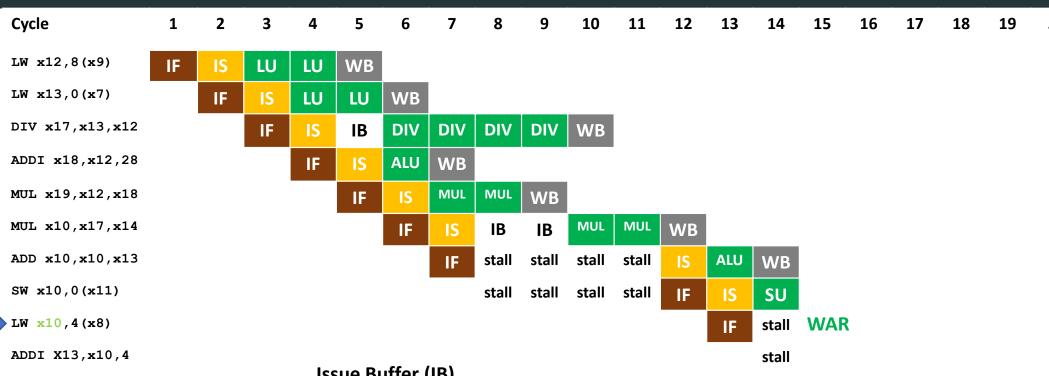

#### Challenges for Exploiting Instruction Level Parallelism: Instruction Dependencies

- Start instructions in EX stage when FUs are available?

- Instructions can *overtake* each other due to different FU latencies.

- Challenge: The assembly program defines a program order for the instructions.

- Requires consideration of instruction dependencies during pipelined execution to preserve program order.

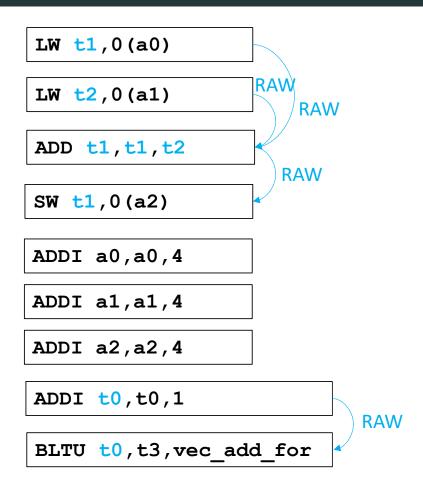

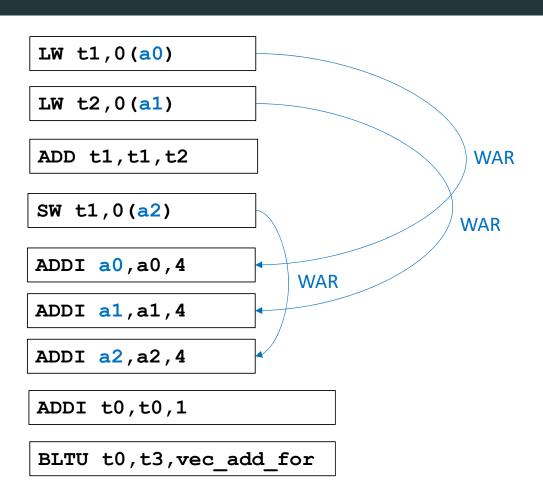

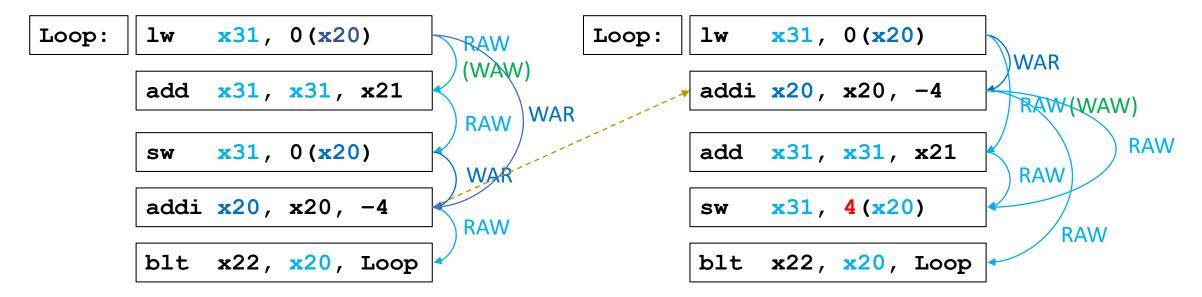

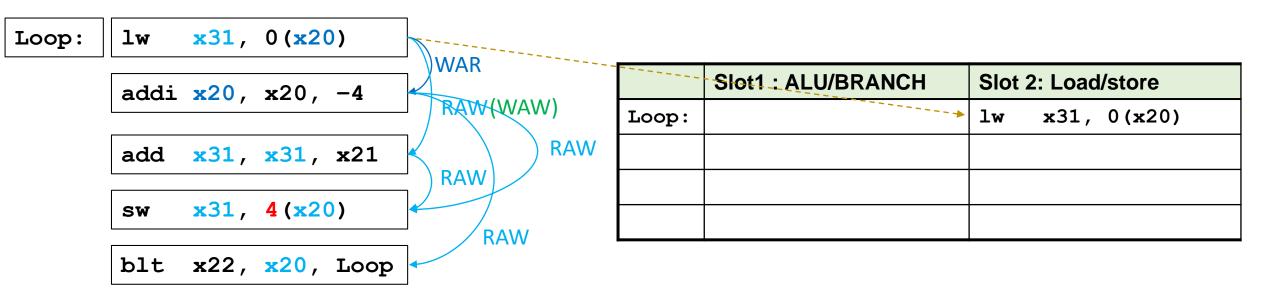

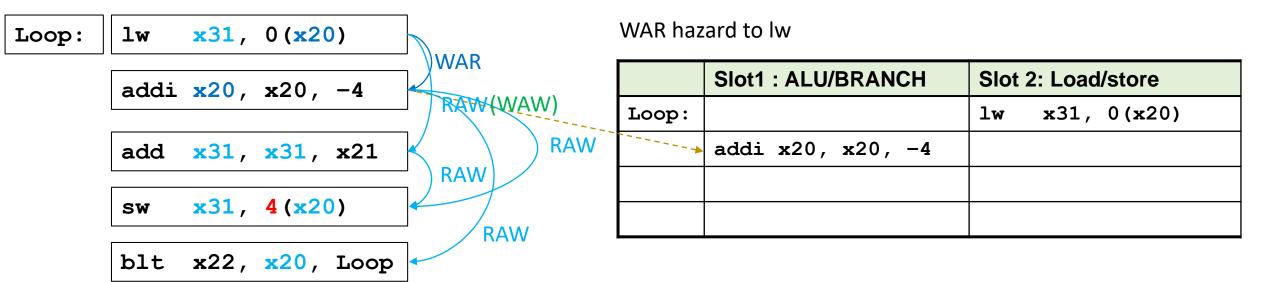

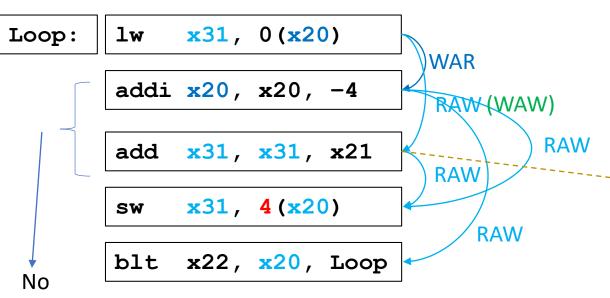

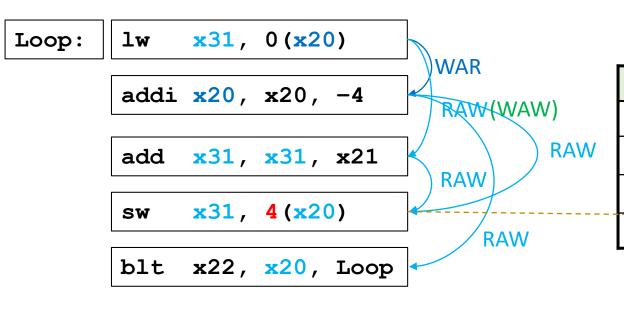

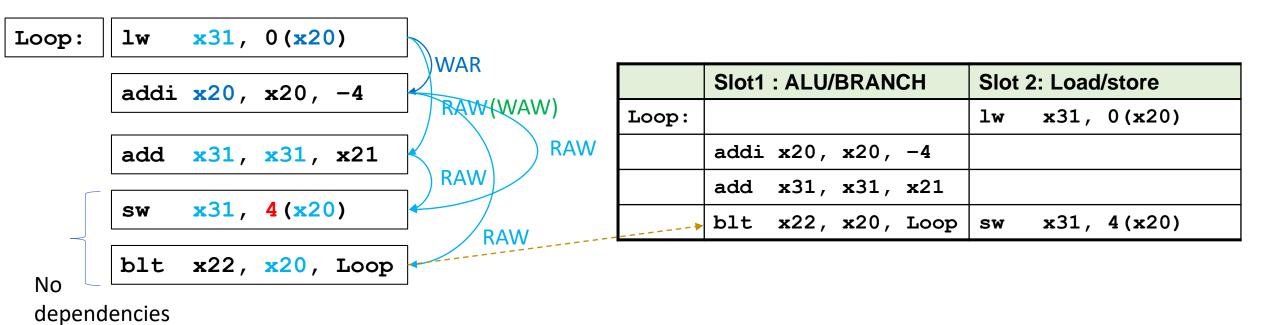

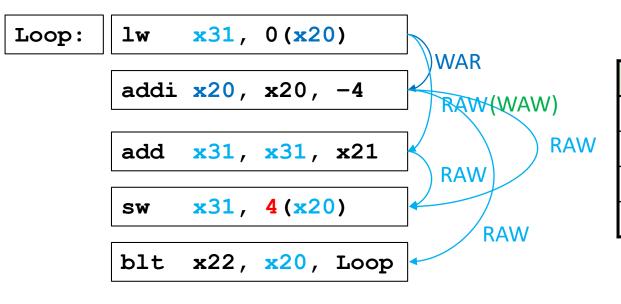

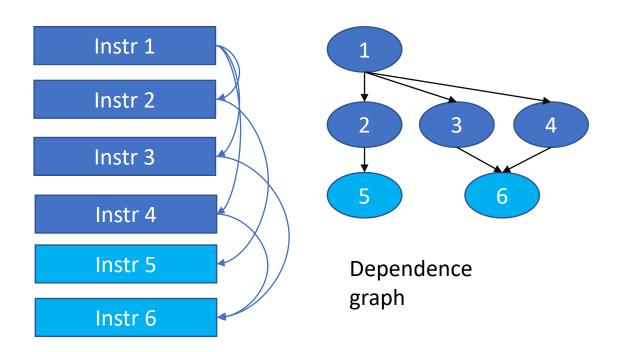

## Instruction Dependencies

A closer look at RAW, WAR and WAW!

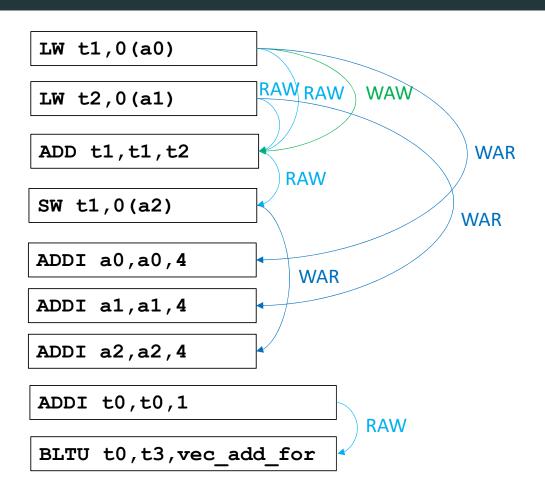

## Types of Instruction Dependencies

- Read-after-Write (RAW): Also "True dependency"

- Result of one instruction (write) is needed as input for another instruction (read)

- May cause data hazards (we seen this one already)

- Write-after-Read (WAR): Also "anti-dependency"

- A value is used (read) and then updated (write)

- The update (write) is not allowed to overtake the use (read)

- Write-after-Write (WAW): Also "output dependency"

- A value us updated (write) and then updated again (write)

- The second update may not overtake the first update

- Often created when registers are reused for different variables

Example for RAW: XOR a1,a2,a4 RAW ADD a3,a1,t1

Example for WAR: SW a1,0(a2) WAR ADDI a2,a3,4

Example for WAW:

LW a1,0(a2)

/ WAW

LI **a1**,a3,4

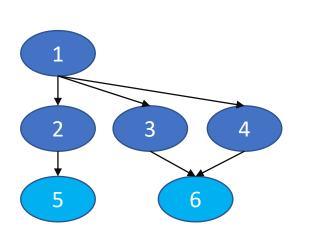

#### Dep. For Example Program (vec\_add)

• Example C-Code 3

```

// vector addition of 4-element integer vectors

void vec_add(int[4] a, int[4] b, int[4] c) {

unsigned int i;

for (i=0;i<4;i++) {

c[i] = a[i] + b[i];

}

}</pre>

```

```

# base address of a: a0.

# base address of b: a1,

# base address of c: a2,

# i: t0, constant 4: t3

vec add:

LI t0.0

# i=0

LI t3.4 # t3=4

vec add for:

LW t1,0(a0) # t1 = a[i]

LW t2,0(a1) \# t2 = b[i]

ADD t1,t1,t2 \# t1 = a[i] + b[i]

SW t1,0(a2) # c[i] = t1

ADDI a0,a0,4 #next element is base address + 4

ADDI a1,a1,4 #next element is base address + 4

ADDI a2,a2,4 #next element is base address + 4

ADDI t0,t0,1 # i++

BLTU t0,t3,vec add for # for (i < 4)

RET # void return

```

## Dep. For Example Program (vec\_add) (RAW)

Mark all RAW dependencies for the following code block:

```

LI t0,0

LI t3,4

vec add for:

LW t1,0(a0)

LW t2,0(a1)

ADD t1,t1,t2

SW t1,0(a2)

ADDI a0,a0,4

ADDI a1,a1,4

ADDI a2,a2,4

ADDI t0,t0,1

BLTU t0,t3,vec_add_for

RET

```

## Dep. For Example Program (vec\_add) (WAR)

Mark all WAR dependencies for the following code block:

```

LI t0,0

LI t3,4

vec add for:

LW t1,0(a0)

LW t2,0(a1)

ADD t1,t1,t2

SW t1,0(a2)

ADDI a0,a0,4

ADDI a1,a1,4

ADDI a2,a2,4

ADDI t0,t0,1

BLTU t0,t3,vec_add_for

RET

```

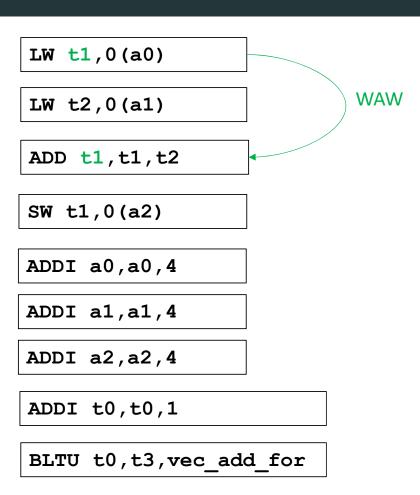

## Dep. For Example Program (vec\_add) (WAW)

Mark all WAW dependencies for the following code block:

```

LI t0,0

LI t3,4

vec add for:

LW t1,0(a0)

LW t2,0(a1)

ADD t1,t1,t2

SW t1,0(a2)

ADDI a0,a0,4

ADDI a1,a1,4

ADDI a2,a2,4

ADDI t0,t0,1

BLTU t0,t3,vec_add_for

RET

```

#### Dep. For Example Program (vec\_add) (ALL)

Mark all dependencies for the following code block:

LI t0,0

LI t3,4

vec add for:

LW t1,0(a0)

LW t2,0(a1)

ADD t1,t1,t2

SW t1,0(a2)

ADDI a0,a0,4

ADDI a1,a1,4

ADDI a2,a2,4

ADDI t0,t0,1

BLTU t0,t3,vec\_add\_for

RET

#### Challenges with Interleaving Instruction Execution in EX Stage

- 1. We have to consider **RAW**, **WAR** and **WAW** dependencies.

- **2. Structural hazards** must be avoided, e.g., FU is already busy.

- 3. Some instructions can cause so-called **exceptions** (e.g. memory fault on load/store) (See optional content for what is required for precise exceptions).

22.04.2024 Computer Systems 42

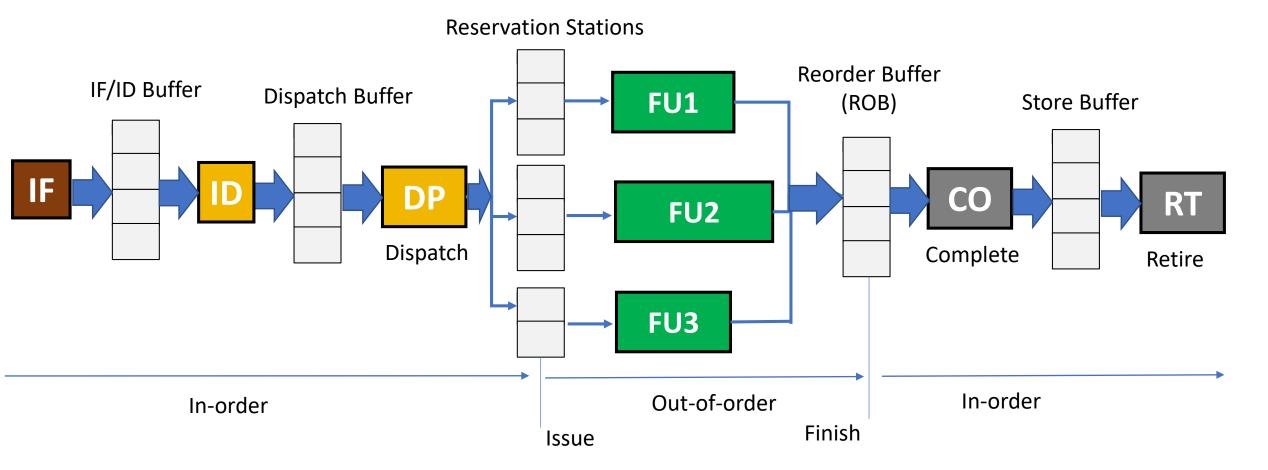

## **Dynamic Scheduling With Scoreboard**

Out-of-Order (OoO, O3) Pipeline

**Computer Architecture A Quantitative Approach – Section C7**

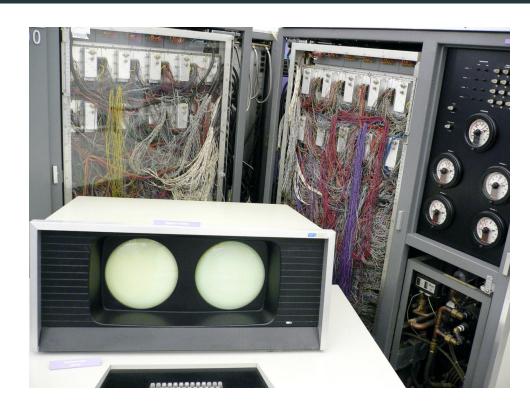

#### The CDC 6600 Project ['1964]

- First implementation of Scoreboard (Out-of-Order)

- 16 separate non-pipelined functional units (7 int, 4 Floating Point (FP), 5 memory)

Out-of-order (OoO) execution is also called dynamic instruction scheduling

Steve Jurvetson CC BY 2.0

#### The CDC 6600 Project ['1964]

#### CDC 6600 Scoreboard

- Three main components

- >Instruction status

- > Functional unit status

- ➤ Register result status

- For an example of use of Scoreboard in CDC 6600 see:

- Computer Architecture

A Quantitative Approach Section C7

|          |           | Instruction status |               |                    |                 |  |  |  |  |  |

|----------|-----------|--------------------|---------------|--------------------|-----------------|--|--|--|--|--|

| Instruct | ion       | Issue              | Read operands | Execution complete | Write<br>result |  |  |  |  |  |

| L.D      | F6,34(R2) | V                  | √             | √                  | V               |  |  |  |  |  |

| L.D      | F2,45(R3) | V                  | <b>√</b>      | <b>√</b>           | <b>√</b>        |  |  |  |  |  |

| MUL.D    | F0,F2,F4  | V                  | <b>√</b>      | <b>√</b>           |                 |  |  |  |  |  |

| SUB.D    | F8,F6,F2  | V                  | <b>√</b>      | <b>√</b>           | V               |  |  |  |  |  |

| DIV.D    | F10,F0,F6 | V                  |               |                    |                 |  |  |  |  |  |

| ADD.D    | F6,F8,F2  | √                  | <b>√</b>      | √                  |                 |  |  |  |  |  |

|         | Functional unit status |      |     |    |    |       |    |    |     |  |  |  |

|---------|------------------------|------|-----|----|----|-------|----|----|-----|--|--|--|

| Name    | Busy                   | Op   | Fi  | Fj | Fk | Qj    | Qk | Rj | Rk  |  |  |  |

| Integer | No                     |      |     |    |    |       |    |    |     |  |  |  |

| Mult1   | Yes                    | Mult | F0  | F2 | F4 |       |    | No | No  |  |  |  |

| Mult2   | No                     |      |     |    |    |       |    |    |     |  |  |  |

| Add     | Yes                    | Add  | F6  | F8 | F2 |       |    | No | No  |  |  |  |

| Divide  | Yes                    | Div  | F10 | F0 | F6 | Mult1 |    | No | Yes |  |  |  |

|    | No.    | Register result status |    |     |    |        |     |  |     |  |  |  |  |

|----|--------|------------------------|----|-----|----|--------|-----|--|-----|--|--|--|--|

|    | FO     | F2                     | F4 | F6  | F8 | F10    | F12 |  | F30 |  |  |  |  |

| FU | Mult 1 |                        |    | Add |    | Divide |     |  |     |  |  |  |  |

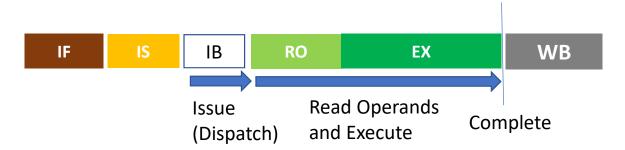

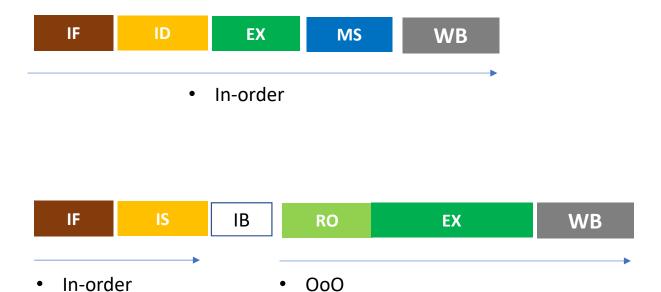

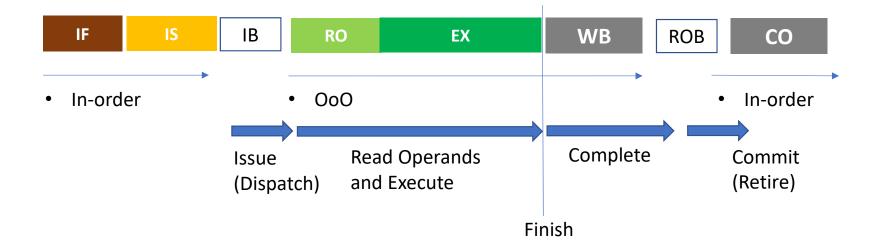

## Split of ID Stage

"To implement out-of-order execution, we must split the ID pipe stage into two stages:

- 1. *Issue*—Decode instructions, check for structural hazards.

- 2. Read operands—Wait until no data hazards, then read operands."

- "In a dynamically scheduled pipeline, all instructions pass through the issue stage in order (in-order issue); however, they can be stalled or bypass each other in the second stage (read operands) and thus enter execution out of order"

- -- Computer Architecture A Quantitative Approach 5<sup>th</sup> Ed. Section C7

#### Steps in Out-of-Order Execution (Scheme 1\*)

#### • 1. **Issue**

#### > Functional unit is free

- ➤ No other active instruction has the same destination register (guarantee that **WAW hazards** cannot be present)

- ➤ If a structural or WAW hazard exists, then the instruction issue stalls, and no further instructions will issue until these hazards are cleared.

#### • 2. Read operands

- ➤ When source operands are available, the scoreboard tells the functional unit to proceed to read the operands from the registers and begin execution.

- > The scoreboard resolves RAW hazards dynamically in this step, and instructions may be sent into execution out of order.

#### 3. Execution

> The functional unit begins execution upon receiving operands. When the result is ready, it notifies the scoreboard that it has completed execution.

#### • 4. Write result

- > Once the scoreboard is aware that the functional unit has completed execution, the scoreboard checks for **WAR hazards** and stalls the completing instruction, if necessary.

- -- \*Computer Architecture A Quantitative Approach 5<sup>th</sup> Ed. Section C7

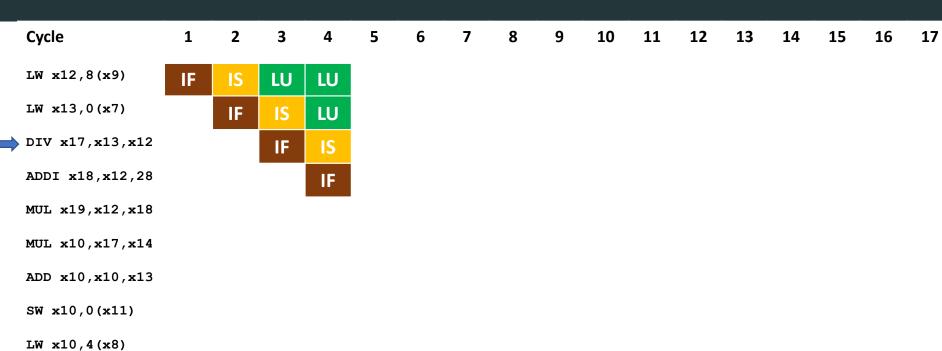

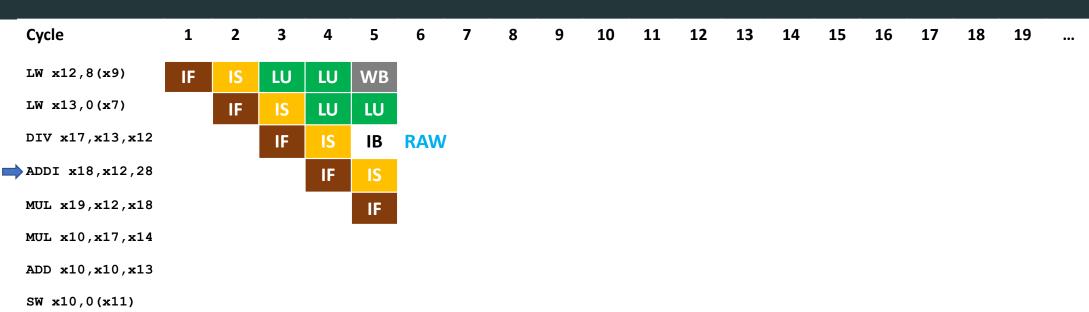

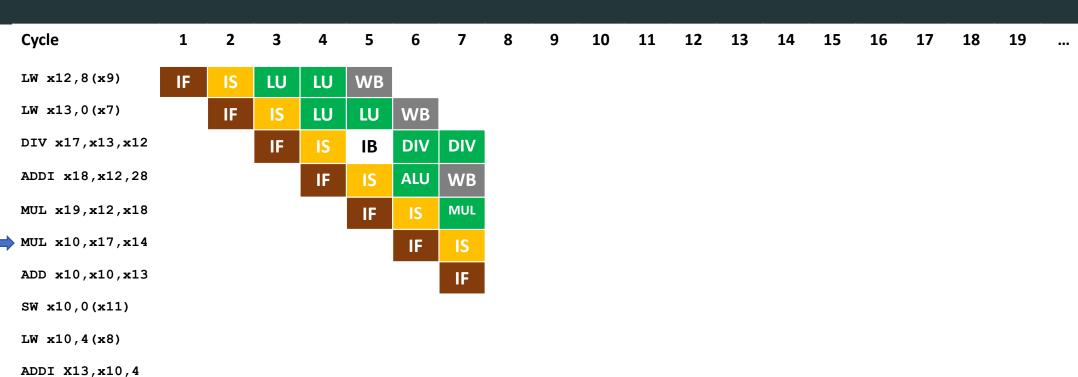

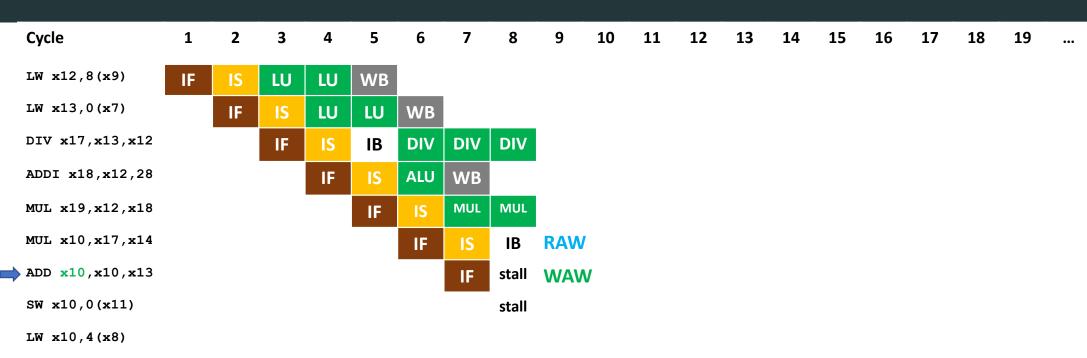

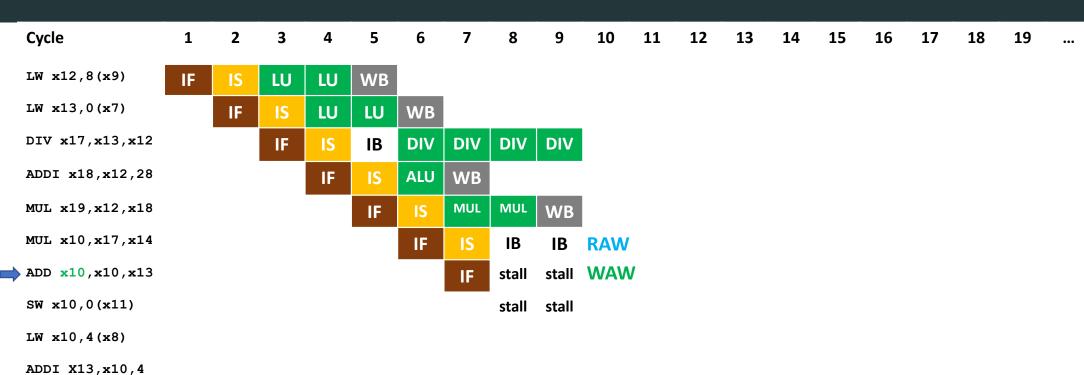

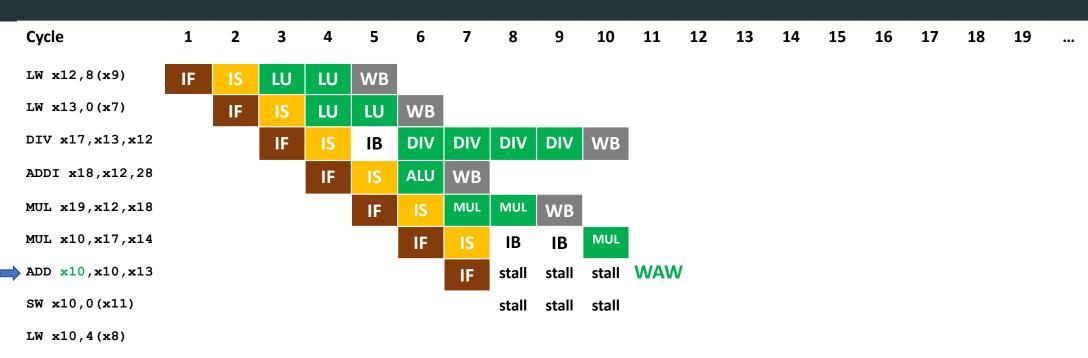

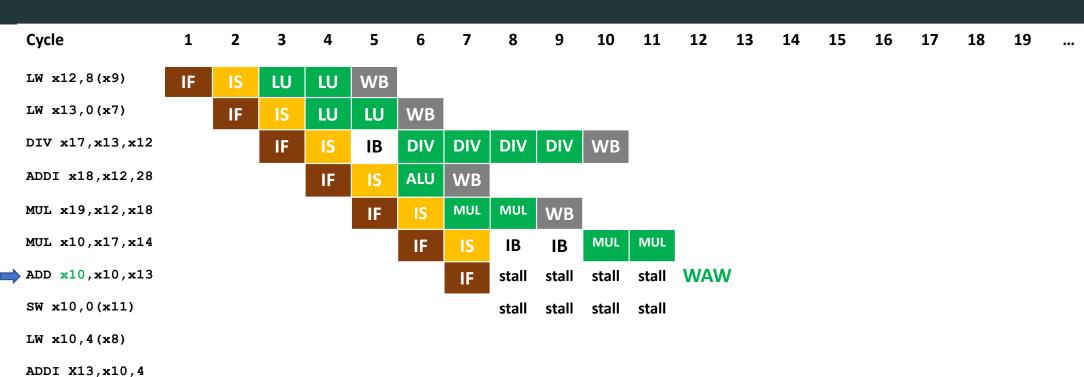

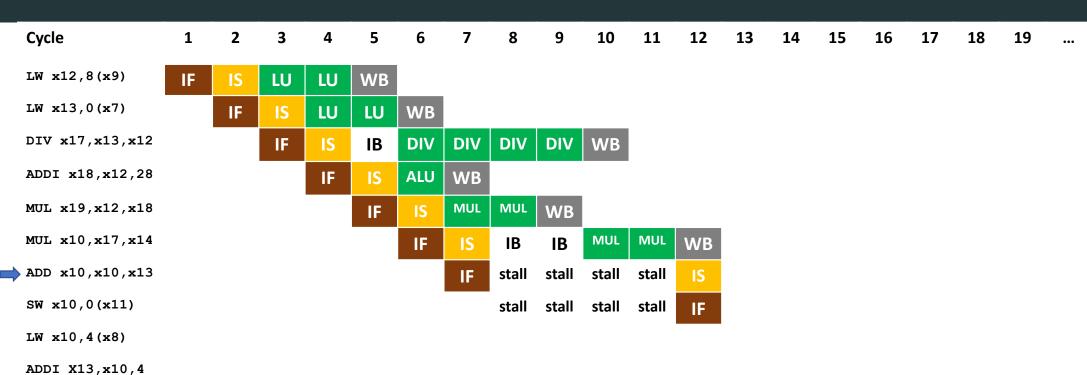

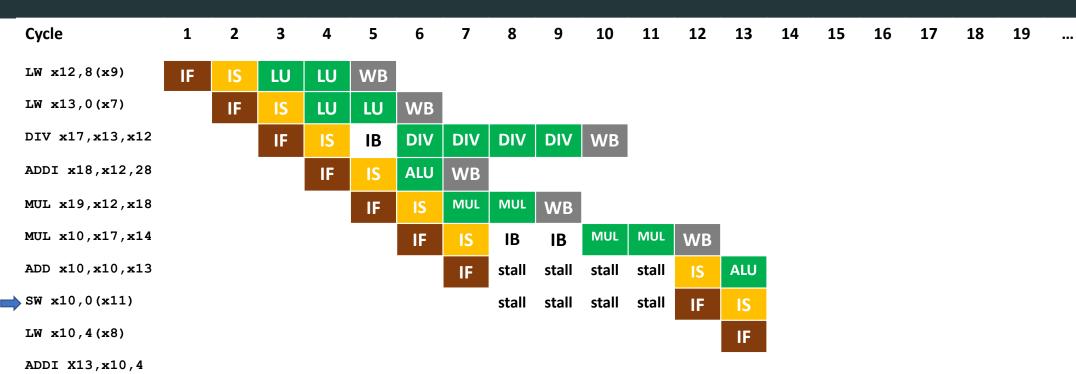

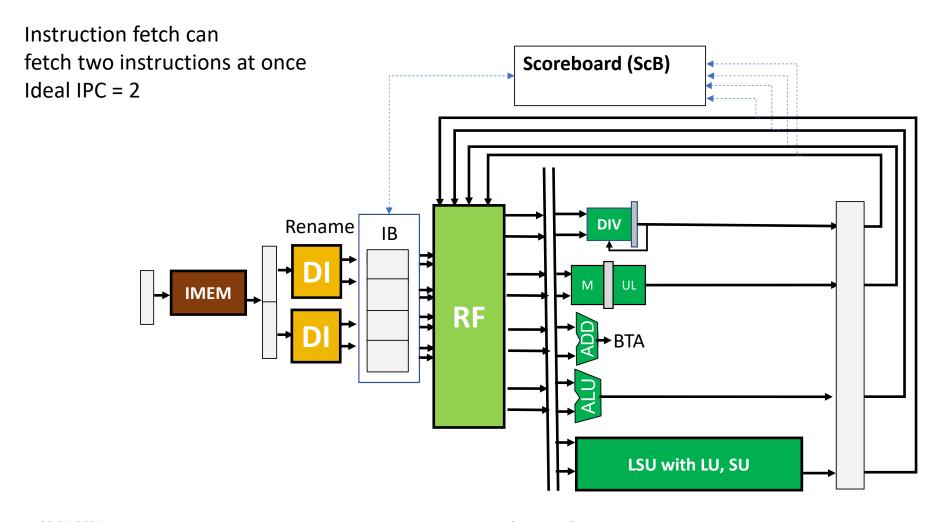

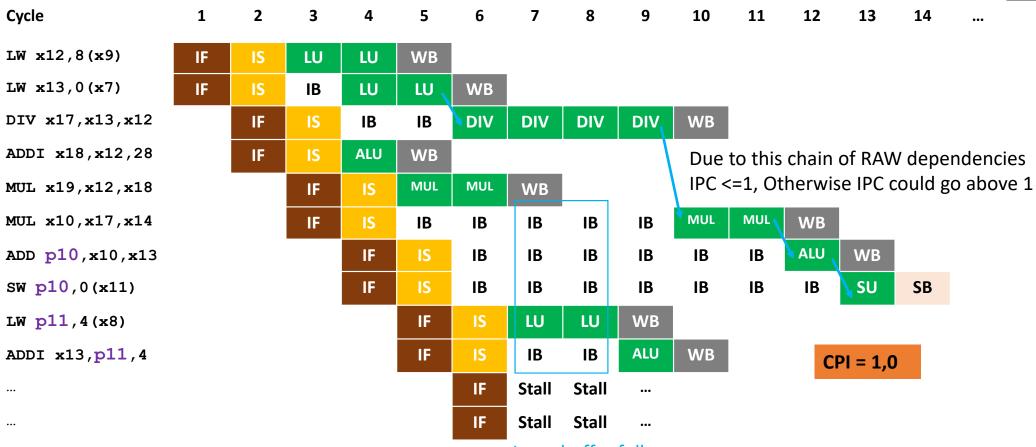

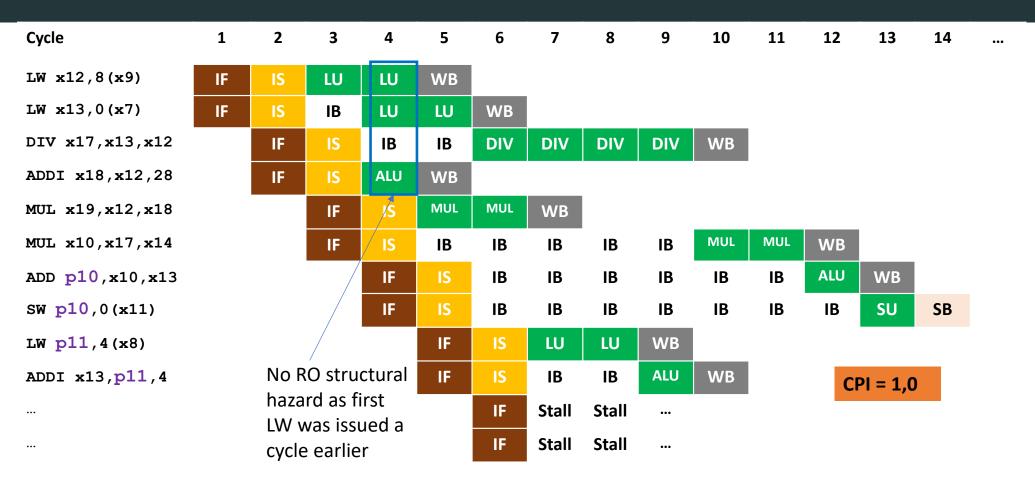

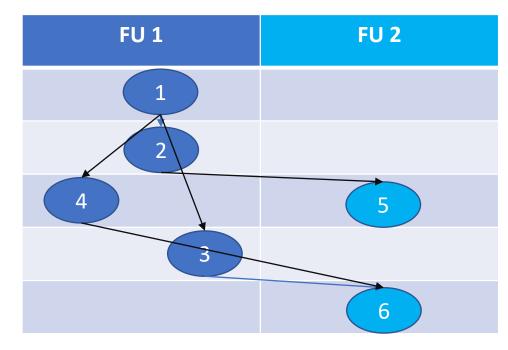

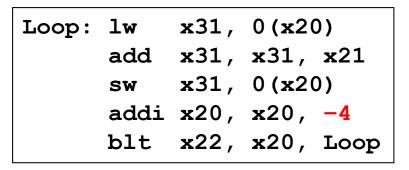

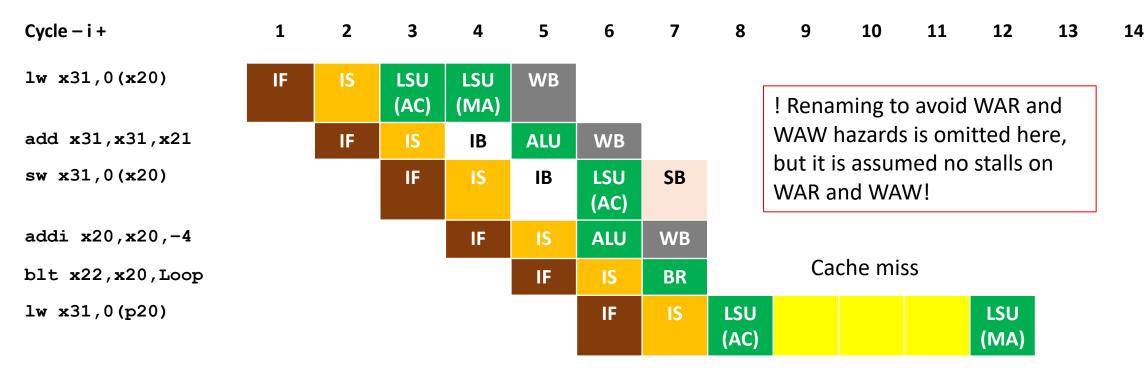

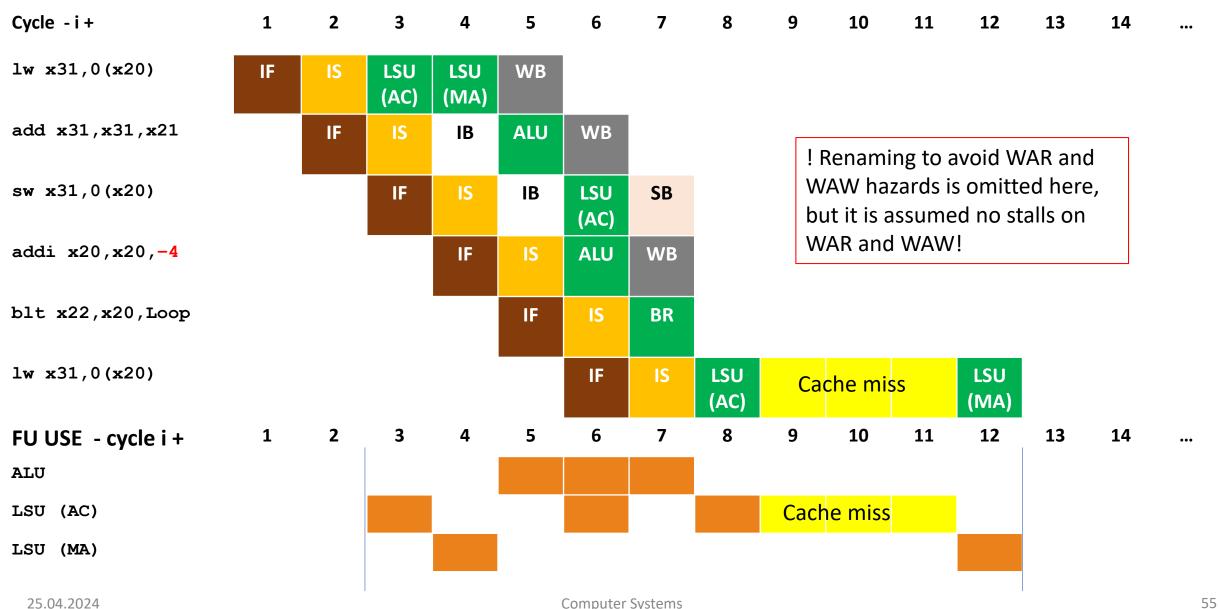

#### Steps in Out-of-Order Execution (Simpler Scheme 2\*\*)

- Issue Buffer (IB) holds multiple instructions waiting to issue.

- Instruction Decode (ID) adds next instruction to IB if

- there is space in IB and

- the instruction does not have a WAR or WAW dependency with any instruction in IB.

- Instruction Issue (IS) can issue any instruction in IB whose

- RAW hazards are satisfied to all previous instructions in IB

- FU is available.

- Note: With writeback (WB) we delete the instruction from the IB, this may enable more instructions to issue as RAW dependencies are resolved.

- -- \*\*Inspired by MIT course, Daniel Sanchez http://csg.csail.mit.edu/6.823S20/Lectures/L09.pdf

## Example OoO Processor: Simple Scoreboard Data Structure

- Simplified CDC-style Scoreboard Data Structure to track execution

- For Scheme 2, One Issue Buffer

- Logical, not HW implementation

| Instruction | rd | rs1 | rs2 | lmm | RO | Complete |

|-------------|----|-----|-----|-----|----|----------|

|             |    |     |     |     |    |          |

|             |    |     |     |     |    |          |

|             |    |     |     |     |    |          |

|             |    |     |     |     |    |          |

Scoreboard (ScB)

**FU Status (Ready?)**

| DIV | MUL | ALU | ADD | SU | LU |

|-----|-----|-----|-----|----|----|

|     |     |     |     |    |    |

RO: Instruction read operands (started the computation)

Complete: Instruction finished computation (in last EX stage)

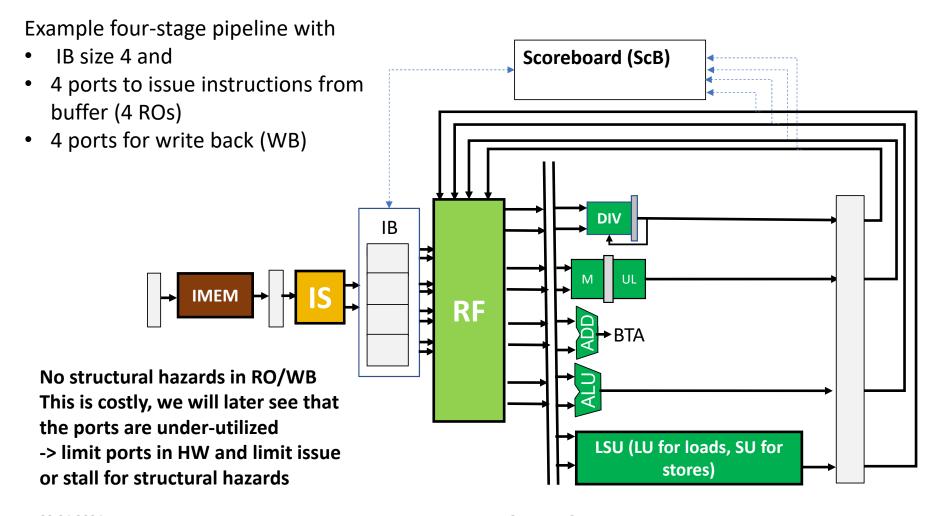

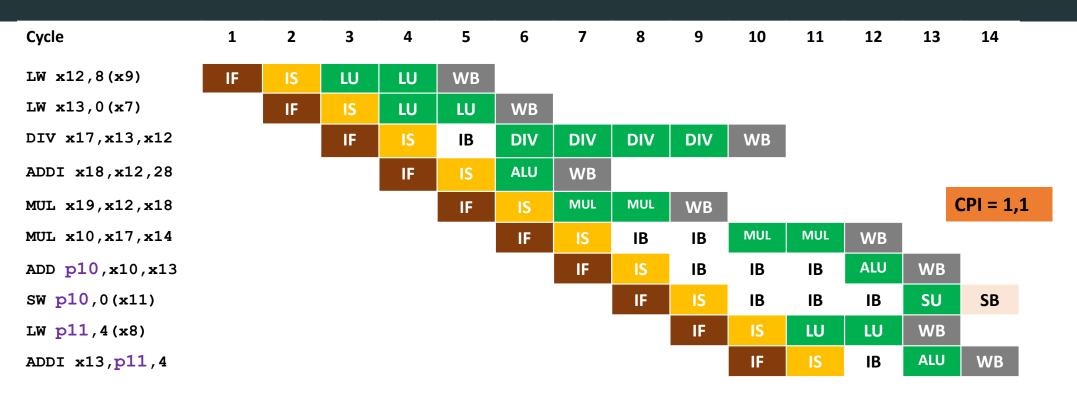

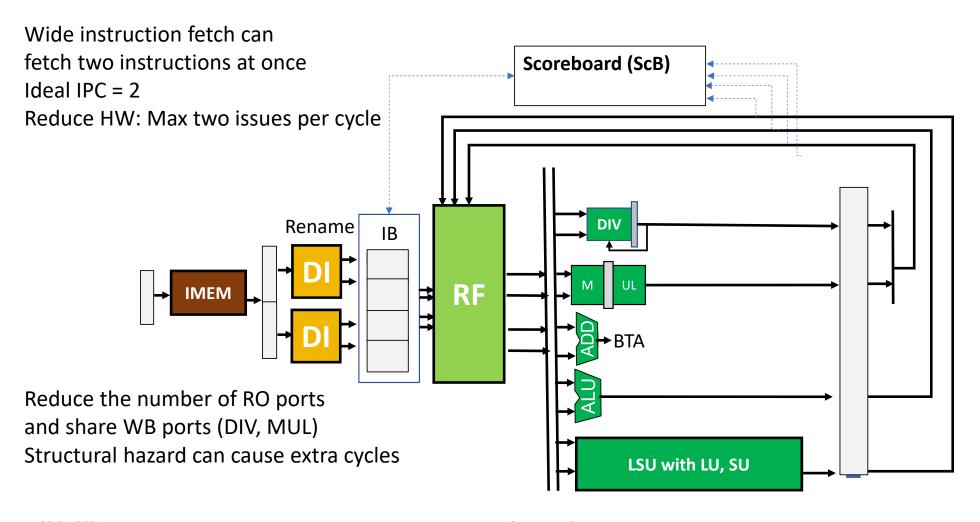

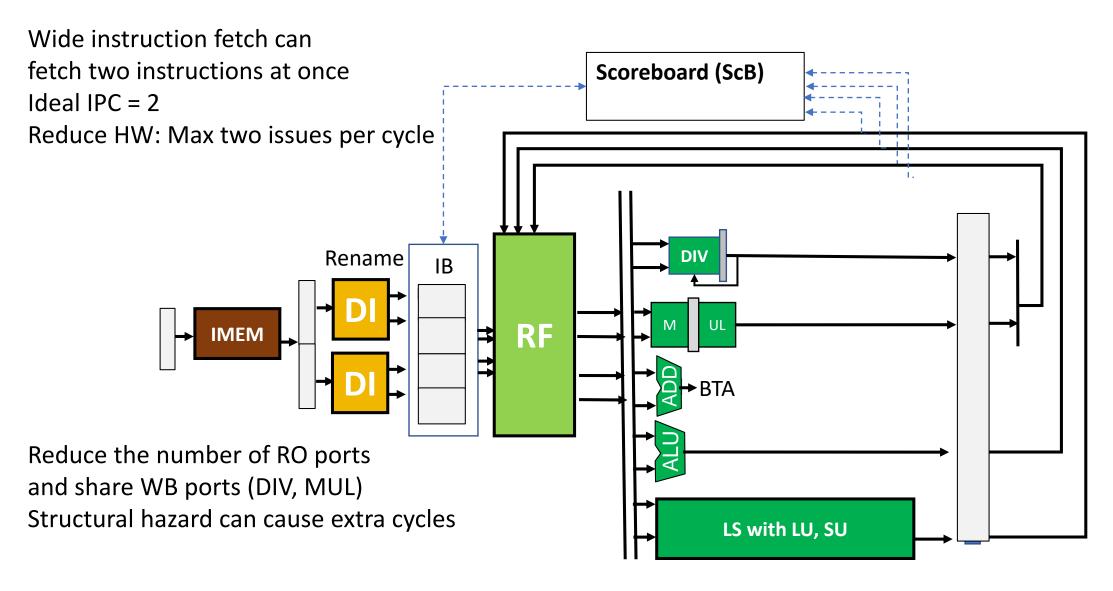

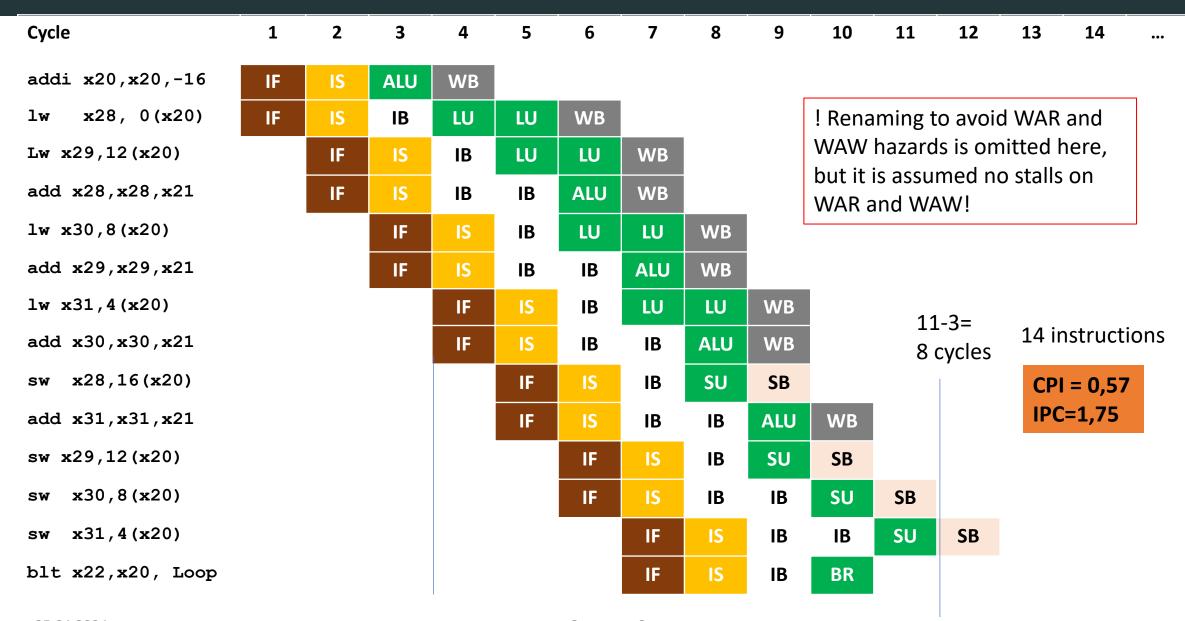

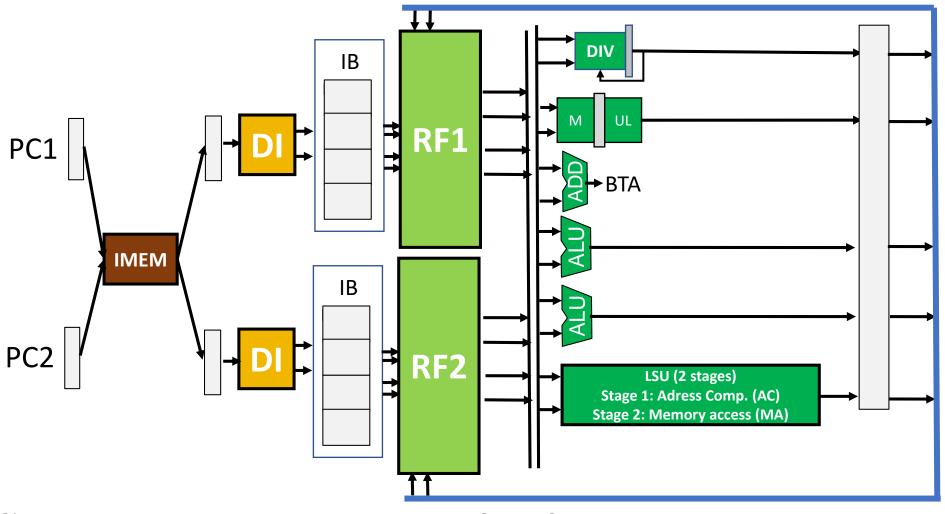

## Example OoO Processor: Scoreboard Integration

#### Example OoO Processor: FUs in EX stage

## For simplicity all FUs have fixed latency:

| FU  | Latency | Initialization Interval |                        |

|-----|---------|-------------------------|------------------------|

| ALU | 1       | 1                       |                        |

| ADD | 1       | 1                       |                        |

| MUL | 2       | 1                       | Pipelined              |

| DIV | 4       | 4                       | Serial (fixed latency) |

| LSU |         |                         |                        |

| LU  | 2       | 1                       | Nonblocking            |

| SU  | 1       | 1                       | Store buffered         |

- Instruction can only be issued when FU is available.

- SU and LU share same port, cannot be issued together

- We assume instruction cannot be issued to EX same cycle it was added to IB by ID

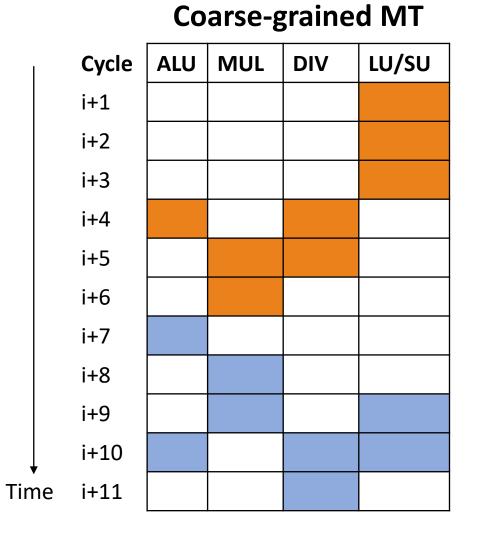

## Example OoO Processor – Pipeline Diagram - Cycle 2

2

3

1

LW x12,8(x9) | IF | IS | IF | IF

DIV x17,x13,x12

Cycle

ADDI x18,x12,28

MUL x19,x12,x18

MUL x10,x17,x14

ADD x10,x10,x13

SW x10,0(x11)

LW x10,4(x8)

ADDI X13,x10,4

#### Issue Buffer (IB)

6

8

7

10

9

12

11

**13**

14

**15**

16

**17**

18

19

| Ins | truction | rd  | rs1 | rs2 | Imm | RO | Complete |

|-----|----------|-----|-----|-----|-----|----|----------|

| LW  | •        | x12 | x9  |     | 8   |    |          |

|     |          |     |     |     |     |    |          |

|     |          |     |     |     |     |    |          |

|     |          |     |     |     |     |    |          |

#### **FU Status (Ready?)**

| DIV | MUL | ALU | ADD | SU | LU |

|-----|-----|-----|-----|----|----|

|     |     |     |     |    |    |

Computer Systems 52

## Example OoO Processor – Pipeline Diagram - Cycle 3

2 8 9 10 12 13 Cycle 1 3 6 7 11 14 **15** 16 **17** 18 19 LW x12,8(x9)IF IS LU **→** LW x13,0(x7) DIV x17,x13,x12 IF ADDI x18,x12,28 MUL x19,x12,x18 MUL x10,x17,x14

ADD x10,x10,x13

SW x10,0(x11)

LW x10,4(x8)

ADDI X13,x10,4

#### Issue Buffer (IB)

|   | Instruction | rd  | rs1 | rs2 | lmm | RO | Complete |

|---|-------------|-----|-----|-----|-----|----|----------|

|   | LW          | x12 | x9  |     | 8   | Х  |          |

|   | LW          | x13 | x7  |     | 0   |    |          |

| Ī |             |     |     |     |     |    |          |

| I |             |     |     |     |     |    |          |

#### **FU Status (Ready?)**

| DIV | MUL | ALU | ADD | SU | LU     |

|-----|-----|-----|-----|----|--------|

|     |     |     |     |    | Busy 1 |

Computer Systems 53

## Example OoO Processor – Pipeline Diagram - Cycle 4

Issue Buffer (IB)

| Instruction | rd  | rs1 | rs2 | Imm | RO | Complete |

|-------------|-----|-----|-----|-----|----|----------|

| LW          | x12 | x9  |     | 8   | Х  | х        |

| LW          | x13 | x7  |     | 0   | Х  |          |

| DIV         | x17 | x13 | x12 |     |    |          |

|             |     |     |     |     |    |          |

ADDI X13,x10,4

#### **FU Status (Ready?)**

| DIV | MUL | ALU | ADD | SU | LU     |

|-----|-----|-----|-----|----|--------|

|     |     |     |     |    | Busy 2 |

18

19

Computer Systems 54

#### Issue Buffer (IB)

| Instruc | tion | rd         | rs1        | rs2 | Imm | RO | Complete |

|---------|------|------------|------------|-----|-----|----|----------|

| LW      |      | <b>x13</b> | x7         |     | 0   | Х  | х        |

| DIV     |      | x17        | <b>x13</b> | x12 |     |    |          |

| ADDI    |      | x18        | X12        |     | 28  |    |          |

|         |      |            |            |     |     |    |          |

LW x10,4(x8)

ADDI X13,x10,4

#### **FU Status (Ready?)**

| DIV | MUL | ALU | ADD | SU | LU     |

|-----|-----|-----|-----|----|--------|

|     |     |     |     |    | Busy 1 |

#### Issue Buffer (IB)

| Instruction | rd  | rs1 | rs2 | Imm | RO | Complete |

|-------------|-----|-----|-----|-----|----|----------|

| DIV         | x17 | x13 | x12 |     | х  |          |

| ADDI        | x18 | x12 |     | 28  | х  | х        |

| MUL         | x19 | x12 | x18 |     |    |          |

|             |     |     |     |     |    |          |

ADDI X13,x10,4

#### **FU Status (Ready?)**

| DIV  | MUL | ALU  | ADD | SU | LU |

|------|-----|------|-----|----|----|

| Busy |     | Busy |     |    |    |

#### Issue Buffer (IB)

| Instruction | rd  | rs1 | rs2 | lmm | RO | Complete |

|-------------|-----|-----|-----|-----|----|----------|

| DIV         | x17 | x13 | x12 |     | х  |          |

| MUL         | x19 | x12 | x18 |     | Х  |          |

| MUL         | x10 | x17 | x14 |     |    |          |

|             |     |     |     |     |    |          |

#### **FU Status (Ready?)**

| DIV  | MUL      | ALU | ADD | SU | LU |

|------|----------|-----|-----|----|----|

| Busy | Busy(s1) |     |     |    |    |

#### Issue Buffer (IB)

| Instruction | rd         | rs1 | rs2 | Imm | RO | Complete |

|-------------|------------|-----|-----|-----|----|----------|