TU Wien:Technische Grundlagen der Informatik VU (Kastner)/Kapitel Micro16

Zur Navigation springen

Zur Suche springen

- 01 Zahlendarstellung

- 02 Numerik

- 03 Codierung

- 04 Informationstheorie

- 05 Boolesche Algebra

- 06 KV-Diagramme und BDD

- 07 Moore- & Mealy-AutomatenTGI+GDS

- 08 Digitalschaltungen, KominatorikTGI

- 09 Sequentielle Logik

- 10 Speicher

- 14 Micro16

- 15 Befehlssatz

- 16 Pipelining

- 17 Speichermanagement

- 18 Chipsatz

- 19 Multi-Core

- 20 Netzwerke

Seite um Informationen über und Code für den Micro16-Simulator zu sammeln. Der Simulator wurde vom TGI-Team entwickelt, ist in Java geschrieben und auf TUWEL verfügbar.

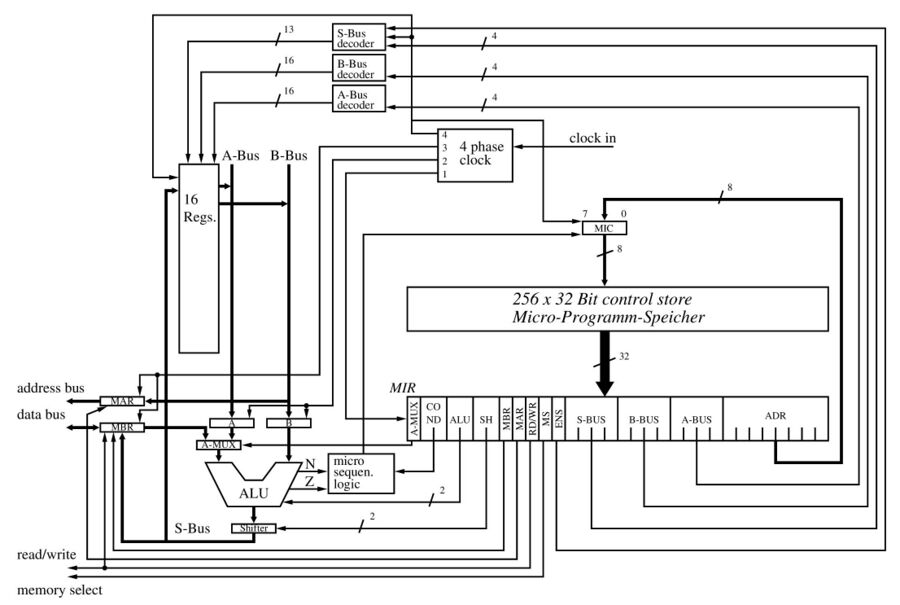

Komponenten[Bearbeiten | Quelltext bearbeiten]

Arithmetic Logic Unit[Bearbeiten | Quelltext bearbeiten]

| ALU | Beschreibung | Syntax |

|---|---|---|

| 00 | A-Bus unverändert durchschalten | A

|

| 01 | Addition | A + B

|

| 10 | Und-Verknüpfung | A & B

|

| 11 | negiert A-Bus | ~A

|

Rechnet im Zweierkomplement mit 16 Bit breiten Datenwörtern aus Registern. Das Ergebnis geht durch den #Shifter.

Ausgänge für #Micro Sequencing Logic:

- N: Ergebnis ist negativ (MSB=1)

- Z: Ergebnis ist zero

Shifter[Bearbeiten | Quelltext bearbeiten]

| SH | Beschreibung | Syntax |

|---|---|---|

| 00 | keine Veränderung | X

|

| 01 | left shift | lsh(X)

|

| 10 | right shift | rsh(X)

|

| 11 | ungültig |

Micro Sequencing Logic[Bearbeiten | Quelltext bearbeiten]

| COND | Beschreibung | Syntax |

|---|---|---|

| 00 | kein Sprung | |

| 01 | Sprung, wenn N=1 | if N goto addr

|

| 10 | Sprung, wenn Z=1 | if Z goto addr

|

| 11 | unbedingter Sprung | goto addr

|

Register File[Bearbeiten | Quelltext bearbeiten]

| 0 | 1 | -1 | PC | R0-R10 | AC |

16 Register, die je 16 Bit breit sind. Die ersten drei sind nicht schreibbar.

Micro Instruction Register[Bearbeiten | Quelltext bearbeiten]

Ein Codewort ist 32 bit groß.

| Feld | Beschreibung | Syntax | |

|---|---|---|---|

| AMUX | Ob das Memory Buffer Register als A-Eingang der ALU verwendet wird. | … <- MBR

| |

| COND | Sprungbedingung für die #Micro Sequencing Logic (2 bit) | [if N/Z] goto addr

| |

| ALU | Operation für die #Arithmetic Logic Unit (2 bit) | A, A+B, A&B, ~A

| |

| SH | Operation für den #Shifter (2 bit) | X, lsh(X), rsh(X)

| |

| MBR | Ob der S-Bus in das Memory Buffer Register geschrieben wird. | MBR <- …

| |

| MAR | Ob der B-Bus in das Memory Address Register geschrieben wird. | MAR <- R

| |

| RD/WR | Wenn MS (memory select) gesetzt ist, wird bei RD/WR=0 geschrieben und bei RD/WR=1 gelesen. Läuft über 2 Takte. |

rd, wr

| |

| MS | |||

| ENS | Wenn ENS gesetzt ist, wird der S-Bus in das durch S-Bus gegebene Register geschrieben. (4 bit) |

R <- …

| |

| S-Bus | |||

| B-Bus | Welches Register für den B-Bus ausgewählt wird. (4 bit) | A+B, A&B

| |

| A-Bus | Welches Register für den A-Bus ausgewählt wird. (4 bit) | A, ~A

| |

| ADDR | Sprungziel für Micro Instruction Counter, wenn COND erfüllt ist. (8 bit) | goto addr

| |

Code Grundlagen[Bearbeiten | Quelltext bearbeiten]

Vorzeichenumkehr[Bearbeiten | Quelltext bearbeiten]

R1 <- ~R1 R1 <- R1 + 1

Weil die ALU im Zweierkomplement rechnet.

Zweimal links shiften[Bearbeiten | Quelltext bearbeiten]

Benötigt nur eine Instruktion:

R1 <- lsh(R1 + R1)

XOR[Bearbeiten | Quelltext bearbeiten]

# R0 = R1 XOR R2 = (R1 & ~R2) + (~R1 & R2) R3 <- ~R2 R3 <- R1 & R3 R4 <- ~R1 R4 <- R4 & R2 R0 <- R3 + R4

Code Beispiele[Bearbeiten | Quelltext bearbeiten]

Gerades Paritätsbit[Bearbeiten | Quelltext bearbeiten]

R0 <- 0 # even parity of R1

(R1); if Z goto .end :loop

R3 <- R1 & 1

R3 <- R3 + R0

R0 <- R3 & 1

R1 <- rsh(R1)

goto .loop

:end

Für ungerade Parität setzt man R0 anfänglich auf 1.

Multiplikation[Bearbeiten | Quelltext bearbeiten]

# Multiplikation zweier positiver Zahlen kleiner 2^8 - 1

# R0 = R1 * R2

(R1); if Z goto .end :loop

R0 <- R0 + R2

R1 <- R1 + (-1); goto .loop

:end

Division[Bearbeiten | Quelltext bearbeiten]

# R0 = R1 / R2

# R1 = R1 % R2

R0 <- 0

R2 <- ~R2

R2 <- R2 + 1

:loop

(R1 + R2); if N goto .end

R0 <- R0 + 1

R1 <- R1 + R2

goto .loop

:end

Arithmetischer right shift[Bearbeiten | Quelltext bearbeiten]

# R0 = R0 >>> 1

R1 <- rsh(-1)

R1 <- ~R1

R1 <- R0 & R1

R0 <- rsh(R0)

R0 <- R0 + R1